Pokud máte sklony sledovat, co se děje v alternativních procesorových architekturách (což asi nyní znamená vše mimo x86 a ARM), pak jste asi už slyšeli o RISC-V. Jde o architekturu silně tíhnoucí k principům RISC a zároveň uvolněnou stylem open source. Tato instrukční sada může být pro výrobce řipů zcela zdarma a zároveň by ale měla umožňovat implementaci „otevřeného“ hardwaru. Architektura RISC-V nyní učinila důležitý krok na cestě k reálné existenci „v poli“. Firma SiFive začíná s výrobou prvního dospělého 64bitového procesoru používajícího instrukční sadu RISC-V. Má čtyři jádra a na rozdíl od předchozích mikrořadičů už na něm může běžet standardní velký operační systém.

SiFive je startup založený přímo některými z tvůrců architektury RISC-V. Tato firma má stejně jako ARM takový obchodní model, že návrhy svých jader licencuje (na rozdíl od ARMu by to ale mělo být za jednorázový poplatek bez dalších tantiém za prodané výrobky). Její návrh CPU tak v komerční podobě bude muset vyrábět někdo jiný, nicméně samotné SiFive ho nyní ověřilo zkušební sérií. Nechalo na 28nm procesoru vyrobit prototypové čipy používající jeho návrh „Coreplex U54-MC“ a tyto čipy nyní úspěšně prošly tape-outem a údajně snad i běží v laboratoři, včetně úspěšného spuštění Linuxu.

Prototypy budou dostupné zákazníkům implementujícím vlastní CPU nad tímto „IP“, ale SiFive na nich údajně plánuje založit i vlastní vývojové desky, které by údajně měly být dostupné v první čtvrtině roku 2018. Ty by tak mohly být asi první šancí, jak provozovat skutečný plnohodnotný počítač s architekturou RISC-V, a to i pro účely jako vývoj Linuxu bez nutnosti tzv. cross-kompilace na procesorech jiné architektury nebo běhu v emulátoru. Čipy na bázi U54-MC by tak mohly hrát docela důležitou úlohu v rozjezdu této architektury, jež by v budoucnu možná mohla být docela důležitá a rozšířená.

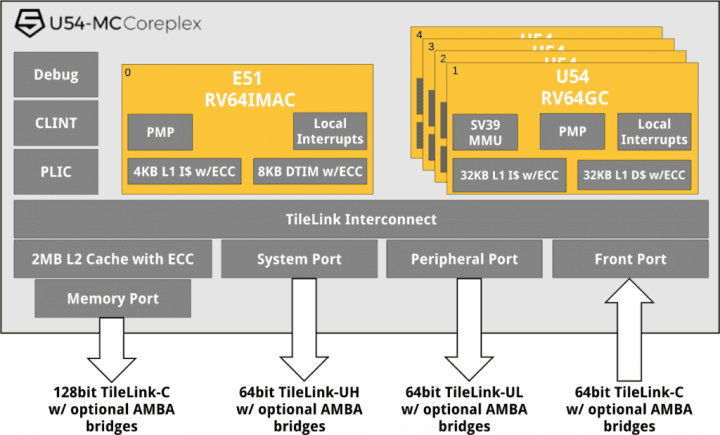

Technické aspekty procesoru U54-MC nejsou nijak oslnivé. I ve srovnání s čipy ARM bude výkon na lowendové úrovni, nicméně tato architektura už má všechny náležitosti pro běh standardního 64bitového OS a nikoliv jen nějakého embedded kódu, zejména MMU pro ochranu paměti. Jde o čtyřjádrový procesor s jádry U54, které vykonávají kód stylem in-order s šířkou 1-issue (jsou tedy stavěné na vykonávání jedné instrukce za takt) a používají pětistupňovou pipeline. Mají L1 cache o velikosti 64 KB (32 KB data, 32 KB instrukce) s ECC a sdílenou 2MB L2 cache. Takt těchto údajně dosahuje 1,5 GHz na zmíněném 28nm procesu a implementují instrukční sadu RV64GC. CPU podporuje virtuální paměť s 38bitovým fyzickým adresováním, což by mělo umožňovat až 256 GB RAM.

Podle SiFive mají jádra U54 na 1 MHz dosahovat výkon asi 1,7 MIPS v benchmarku Dhrystone a 2,75 bodů v CoreMarku. Archtiektura U54 by měla údajně zhruba odpovídat výkonu Cortexu-A35, což je lowendové jádro ARMu. Běžně používané in-order Cortexy-A53 jsou už dual-issue a budou tedy proti těmto čipům o dost rychlejší.

Čip SiFive, který by se asi měl nacházet ve zmiňovaných vývojových deskách, má k čtyřem hlavním jádrům mít ještě menší jádro U51 (4KB L1 cache pro instrukce s ECC, 8KB paměť pro data, bez FPU, instrukční sada RV64IMAC), které bude sloužit jako řídící jednotka. Všechna jádra komunikují po koherentní propojovací logice TileLink. Na sběrnici TileLink se bude nacházet řadič paměti DDR3 nebo DDR4 (zřejmě dvoukanálový) a bude na ni možné navěsit ostatní periférie a systémová rozhraní jako konektivitu USB, SATA, PCI Express 3.0 nebo Ethernet.

Kromě plánu na výrobu vlastní vývojářské desky má SiFive pro architekturu RISC-V a na ní založené IP údajně slušné množství zákazníků. Je mezi nimi oficiálně Arduino a Microsemi, ovšem kromě nich údajně firma získala větší množství dalších licencujících klientů (v oborech nositelné elektroniky a v řadičích pro úložiště, tedy v embedded sféře, ale také pro vojenské aplikace, set-top boxy a datacentrové čipy). Architekturu RISC-V prý zvažují i pro různé účely i velcí výrobci čipů, ovšem nic bližšího prozrazeno nebylo.

Kromě plánu na výrobu vlastní vývojářské desky má SiFive pro architekturu RISC-V a na ní založené IP údajně slušné množství zákazníků. Je mezi nimi oficiálně Arduino a Microsemi, ovšem kromě nich údajně firma získala větší množství dalších licencujících klientů (v oborech nositelné elektroniky a v řadičích pro úložiště, tedy v embedded sféře, ale také pro vojenské aplikace, set-top boxy a datacentrové čipy). Architekturu RISC-V prý zvažují i pro různé účely i velcí výrobci čipů, ovšem nic bližšího prozrazeno nebylo.