Uniklé dokumenty: Zen 3 mohl mít plánované čtyřcestné SMT

Ona chybějící opora pro spekulace o SMT4 (či „4-way SMT“) se totiž teď objevila. Asijský leaker Momomo_us, který bývá poměrně spolehlivý, získal a publikoval kousky dokumentů pocházejících zřejmě z nějakých prezentace Gigabyte (tato firma se věnuje i serverům) a AMD, týkající roadmapy procesorů Epyc. Zde je podstatné říci, že jde asi o dokument někdy z konce roku 2018 (Q4 2018). Tehdy ještě nebyly vydané 7nm Epycy Rome a následující třetí a čtvrtá generace Milan a Genoa, o nichž dokument hovoří, asi nebyly ještě vůbec hotové co do architektury a funkcí. Od té tedy specifikace mohly změnit a podle všeho i v některých věcech změnily. To mějte při následujícím čtení na paměti (a pamatujte i na to, že tento únik přeci jen může být fake). Vypadá to, že předtím, než ho Momomo_us našel, unikla celá verze slajdu na čínském internetu (druhá část pochází z interní serverové roadmapy divize AMD China datované 4Q18, viděli jsme ji i neořezanou).

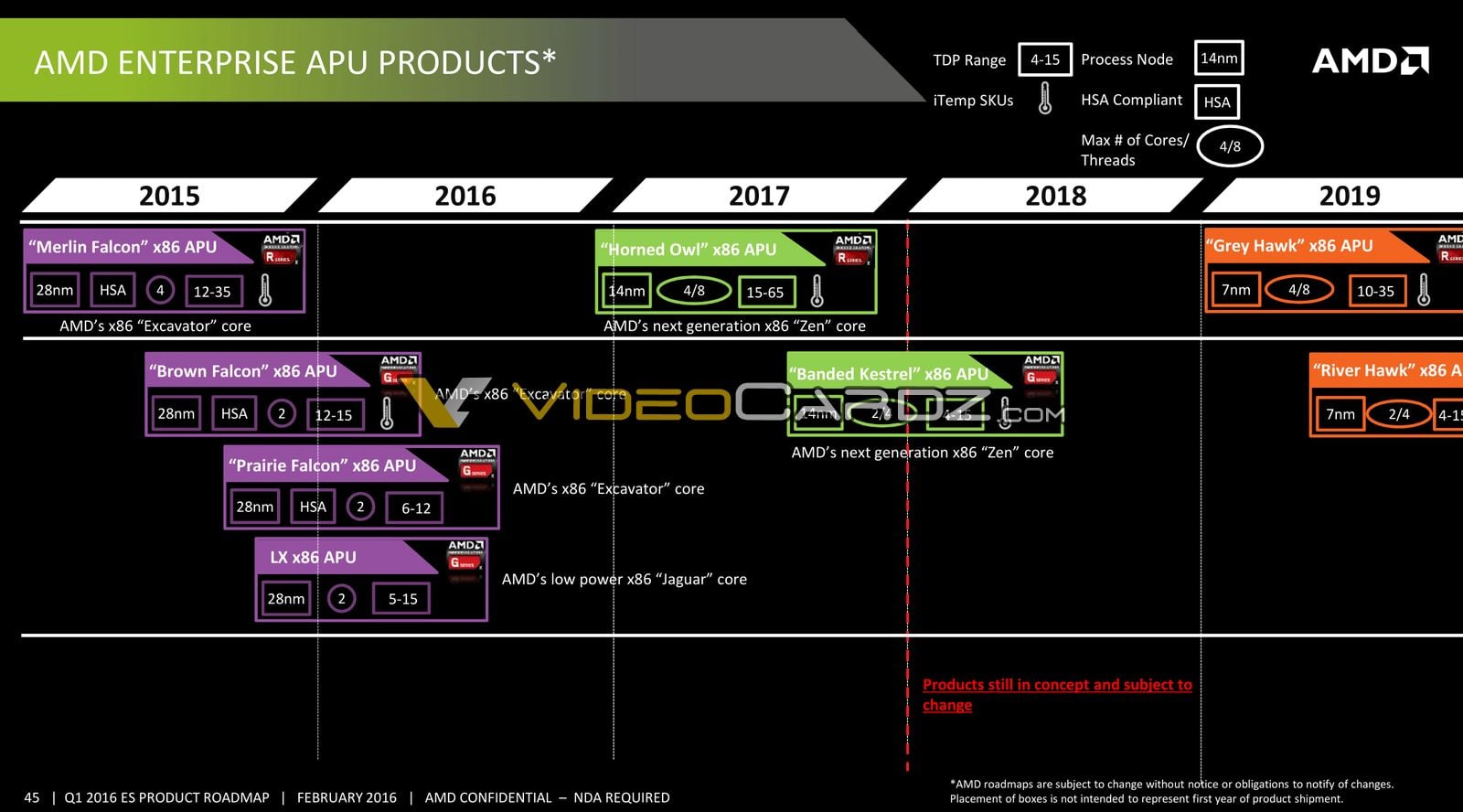

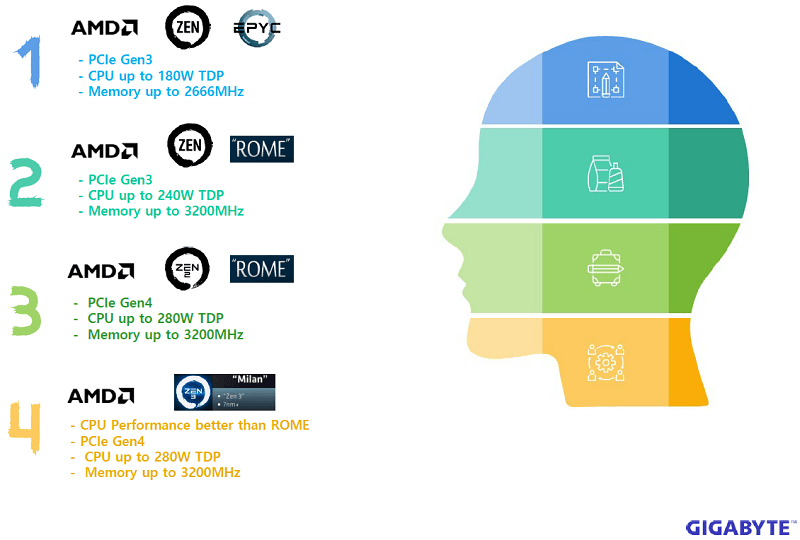

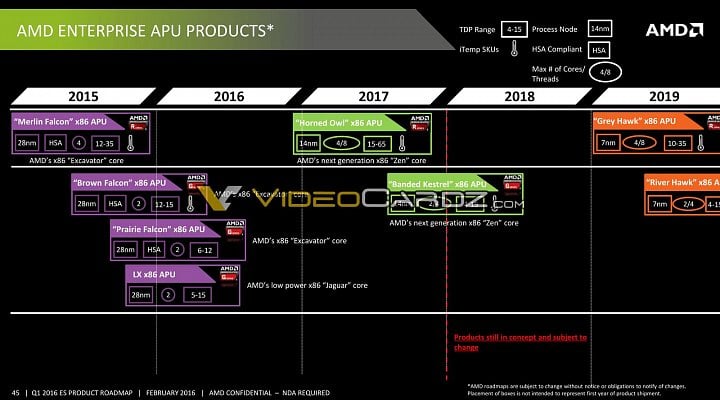

První slajd nám toho ještě moc neukazuje, tedy až na to, že jde asi opravdu o starý dokument. Tváří se totiž tak, jako by generace „Rome“ byla ve skutečnosti dvěma generacemi – druhá generace Epyců by podle této alternativní historie měla mít ještě jádra Zen a jen PCI Express 3.0, ale už 240W TDP – napadá mě, zda třeba nešlo o původně plánovanou 48jádrovou verzi Epyců Rome (která možná neměla používat IO čiplet, ale jen čtyři symetrické 12jádrové čipy po vzoru první generace Naples). Až třetí generace Epycu (ale stále „Rome“) měla údajně přinést Zen 2 a PCI Express 4.0 – toto jsou tedy asi procesory, které AMD nakonec skutečně jako Rome uvedlo. Jako čtvrtou generaci tento slajd uvádí Milan s jádry Zen 3 a „lepším výkonem CPU“, což ale nyní je plánováno jako třetí generace.

Milan a Genoa, jak byly plánovány před 2+ lety?

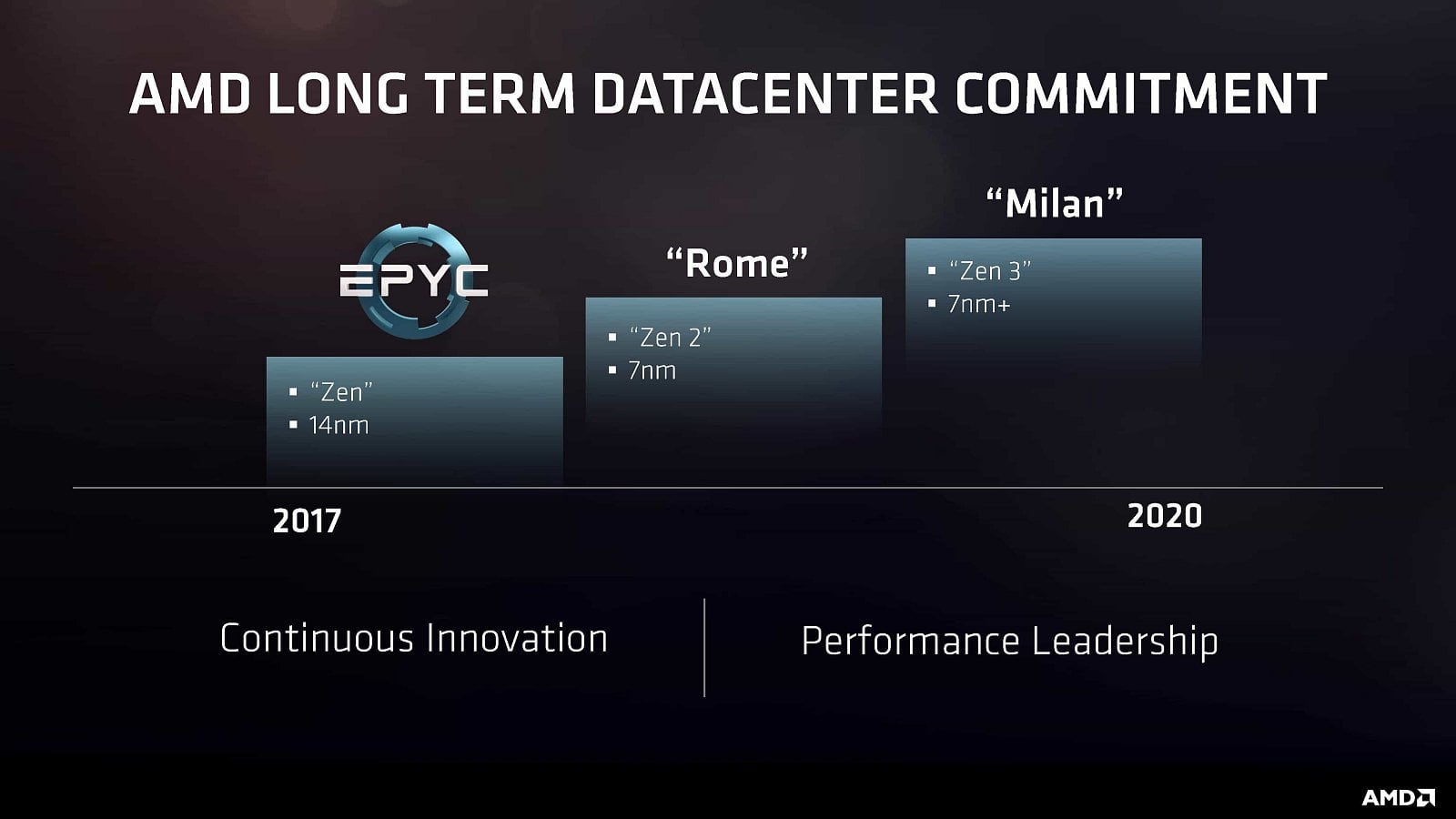

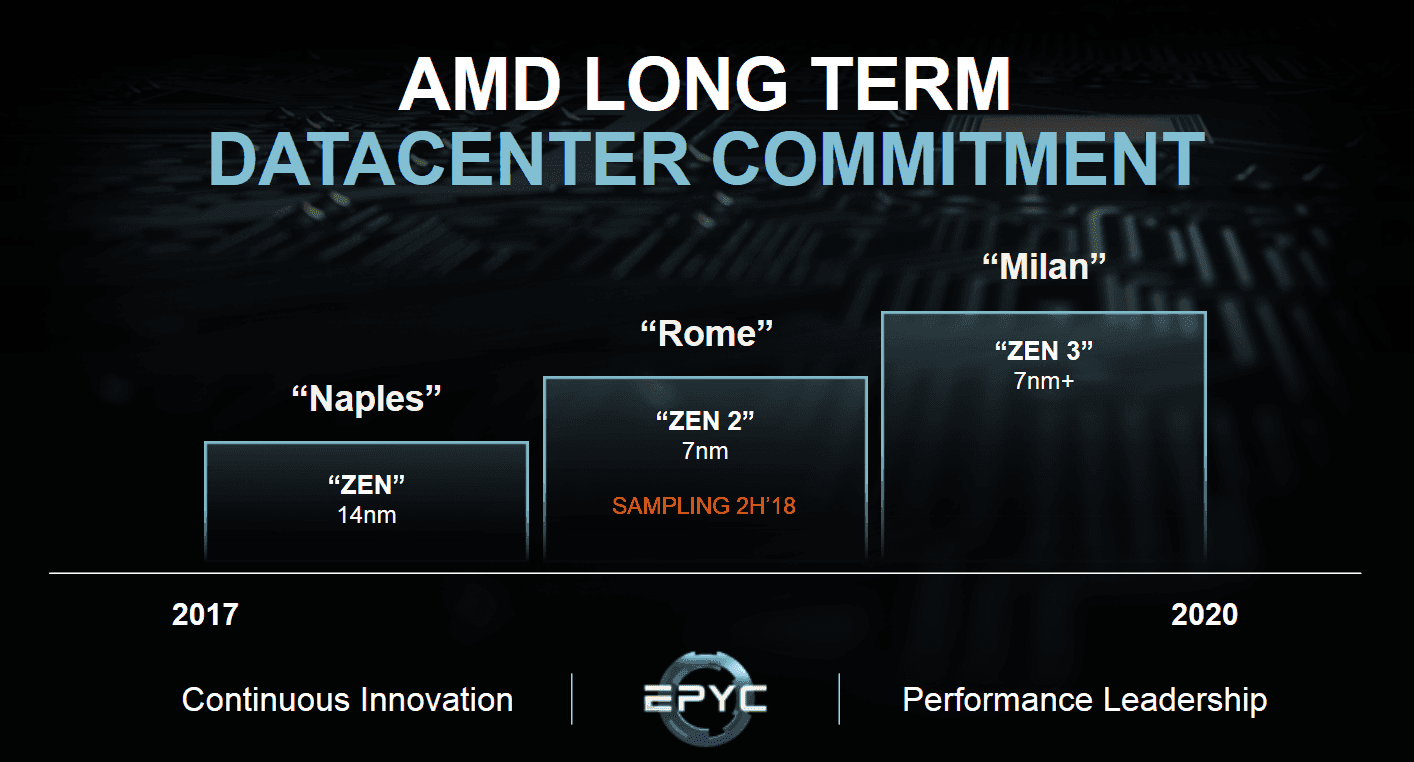

S tím můžeme přejít k druhému slajdu či útržku, který je z roadmapy AMD – stylem připomíná tuto z loňského léta, která by ale měla být aktuálnější. Vidíme, že už tehdy se plánovala podpora jen pro PCIe 4.0 a DDR4 a 64 jader. Ovšem všimněte si poznámky „2X*“. Ve zmíněné loňské roadmapě toto udávalo, kolik vláken navíc poskytuje SMT (tedy zde klasicky dvě vlákna na jádro). Ovšem co hvězdička? Poznámku, kterou toto indikuje, bohužel nevidíme. Mohlo by to tedy znamenat, že některé modely Milanu měly mít zapnuté SMT4 a jiné ne. Anebo měly některé modely mít SMT vypnuté úplně (takže by byly „1X“). Podstatné je, že v novější roadmapě už toto není, u Milanu/Zen 3 bylo loni pouze „2X“, tedy dvouvláknové SMT na jednom jádře.

Roadmapa CPU Epyc podle AMD China, Q4 2018. V té době ještě procesory Genoa byly v tzv. definition phase, ještě nebylo rozhodnuto o tom, jak bude finální architektura vypadat, Milan měl před tapeoutem, který roadmapa kladla až na Q1 2019 (Zdroj: Taobao via Momomo_us)

Roadmapa CPU Epyc podle AMD China, Q4 2018. V té době ještě procesory Genoa byly v tzv. definition phase, ještě nebylo rozhodnuto o tom, jak bude finální architektura vypadat, Milan měl před tapeoutem, který roadmapa kladla až na Q1 2019 (Zdroj: Taobao via Momomo_us)Jenže pak je ve staré roadmapě další fáze „Genoa“, kterou momentálně AMD plánuje vydat snad někdy do roku 2022 jako čtvrtou generaci Epyců a potvrdilo, že má obsahovat jádra Zen 4. Jenže pokud je tento únik legitimní a ne fake (to se nedá zaručit, ačkoliv Momomo_us mu důvěřuje), tak Zen 4 v Genoa je až výsledkem nějakého pozdějšího redefinování. Podle tohoto staršího materiálu měla generace Genoa umět zase 2× rychlejší PCI Express 5.0, podporu pamětí DDR5 a také nevolatilních RAM modulů NVDIMM-P, nový socket SP5 a také podporu koherentního I/O Gen-Z. Evidentně by tedy měla nový I/O čiplet, kde se všechna logika pro tyto funkce nachází. Ale jádra CPU měla údajně ještě pořád mít architekturu Zen 3, tedy stejnou jako Milan. Toto už jak víme neplatí.

Nicméně roadmapa uvádí, že jádra Zen3 v procesorech Genoa už neměla mít SMT „2X*“, ale „4X“. Čili, podle tohoto dokumentu skutečně mělo jádro Zen 3 mít připravovaný SMT4. Tím pádem asi i ono „2X*“ u Milanu mohlo opravdu znamenat podporu SMT4 – jen byla buď naplánovaná jen pro omezené množství modelů, nebo ještě o ní nebylo rozhodnuto. Možná si AMD nechávalo otevřená vrátka pro zapnutí nebo vypnutí SMT4 podle toho, jestli se podaří funkci včas bezchybně odladit a ověřit, a ona hvězdička znamenala, že SMT4 může být, ale nemusí, podle toho, zda bude v tuto novinku už důvěra, nebo ne a/nebo se najdou chyby/problémy (změna z 2X* na 2X u novější roadmapy může znamenat, že došlo na druhou možnost). A u Genoa se možná už počítalo s tím, že tato revize případné chyby vyřeší.

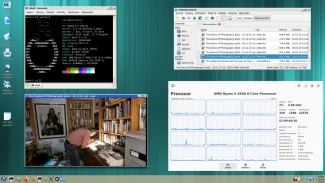

Roadmapa AMD s procesory Epyc 7003 Milan s architekturou Zen 3, kterou firma publikovala v září 2019. Vlastnosti procesorů Genoa tehdy AMD ponechalo v tajnosti. Všimněte si, že zde legenda říká, že 2X znamená dvoucestné SMT

Roadmapa AMD s procesory Epyc 7003 Milan s architekturou Zen 3, kterou firma publikovala v září 2019. Vlastnosti procesorů Genoa tehdy AMD ponechalo v tajnosti. Všimněte si, že zde legenda říká, že 2X znamená dvoucestné SMTJestli ale něco z tohoto nadále platí, to teď opravdu nevíme. Pokud mezitím uběhly dva roky a Zen 3 je sice už po tape-outu, ale pořád několik měsíců vzdálený, pak klidně mohlo být od úmyslu implementovat SMT4 ustoupeno a v Zenu 3 nikdy nebude. Nebo může křemík pro tuto funkci v čipech být, ale nikdy nebude aktivována. A u Zenu 4 také nevíme. Pokud AMD pořád SMT4 považuje za užitečné, mohla by se tato funkce do něj dostat, ale mimo firmu a úzký okruh zasvěcených to asi teď nikdo neví (i když leckdo se tak může tvářit). Nicméně teď může být vhodný čas SMT4 opět začít zvažovat při spekulacích o tom, jak bude architektura Zen 4 vypadat.

Roadmapa serverových procesorů AMD z letošního března. Pro procesory Genoa už je uvedeno jádro Zen 4 (AMD Financial Analyst Day 2020)

Roadmapa serverových procesorů AMD z letošního března. Pro procesory Genoa už je uvedeno jádro Zen 4 (AMD Financial Analyst Day 2020)Co by SMT4 znamenalo?

Bylo by SMT4 přínost, pokud by se potvrdilo? Potenciálem, který nabízí, je vyšší celkový výkon při využití všech vláken. Jenže je třeba počítat s tím, že aplikace musí být zároveň schopná se rozložit do nyní dvojnásobného počtu paralelních vláken, což zrovna u typického spotřebitelského softwaru moc rozšířené nemusí být. Navíc třetí a čtvrté vlákno bude mít pravděpodobně menší přínos než to druhé přidané SMT2, protože zde vládne zákon klesajícího užitku.

Tipněte si: Bude mít architektura AMD Zen 4 čtyřcestné SMT (čtyři vlákna na jádro)?

Z tohoto důvodu se obvykle soudí, že uplatnění by SMT4 mělo asi téměř výhradně v serverech, takže i v případě jeho potvrzení pro Epycy Genoa by u odvozených Ryzenů 5000 nebo 6000 mohla tato novinka zůstat vypnutá. Mimochodem, je dobré si také připomenout, že při vytížení všech virtuálních vláken se výkon výpočetních prostředků jádra rozdělí mezi ně. To ale znamená, že zatímco u SMT2 můžete dostat třeba 60–70% jednovláknového výkonu na dvou jádrech, zde byste najednou měli na každém vlákně už jenom třeba 40–50 % jednovláknové rychlosti, byť celkový výkon by byl lepší. Desktopové operační systémy a třeba hry by to nemusely rády vidět.

Zdroje: 188号/Twitter (1, 2, 3), Imgur (1, 2)