Během Computexu 2017 se toho hodně seběhlo, například kolem nové highendové platformy procesorů Intel Skylake-X. Novinky do tohoto návalu zpráv oznámil ale také jeden z velkých současných protivníků Intelu: britský ARM. Ten nevyrábí vlastní CPU, místo toho licencuje instrukční sadu a připravená jádra dalším firmám – skrze kterýžto model se tato architektura dostala do miliard zařízení a prakticky kompletně ovládla mobilní sféru. Během Computexu ARM předvedl nejnovější zbraně: procesorová jádra Cortex-A75 a Cortex-A55, která budou pohánět příští generace mobilů a tabletů a měla by jim zase přinést lepší výkon a energetickou efektivitu.

Cortex-A75: 3-issue evoluce jádra A73

Jádro Cortex-A75 má být novým výkonnostním tahounem firmy, nahrazujícím jádro A73, vydané před rokem. Novinka by měla stavět na stejném základě, ale má mít vyšší výkon a nové funkce, včetně podpory novější verze instrukční sady, ARMv8.2. Přidané by v ní měly být například nějaké operace s 8bitovými celočíselnými hodnotami a také podpora výpočtů s hodnotami FP16, obojí potenciálně užitečné pro strojové učení.

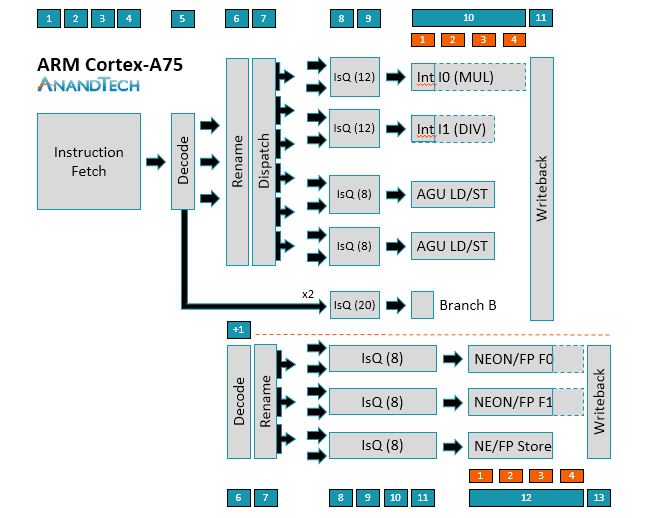

Cortex-A75 má nadále jen dvě ALU a dvě AGU, ale frontend byl rozšířen na dekódování tří instrukcí z takt (3-issue). Pipeline má 11 až 13 stupňů. Přidání třetí ALU pipeline bylo také zvažováno, ale údajně mělo jen omezený efekt. ALU a AGU už ale nejsou spřažené do společných front, každá jednotka má nyní vlastní, což by mělo posílit možnost out-of-order logiky přiřazovat optimálně instrukce volným jednotkám. Také jednotky FPU/Neon zůstala na dvou výpočetních pipeline, ale přibyla třetí specializovaná na load/store – tyto operace tedy už nebudou zabírat dvě hlavní pipeline.

Jádro A75 přebírá hlavní prediktor větvení z Cortexu-A73, nicméně vylepšuje pomocné předběžné prediktory, takže celkově by tento aspekt také měl zaznamenat zdokonalení. Vylepšen byl také prefetch, ale zejména paměti cache. L2 cache se ze sdílené mezipaměti mimo jádro stane jeho integrální součástí, privátní pro každé jádro, a také poběží na plné frekvenci. Proti dnešnímu stavu, kde je až částí celého klastru jader, má její latence údajně být zredukována o 50 %. Roli posledního stupně mezipaměti převezme nově přidaná L3 cache. L2 cache může mít kapacitu 256 KB nebo 512 KB a vůči L1 je neinkluzivní, což šetří kapacitu.

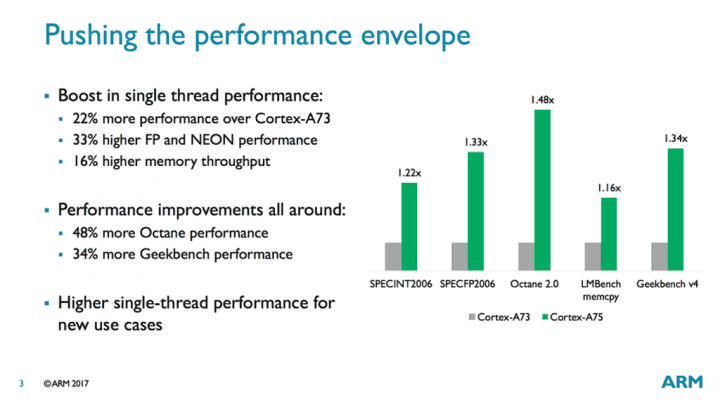

Cortex-A75 by měl proti Cortexu-A73 na stejné spotřebě podávat lepší výkon, údajně až o 30 %. Podobně vysoké mají být i procentuální nárůsty v některých testech (například Geekbench). Jde ale samozřejmě o marketingové sliby, jak výrazně lepší bude reálný výkon, ukáží až testy.

Cortex-A55: konečně nové jádro pro levné čipy

Cortex-A55: konečně nové jádro pro levné čipy

Možná ještě podstatnější než nahrazení Cortexu-A73 jádrem A75 je ale nové jádro Cortex-A55. To totiž po dlouhé době přináší upgrade levnější a méně výkoné, ale také úspornější větvi architektur, která ARM navrhuje pro roli „little“ jader. V levnějších SoC jsou používané i jako hlavní architektura. Cortex-A53 byl vůbec prvním 64bitovým jádrem tohoto typu a od dejme tomu roku 2014 nedostal na rozdíl od Cortexu-A57 žádného následníka. Vylepšení tedy už bylo třeba.

Cortex-A55 celkovou koncepcí odpovídá předchůdci. Jde stále o in-order jádro (tedy zpracovávající instrukce v originálním pořadí, bez Out-of-Order optimalizace), stavěné na zpracování dvou instrukcí za takt – jádro je stále dual-issue – a krátké pipeline s jen osmi stupni (či deseti pro instrukce Neon a FPU), což znamená nižší frekvence. ARM jeho výkon slibuje zvýšit vylepšeným paměťovým subsystémem, podobným tomu u jádra A75. L2 cache se místo sdílené mezipaměti mimo jádra i zde stane integrální součástí (i u A55 by měla být o 50% snížena latence), a taktéž bude přidaná sdílená L3 cache. L1 instrukční cache mají v jádru A55 čtyřcestnou asociativitu místo jen dvoucestné v A53. Datová L1 už byla čtyřcesteně asociativní předtím. Kapacita obou je konfigurovatelná, lze mít 16, 32 i 64 KB. Lepší by měly být i jejich TLB (to by mělo platit i pro L2 cache).

Paměťový výkon má stoupnout citelně a výsledky v softwaru jako je SPECint/SPECfp 2006 jsou údajně o 18–38 % vyšší. Tato zlepšení výkonu ale mírně zhoršila spotřebu jádra (údajně asi o 3 %). Po stránkách hrubého výkonu by se příliš měnit nebylo, a tak se budou zlepšení asi hodně měnit podle běžícího kódu. Lepší paměťový subsystém by ale měl obecně zlepšovat výkon jádra. In-order architektura je totiž citlivá na včasný přísun dat z paměti, jehož latenci neumí „schovávat“ jako out-of-order jádro.

Jádro má i některé změny ve výpočetní části. Místo jedné jednotky AGU jak pro čtení, tak pro zápis do paměti bude mít A55 oddělenou jednotku pro load i store. Tyto operace tedy bude možné provést v jednom cyklu paralelně. Vylepšeno by mělo být předpovídání výsledků větvení a rovněž prefetch, který má mít vyšší propustnost.

Jádro Cortex-A55 má také být robustnější, například podporovat rozšíření VHE (Virtual Host Extensions) a různá vylepšení RAS. Přidaná je tak ochrana dat paritou a ECC ve všech mezipamětech. Také toto jádro bude mít instrukční sadu ARMv8.2 s novými instrukcemi nad datovými typy INT8 a FP16, jako Cortex-A75. Instrukce FMA by také měly být prováděny jedním průchodem, takž se jejich latence zlepší z 8 na 4 cyklů.

ARM DynamIQ

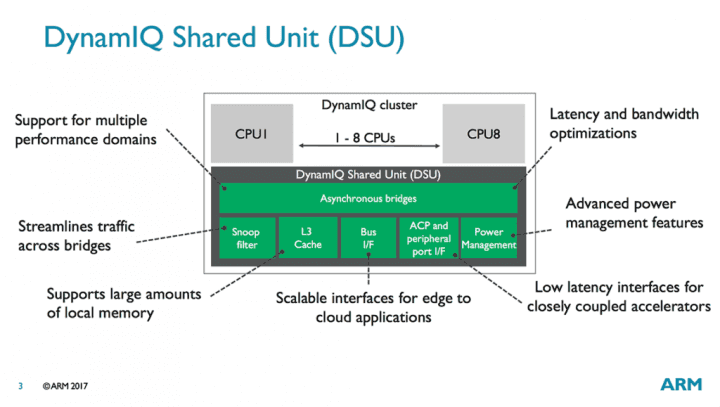

Obě tato jádra jsou navržena ve spojení s novou propojovací logikou, která je bude ve výsledném procesoru vázat dohromady. Ta se jmenuje DynamIQ a jde náhradou (ale zároveň evolucí) konceptu big-LITTLE. Nová logika je ale pružnější. Big.LITTLE čipy musely v každém klastru jader mít stejný typ jader, kdežto DynamIQ umožní jádra míchat v rámci jednoho klastru – ARM hovoří například o možnosti mít čip s sedmi Cortexy A55 a jedním A75 pro jednovláknové úlohy. S touto pružností souvisí i přechod na privátní L2 Cache a přidání L3 coby poslední úrovně hierarchie pamětí cache. Zároveň nyní bude možné mít v jednom klastru se sdílenou L3 až osm jader místo jen čtyř – běžné mobilní SoC by tudíž mohly být jednoklastrové. Klastrů může být v procesoru až 32, takže teoreticky lze na této technologii možné vytvořit SoC s až 128 jádry.

DynamIQ má také zlepšovat spotřebu čipu, jelikož podporuje škálování napětí a frekvence pro jednotlivá jádra v klastru, zatímco dříve se měnily najednou pro celou skupinu. V praxi ale přepínání bude fungovat v doménách, v nichž se může ocitat jader více než jedno, jelikož domény navíc prodražují desku a napájecí obvody.

DynamIQ má také zlepšovat spotřebu čipu, jelikož podporuje škálování napětí a frekvence pro jednotlivá jádra v klastru, zatímco dříve se měnily najednou pro celou skupinu. V praxi ale přepínání bude fungovat v doménách, v nichž se může ocitat jader více než jedno, jelikož domény navíc prodražují desku a napájecí obvody.

Každý klastr bude řízen jednotkou DSU (DynamIQ Shared Unit), která řídí spotřebu přímo v hardwaru. To umožňuje rychlejší a efektivnější změny frekvence proti softwarovému řízení. DSU také spravuje komunikaci mezi jádry, která probíhá koherentní propojovací logikou CCI, CCN nebo CMN i s integrovaným snoop filtrem. S DSU by také měly být spojena L3 cache klastru, která je konfigurovatelá, může mít 1, 2 nebo 4 MB, případně ji lze zcela vypustit. L3 má 16cestnou asociativitu a je více méně exkluzivní.

Každý klastr bude řízen jednotkou DSU (DynamIQ Shared Unit), která řídí spotřebu přímo v hardwaru. To umožňuje rychlejší a efektivnější změny frekvence proti softwarovému řízení. DSU také spravuje komunikaci mezi jádry, která probíhá koherentní propojovací logikou CCI, CCN nebo CMN i s integrovaným snoop filtrem. S DSU by také měly být spojena L3 cache klastru, která je konfigurovatelá, může mít 1, 2 nebo 4 MB, případně ji lze zcela vypustit. L3 má 16cestnou asociativitu a je více méně exkluzivní.

A75 a A55 během roku 2018

První čipy s touto technologií lze asi čekat někdy v prvním kvartále příštího roku (Q1 2018) – tedy u hráčů agresivně přecházejících na nové generaci technologií ARMu. Totéž by mělo asi platit také pro mobilní čipy založené na Cortexu A75 a A55, i když asi nelze vyloučit nějaké hodně rychlé vlaštovky třeba už před Vánoci.