AMD tento měsíc poprvé odhalilo 7nm procesory a jejich architekturu Zen 2. Potvrdily se dřívější zvěsti o 64 jádrech v serverových CPU Epyc, ale AMD přirozeně ještě zatajilo, jaké by mohly mít frekvence. A také stále nebylo jasné, zda architektura stále bude používat členění jader do bloků CCX po čtyřech, nebo zda se něco na propojení změní. Teď to ovšem vypadá, že na tyto otázky máme odpověď.

První vzorek Zenu 2 venku

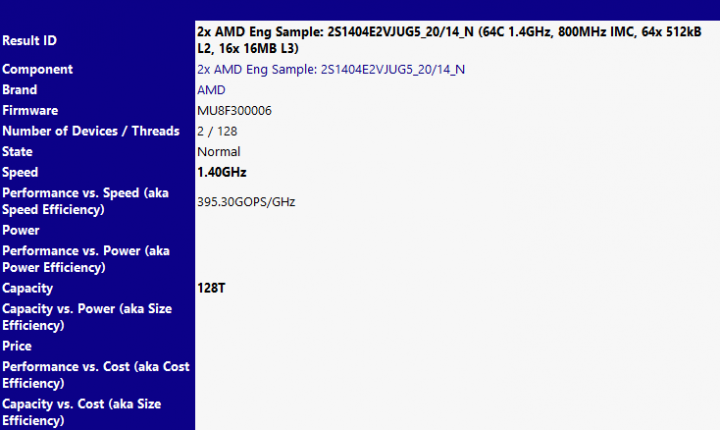

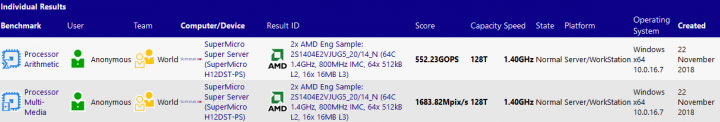

Na internet se totiž zdá se dostalo záznam z testování inženýrského vzorku (ES) 7nm procesoru Rome, tedy Epycu druhé generace, který má mít oněch až 64 jader v celkem devíti čipech. Mělo by jít o vůbec první ES 7nm procesoru AMD, o kterém se dozvídáme. Kód jeho označení zní 2S1404E2VJUGS_20/14_N. Už z tohoto řetězce by se dá vyčíst něco o parametrech, protože sémantika značení ES procesorů u AMD je známá. Ovšem CPU bylo nalezeno v databázi SiSoft Sandra, což nám dává ještě nějaké informace navíc.

Procesor 2S1404E2VJUGS_20/14_N má podle všeho skutečně 64 jader. Sandra nicméně ukazuje jen 128 vláken, ačkoliv vzorky podle ní byly testovány v páru (v desce Supermicro H12DST-PS). Asi tedy nebylo aktivní SMT, ale finální verze Zenu 2 by měla mít dvě vlákna na jádro. Z označení pak lze vyčíst frekvence, které dokládá i Sandra. Tento vzorek 64jádra má základní takt 1,4 GHz v základu a zřejmě 2,0 GHz pro turbo. Takto nízká základní frekvence není výjimečná, první vzorky 14nm Epycu měly základ 1,45 GHz. Nicméně turbo tehdy bylo 2,9 GHz, proti čemuž je uváděných 2,0 GHz u 7nm čipu dost nízké. Jde ale koneckonců o ES, tedy vzorek, jehož parametry neodpovídají finálním parametrům.

Finální takty Epycu budou o dost výš

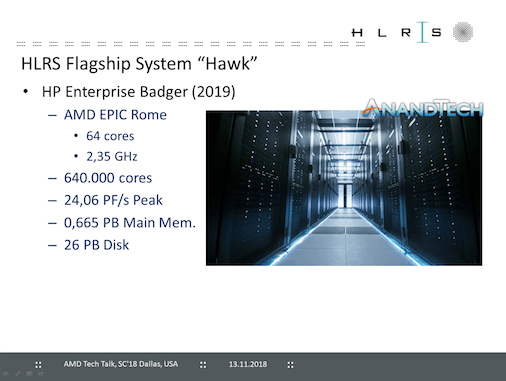

Zde je zajímavé, že z jiného zdroje máme zdá se informaci o tom, jaké takty AMD očekává pro hotový výrobek. Nedávno se totiž objevila informace, že AMD bude dodávat procesory do superpočítače Hawk pro institut HLR Stuttgart. Použité v něm mají být právě Epycy druhé generace „Rome“, což je potvrzeno v oficiálních prezentacích. V těch stojí, že budou použité 64jádrové procesory (celkem má stroj obsahovat 640 000 jader, tedy 10 000 CPU). Přímo ve slajdech stálo, že frekvence použitých modelů má být 2,35 GHz. Pravděpodobně by mohlo jít o jejich základní frekvenci, i když teoreticky by asi řeč mohla být i o all-core boostu. Každopádně je to ale vyšší frekvence, než má tento nízko taktovaný ES vzorek. Epyc 7601, nejvýkonnější 32jádro 14nm generace Naples, má mimochodem základní frekvenci 2,2 GHz.

Sandra ještě o vzorku sděluje, že každé jádro Zen 2 obsahuje 512 KB L2 cache, což by bylo stejné jako u Zenu 1, a uncore/Infinity Fabric zdá se mohla běžet na 800 MHz. To by implikovalo, že paměti běžely jen jako DDR4-1600. Pokud tedy Zen 2 neumí používat nějaké jiné poměry frekvencí DDR4 a Infinity Fabric než Zen 1.

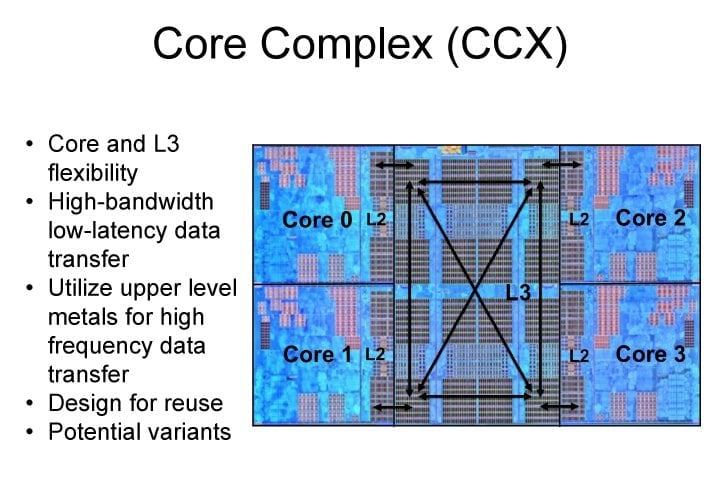

Zen 2 zřejmě stále používá čtyřjádrové bloky CCX

Asi nejzajímavější část ale je údaj o L3 cache. Proč? Sandra ukazuje 16×16 MB L3. To znamená, že by mezipaměť třetí úrovně byla rozdělená na bloky jako u Zenu 1. Pokud je těchto bloků 16, znamená to zřejmě, že L3 cache je sdílena vždy blokem čtyř jader, přičemž další čtyři jádra mají opět ve čtveřici vlastních 16 MB a tyto kapacity nejsou spojené. Zen 2 tedy podle všeho opět používá jako stavební blok čtyřjádrový Core Complex (CCX), stejně jako Zen 1.

Každý z osmi čipů (respektive chipletů) je tedy asi interně tvořen dvěma CCX po čtyřech jádrech. Oba CCX budou mít svých 16 MB L3 cache a tyto dvě poloviny budou stejně jako na 14nm či 12nm čipu Zeppelin/Summit Ridge v dnešních Ryzenech a Epycích propojené pomocí Infinity Fabric. Při komunikaci jader mezi dvěma různými CCX tedy stále asi nastane vyšší latence/nižší propustnost, jako dnes.

Toto tedy zřejmě vyvrací spekulace o tom, že by CCX v architektuře Zen 2 nově mohl mít šest nebo osm jader místo čtyř (a že by tedy ony 7nm čiplety v Epycu Rome třeba mohly být monolitické a L3 cache v nich by mohla být sdílena všemi osmi jádry). Proč to AMD neudělalo? Patrně jednak kvůli zjednodušení návrhu, čtyřjádrový CCX lze jako celek vzít a snadno zkopírovat do mnoha jiných čipů – třeba APU nebo semi-custom procesoru (na základě toho je pravděpodobné, že čtyřjádrový CCX převezmou i procesory Ryzen).

Mnohajádrové CCX by byly náročné na propojení

Kromě toho je zde ale asi i otázka komunikace uvnitř CCX. Jádro v čtyřjádrovém CCX architektury Zen 1 má přímé propojení s každým z ostatních tří sousedů. Při zapojení čtyř jader tímto způsobem je třeba celkem jen šest linek mezi nimi. Ovšem s vyšším počtem uzlů komplexita tohoto druhu propojení velmi rychle roste – s šesti jádry byste potřebovali linek patnáct, pro osm jader 28 (každé jádro komunikuje se sedmi sousedy, to celé děleno dvěma). Tento interconnect tedy jednoduše řečeno neškáluje dobře na víc jak čtyři jádra, komplexita propojení by byla vysoká, stejně jako asi zabraná plocha na čipu a spotřeba. Je tedy mnohem jednodušší a asi také efektivnější, pokud blok CCX zůstane čtyřjádrový a těchto CCX se jednoduše použije více, přičemž jejich propojení obstará logika Infinity Fabric.

Devět čipů pod kapotou Epycu Rome. Osm malých je 7nm s jádry CPU, centrální I/O čip je 14nm a obsahuje vše ostatní včetně řadiče pamětí (Zdroj: Twitter)

Devět čipů pod kapotou Epycu Rome. Osm malých je 7nm s jádry CPU, centrální I/O čip je 14nm a obsahuje vše ostatní včetně řadiče pamětí (Zdroj: Twitter)V tuto chvíli je ovšem dost předčasné z tohoto faktu vyvozovat nějaké závěry o výkonu a kvalitě celé architektury. Čtyřjádrové CCX a tím i L3 cache rozdělené do bloků sdílených jen čtyřmi jádry představuje jen jeden z implementačních detailů. Jak dopadnou finální procesory postavené na této koncepci, to se dozvíme až z podrobnějších testů. A nejspíš až po uvedení, když bude možné podrobně analyzovat výkon Zenu 2 v různých situacích.