Minulý týden měli posvícení fanoušci AMD – ale v širším smyslu i všichni zájemci o problematiku procesorů, protože firma poprvé prozradila něco o tom, co přinese architektura Zen 2, kterou příští rok vydá na 7nm procesu. To, co bylo o jádru Zen 2 (a o 64jádrových serverových procesorech Epyc na něm založených) řečeno, jsme už probírali v tomto článku. Mezitím se vynořilo ještě několik dalších věcí, které potřebují komentář. Tento článek bude tedy cosi jako volné pokračování. Po hlavní prezentaci, o které jsme referovali minule, se ještě něco nového objevilo v rozhovoru s Markem Papermasterem (CTO firmy AMD) který publikoval AnandTech. Najdete ho zde, pokud ho chcete vidět celý, bohužel však v této fázi firma nechce říct nic navíc, takže moc výživného toho v něm nenajdete. Něco se z něj ale přece jen podařilo vypáčit.

Lepší latence v serverových CPU

V rozhovoru Papermaster řekl, že Zen 2 a modulární architektura Epycu druhé generace zlepší přístupové doby do operační paměti (latence), které jsou u Zenů 1 poměrně vysoké (což je špatně). Ve srovnání s první generací MCM Epycu by zřejmě latence měla v průměru být nižší. Toto ovšem neznamená, že by vícečipové řešení mohlo mít nižší latenci, než je mezi jádrem a pamětí připojenou na řadič přítomný přímo ve stejném křemíku (jak je to u Ryzenů v platformě AM4 nebo při přístupu do lokální části paměti u dnešního Threadripperu či Epycu). Serverový Zen 2 bude tedy asi mít v průměru lepší latence a nejhorší případ by mohl být rychlejší, ale nejlepší případ se zase stane o něco pomalejším, protože žádná část RAM už nebude dostupná přes řadič přítomný na stejném kusu křemíku. Chování ale nyní bude uniformní a předvídatelné, protože odpadne rozdíl mezi oním nejhorším a nejlepším případem. To by někdy také mohlo být plus.

Zde ovšem pozor na to, že je řeč o serverové MCM verzi. Zda se tato zlepšení latence přetaví i do Ryzenů pro PC a notebooky, zatím nelze říct. AMD nicméně prý chce v každé generaci zlepšovat konektivitu Infinity Fabric, která v procesorech vše propojuje, takže nezbývá než doufat, že nějaké její pokroky se projeví i v Ryzenu.

Zen 2 prý při AVX2 nebude snižovat frekvence (nebo ne moc…)

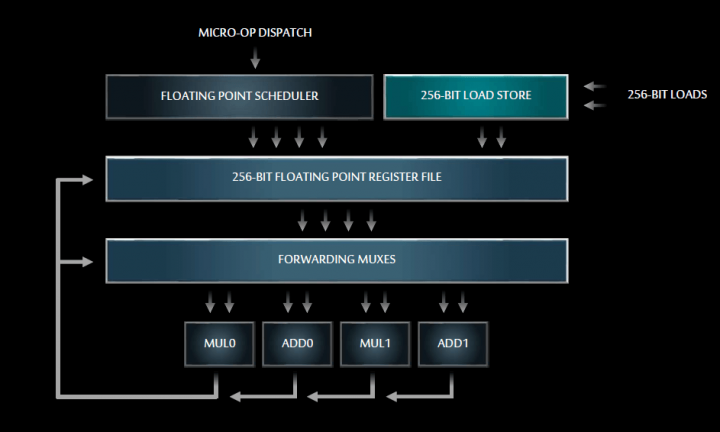

Co je dále zajímavé, je otázka po vlivu 256bitových jednotek FPU na frekvence, která v rozhovoru padla a na rozdíl o dalších věcí ji Papermaster neodmítl komentovat. Jak asi víte, u Intelu alespoň v některých případech procesory mají druhou odlišnou sadu základních a turbo frekvencí pro instrukce AVX/AVX2, protože tyto operace mají vyšší spotřebu. Podle AMD toto u Zenu 2 nemá být aplikováno. Ve specifikacích prý budou jak pro běžný kód, tak pro AVX2 stejné takty.

Ale opět pozor – toto asi neznamená nutně, že Zen 2 nebude mít také pod AVX2 na stejném taktu vyšší spotřebu. Fyzika říká, že by měl mít, širší vektor znamená více uskutečněné práce. V praxi by asi aktivace 256bitových instrukcí stále mohla či možná spíše měla snižovat okamžitou frekvenci čipu. Jen to bude v rámci standardního rozsahu mezi základem a maximálním boostem, jako s každým jiným programem. Zen 2 tedy bude mít například základní takt 3,2 GHz a turbo 3,8 GHz a jak běžné aplikace (nebo s SSE), tak ty s instrukcemi AVX2 se budou pohybovat v tomto rozmezí, místo aby pro SSE byl rozsah frekvencí 3,2–3,8 GHz a pro AVX/AVX2 například jen 3,0–3,5 GHz.

Čiplety, jak by mohl vypadat 7nm Ryzen?

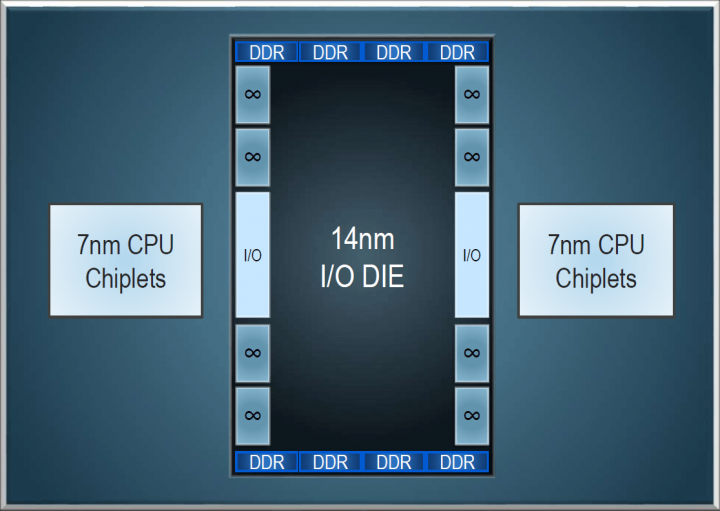

Je také potvrzeno, že čiplety s jádry nemají propojení mezi sebou – napojené jsou vždy jen na centrální IO čiplet. Bohužel zatím neexistuje informace, která by nás nejvíc zajímala, a to zda AMD stejné uspořádání nepoužije i na platformě AM4. Existují asi důvody pro to, aby tak učinila, ale i proti tomu. Pokud by Ryzeny byly také složené z těchto 7nm osmijádrových čipletů a k tomu dalšího 14nm čipu pro IO, znamenalo by to, že firma už nemusí navrhovat další drahý 7nm křemík, jen další levnější na 14 nm. Pokud by AMD šlo touto cestou, mohl by 7nm osmijádrový čiplet možná být použit do třetice i u APU, ale je otázka, zda by třeba MCM řešení nebylo nevýhodné pro jejich použití v noteboocích.

Devět čipů pod kapotou Epycu Rome. Osm malých je 7nm s jádry CPU, centrální I/O čip je 14nm a obsahuje vše ostatní včetně řadiče pamětí (Zdroj: Twitter)

Devět čipů pod kapotou Epycu Rome. Osm malých je 7nm s jádry CPU, centrální I/O čip je 14nm a obsahuje vše ostatní včetně řadiče pamětí (Zdroj: Twitter)Ovšem vícečipové pouzdření by zase o něco zvýšilo náklady na výrobu a také by asi mohlo zhoršovat právě onu velmi důležitou latenci do pamětí. Pro nás uživatele by asi proto bylo lepší, kdyby AMD pro socket AM4 navrhlo zvlášť druhý 7nm čip (a třetí pro APU...). Ten by mohl být uzpůsoben přímo pro desktop a mohl by asi být levnější na výrobu. Ale AMD by zase muselo zainvestovat značné částky do jeho vyvinutí. Osobně si netroufám hádat, které důvody zde převáží.

7nm EUV výroba u Samsungu?

Kromě těchto věcí se objevila ještě jedna drobnost, která možná je, možná není zajímavá. Zdá se, že v jiném rozhovoru s představiteli AMD padla zmínka o potenciální výrobě druhé 7nm („7nm+“) generace (serverových procesorů „Milan“ s jádry Zen 3) v továrnách Samsungu. Kdosi z AMD údajně řekl, že firma sleduje to, jak si Samsung vede a analyzuje možnost výroby na jeho EUV výrobním procesu.

https://twitter.com/dylan522p/status/1061250747256451072

Pokud by AMD od TSMC hned zase přeskočilo do jiných továren, bylo by to docela pozoruhodné, nicméně zde je asi třeba brát vše hodně s rezervou. Toto sdělení totiž dost možná nemělo tvrdit, že je taková změna dodavatele na cestě, ale jen ji nastínit jako čistě teoretickou možnost. Třeba se tímto myslelo jen to, že se této možnosti firma nebrání, pokud by se někdy v budoucnu ukázalo, že je schůdná a přínosná. V nejbližší době ale nic takového asi nemusí nastat.

Zvěsti o 29% zlepšení IPC nejsou realistické

Poslední věc, ne kterou se tu podíváme, bude hodně atraktivní otázka IPC, kde je třeba uvést některé věci na pravou míru. Médii se po prezentaci minulý týden rozšířily bombastické zprávy o tom, že IPC jádra Zen 2 by údajně mohlo být „vyšší o 29 %“ proti první generaci. Ty byly založené na interpretaci poznámky pod čarou přímo z tiskové zprávy, tedy z oficiálního zdroje. AMD v ní udávalo, že v jednom speciálním mikrobenchmarku se IPC skutečně takto zvýšilo, kód označený jako DKERN+RSA má mít IPC 4,53 tam, kde pro Zen 1 vychází jen 3,5. Celé sdělení (poznámka pod čarou č. 1), které tyto diskuse spustilo, zní:

Estimated increase in instructions per cycle (IPC) is based on AMD internal testing for“ Zen 2” across microbenchmarks, measured at 4.53 IPC for DKERN +RSA compared to prior“ Zen 1” generation CPU (measured at 3.5 IPC for DKERN + RSA) using combined floating point and integer benchmarks.

Nicméně klíčové je, že šlo o mikrobenchmark, který evidentně silně těží z 256bitového SIMD. Mikrobenchmarky ale málokdy odpovídají typickému zrychlení v reálném kódu. Testují totiž třeba jen jeden izolovaný aspekt CPU, aniž by se v nich uplatňovala další úzká hrdla výkonu a faktory jako škálovatelnost a Amdahlův zákon. A ty způsobují, že v celé regulérní aplikaci je pak výkon téměř vždy nižší. Lze asi říci, že mikrobenchmarky jsou co do reprezentativnosti trošku podobné čistě syntetickým benchmarkům typu Dhrystone/Whetstone a podobně.

A přesně to nyní vyjasnilo i AMD, které se proti uvádění oněch 29 % samo oficiálně ohradilo. Prohlášení, které od něj dostal web HardOCP, upozorňuje, že tuto hodnotu nemáme brát jako příklad toho, o kolik bude Zen 2 rychlejší než Zen 1 v obvykle používaných programech. Poukazuje přitom na to, že šlo jen o příklad speciálního mikrobenchmarku, měřícího kód nějaké finanční aplikace.

Some news media interpreted a "Zen 2" comment in the press release footnotes to be a specific IPC uplift claim. The data in the footnote represented the performance improvement in a microbenchmark for a specific financial services workload which benefits from both integer and floating point performance improvements and is not intended to quantify the IPC increase a user should expect to see across a wide range of applications. We will provide additional details on "Zen 2" IPC improvements […] when the products launch.

AMD neuvádí, jaké zlepšení IPC bychom měli tedy místo toho čekat s tím, že více se o výkonu dozvíme až když procesory budou připravené k vydání. Z toho, že 29 % popřelo, by ale asi vyplývalo, že realita bude střízlivější. Osobně bych asi doporučil čekat typické zlepšení IPC spíš někde mezi 5 a 15 %. Otázka je ovšm, kde v tomto intervalu. Výjimkou by mohly být asi jen programy jako x265 silně využívající AVX2. V x265 by se možná nárůst výkonu na 1 MHz mohl oněm 29 % přiblížit. Shrnuto a podtrženo, jako všude tu asi platí, že je lepší mít přízemnější očekávání, protože ta častěji bývají naplněna.