Letos (snad v třetím kvartále) vyjdou procesory AMD s novou architekturou Zen 5. Bude to opět velká změna, zatímco předchozí Zen 4 byl v podstatě evoluce Zenu 3, a podle různých nepřímých náznaků, mezi nimiž jsou i výroky architekta Mike Clarka, by to prý mohla být vůbec nejzajímavější architektura AMD od prvního Zenu. Je zajímavé, že až dosud o ní byly informace z jediného youtuberského zdroje. Právě ale byly oficiálně potvrzeny přímo z AMD.

Všechny konkrétní informace o povaze jader Zen 5 (snad vedle toho, že desktopová CPU budou používat 4nm čiplety) pocházejí z tohoto úniku youtubera Moore's Law Is Dead. Ten odhalil jednak schéma jádra, ale jak si jistě pamatujete, také nástřel nárůstu výkonu na 1 MHz frekvence. Ten se podle těchto slajdů má zlepšit o 10–15+ % (ono plus asi má říkat, že 10–15 % je konzervativní spodní mez).

Zatímco na výkon ještě budeme dál napnutí, AMD nyní poslalo patch do kompilátoru GCC, používaného pro překlad zejména open source softwaru ze zdrojových kódů, který do něj přidává podporu optimalizace pro procesory Zen 5. Patch je pro nás zajímavý, protože popisuje řadu aspektů jádra a sedí s tím, co před časem ukazovaly slajdy publikované Moore's Law is Dead. To znamená, že nejspíš doložil jejich pravost, a můžeme se o ně tedy s poměrně slušnou mírou jistoty teď opírat.

Rozšířené jádro: víc ALU a AGU

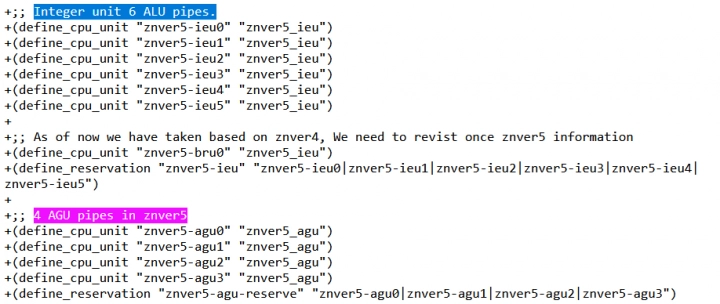

Patche pro GCC potvrzují rozšíření jádra Zen 5. Od první až po čtvrtou generaci tyto architektury zachovávaly hodně podobnou základní strukturu se čtyřmi aritmeticko-logickými jednotkami (ALU), které provádějí většinu nejtypičtějších instrukcí, byť u Zenu 3–4 jsou tři jednotky AGU (u Zenu 1–2 pouze dvě), které provádějí operace zápisů do paměti a čtení z ní. Toto je v kontrastu s vyšším počtem jednotek u jader Intelu, nemluvě o jádrech ARM, kde Cortex-X4 například ALU už obsahuje osm.

Bylo zajímavé, že AMD dokázalo z tohoto konkrétního počtu vytěžit relativně vyšší výkon než konkurenti, Zen 5 ale konečně v tomto parametru povyšuje. Patch potvrzuje, že jádro má šest ALU a čtyři AGU. To by mohlo provázet značné zvýšení IPC, i když z počátku nemusí být využití těchto jednotek navíc tak vysoké a další pokroky v IPC mohou být těžené až postupně v dalších generacích, podobně jako Zen 2, 3 a 4 dokázaly postupně dostat víc a víc výkonu ze čtyř ALU již přítomných v Zenu 1.

Zatím není úplně jasné, zda mají load/store pipeline (jednotky AGU) zvětšenou šířku z 256 bitů na 512 bitů, aby dokázaly v jednom cyklu číst a zapisovat 512bitový vektor pro instrukce AVX-512.

Naopak je jedna oblast, kde rozšíření není. Počet instrukčních dekodérů zůstává čtyři. Procesory x86 včetně architektur Zen ale mají jako alternativní řešení tzv. uOP cache, která ukládá již dekódované instrukce. Procesor by měl většinu času brát instrukce z uOP cache, která dokáže dodat výrazně více instrukcí za cyklus než čtyři dekodéry a současně je energeticky efektivnější. Tudíž počet dekodérů není tak důležitý jako u ARM procesorů bez uOP cache.

Nativní 512bitové AVX-512

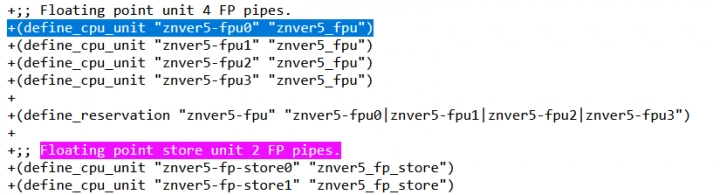

Jednotka FPU (která ale zejména zpracovává i SIMD instrukce), zdá se, nemá přidané pipeline navíc proti Zenu 3 a 4, v FPU zřejmě opět bude čtveřice pipeline pro různé operace. GCC ale potvrzuje, že Zen 5 má poprvé fyzicky 512bitové SIMD jednotky. Podporuje tak zpracování většiny instrukcí AVX-512 v jediném cyklu, zatímco Zen 4 má jednotky 256bitové jako jádra Zen 2 a Zen 3 (která uměla jen 256bitové AVX2).

Předchozí jádro proto 512bitové instrukce AVX-512 provádělo ve dvou průchodech, které vypočítávaly vždy polovinu šířky vektoru. Tomuto rozšíření SIMD v Zenu 5, zdá se, odpovídá přidání druhého portu pro operace Foating-point store. FP store jednotky jsou ale patrně stále 256bitové, takže 512bitové operace provádí sdružením obou jednotek.

Samo rozšíření šířky SIMD jednotek na 512 bitů znamená, že se teoretický výpočetní výkon udávaný ve FLOPS (ale totéž platí pro operace pracující s celočíselnými datovými typy) zdvojnásobí. Tímto by Zen 5 měl dohnat hrubý výkon jader Intelu ve všech parametrech, takže použití AVX-512 by například v serverech nyní mělo přinést výhodu AMD, zatímco doteď dávalo Intelu šanci dohnat vyšší celkový výkon procesorů Epyc (Intel by mohl mít ještě výhodu v odlišných maticových instrukcích AMX).

Patche pro GCC ale ukazují, že došlo k dalším zlepšením. V jednotkách SIMD nyní mají schopnost zpracovat operace typu shuffle (permutace) tři pipeline místo dvou, takže lze provést místo dvou tři tyto operace za cyklus. Došlo, zdá se, k redistribuci některých operací mezi porty v FPU. Floating-point sčítání má latenci sníženou ze tří na dva cykly, což by mělo přímo zlepšovat výkon, protože na sebe navazující výpočty mohou být zpracovány rychleji.

Nějaká zlepšení tohoto druhu má i celočíselná část. Vypadá to, že dvě nově přidané ALU umí víc než jen nejjednodušší operace, nebo AMD posílilo již existující ALU. Zatímco dosavadní jádra uměla zpracovat CMOV a SETCC jen na dvou ze tří ALU, Zen 5 podle patche do GCC tyto instrukce dokáže zpracovat ve čtyřech ze svých šesti ALU, tedy až čtyři za cyklus.

Dále se v patchi nachází informace, že by mělo být zrychleno dělení a výpočty druhé odmocniny, tyto instrukce mají sníženou latenci o jeden nebo více cyklů pro většinu datových typů.

Zen 5 bude umět některé instrukce AVX-512, které Intel ztratil (nebo zatratil?)

Z patche lze také vyčíst, že jádro Zen 5 bude navíc umět některé instrukce AVX-512, které Zen 4 ještě nepodporuje. Tato skupina instrukcí má totiž poměrně rozvětvenou (a kritizovanou) množinu subsetů. Zen 4 podporuje značnou část, ale nikoliv instrukce MOVDIRI, MOVDIR64B, PREFETCHI a AVXVNNI – ta bude užitečná pro AI, ale jde o 256bitovou verzi instrukce VNNI, jež byla přidána pro E-Core, zatímco Zen 4 ji umí v původní 512bitové verzi. AVXVNNI bude užitečné hlavně pro kompatibilitu s big.LITTLE procesory Intel. Tyto instrukce Zen 5 přidává.

Kromě nich také Zen 5 podporuje rozšíření s dlouhatánským názvem AVX512VP2INTERSECT (AVX-512 Vector Pair Intersection to a Pair of Mask Registers), které je zajímavě obskurní. Tyto instrukce u Intelu přidaly procesory Tiger Lake (architektura Willow Cove), ale pak si to zřejmě Intel rozmyslel, nebo nalezl v implementaci nějaké problémy, protože následné architektury, včetně aktuálních serverových procesorů Intel Sapphire Rapids, už zase AVX512VP2INTERSECT nepodporují.

Je možné, že se AVX512VP2INTERSECT ještě u Intelu vrátí. Vše po Tiger Lake má Intel stále založené na jedné architektuře Golden Cove, takže je možné, že AVX512VP2INTERSECT je rozbité jen v ní, respektive v její serverové verzi. Je zajímavé, že klientská CPU Alder Lake a Raptor Lake snad tuto instrukci podporují, dokud jim tedy Intel AVX-512 na sílu nevypnul. Ovšem zase nedávno prezentované plány na reorganizaci 512bitových instrukcí pod pláštík AVX10 s tímto rozšířením zatím nepočítají, takže je možné, že už se s implementací znovu nepočítá.

Možná tak vznikne legrační situace, kdy AMD opět jako v případě instrukcí FMA4 podporuje něco, co Intel nemá. Otázka je, zda to Zenu 5 prospěje, nebo to bude spíš nevýhoda. Tato instrukce totiž bude spotřebovávat tranzistory, které Intel bude moci ušetřit, ale software ji raději kvůli nepodpoře na Intelu možná nebude chtít používat. Toto je nevýhoda, se kterou se menší konkurenti často musí potýkat.

Není to ovšem tak, že by Zen 5 celkově uměl více instrukcí AVX-512 než jádra Intelu. Měl by mít větší pokrytí než desktopové a notebookové procesory (Ice Lake, Rocket Lake, Tiger Lake), ale serverové procesory Sapphire Rapids a nové Emerald Rapids mají několik dalších instrukcí, které Zen 5 ještě neumí.