Na Computexu 2024 byly Intelem představeny nové architektury Lion Cove a Skymont, kterým jsme se podrobně věnovali. AMD také nakouslo jejich konkurenta Zen 5, ovšem zatím jen letmo, takže kompletní rozbor architektury bude teprve v budoucnu. Ovšem těmto x86 procesorům přichází konkurovat vyzyvatel s instrukční sadou ARM – Snapdragon X Elite přicházející do notebooků. A Qualcomm teď také konečně poodhalil jeho „Nuvia“ architekturu Oryon.

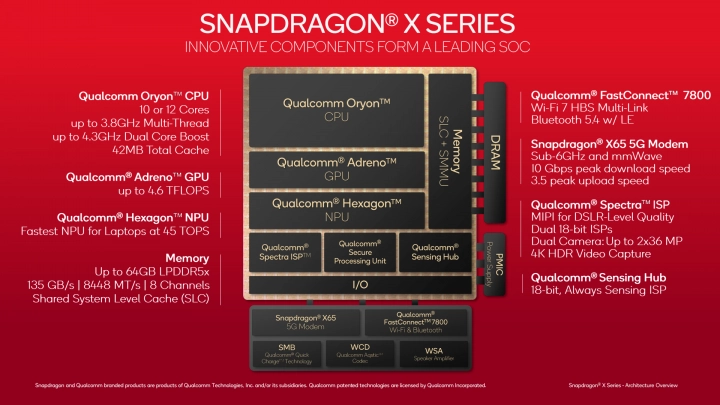

Když Qualcomm loni v říjnu tyto procesory formálně odhalil (poměrně dlouho před reálnou dostupností, jež začne příští týden), dostaly jméno Snapdragon X Elite (levnější modely se jmenují Snapdragon X Plus). Architektura jader CPU samotná je označována jako Oryon a je jen jedna, procesor má samá velká jádra bez big.LITTLE hybridizace.

Toto jádro je architekturou, kolem níž se už od roku 2019 tvořil „hajp“ ohledně toho, jak deklasuje procesory x86 (a dost se přitom zapomínalo, že to bude za několik let, během nichž se laťka nutně také zvedne). Tehdy to ještě bylo jádro „Phoenix“, vyvíjené firmou Nuvia, kterou založili inženýři předtím navrhující jádra Applu. Qualcomm poté Nuvii včetně týmu koupil a z jejího projektu udělal jádro pro vlastní mobilní SoC, tedy dnešní Oryon.

Nuvia Phoenix Qualcomm Oryon: Rozbor architektury

Jak přesně je architektura navržená, Qualcomm až do této chvíle neuváděl, ale tyto detaily byl odhaleny tento týden, takže lze konečně návrh trochu porovnat s konkurencí. Jádro má instrukční sadu ARMv8.7 a je z tohoto pohledu trošku starší než aktuální licenční Cortexy s architekturou ARMv9. Oryon tak například nepodporuje SIMD instrukce SVE a SVE2, které ale může zastoupit existující SIMD rozšíření Neon.

V praxi toto nemusí nijak moc vadit. Tedy pokud se Microsoft v budoucnu nerozhodne, že zvýší požadavky Windows a ARMv9 bude minimum (nebo bude povinné SVE2). Něco takového se nedávno stalo, ale doufejme, že ARMv8.7 bude podporována ještě dlouhé roky.

Je otázka, zda Qualcomm teď vůbec plánuje přechod na ARMv9, ARM totiž může tuto technologii možná spojovat s restriktivnějšími podmínkami a vyšším poplatky. V poslední době, zdá se, má v nelibosti, když firmy navrhují své vlastní architektury, místo aby si od něj licencovaly kompletní jádra Cortex, a s Qualcommem ARM vede dost nepřátelský soudní spor, kde dokonce požadoval, aby Qualcomm jádro Oryon zrušil a vymazal všechno vyvinuté IP.

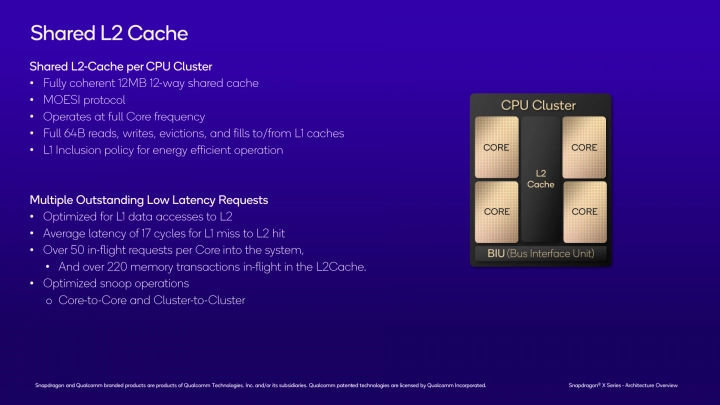

Čtyřjádrový základní blok se sdílenou L2 cache

Jádra Oryon se spojují v procesoru do čtyřjádrových klastrů, které tvoří základní stavební jednotku potenciálně portovatelnou do jiného čipu (vedle nynějšího 12jádrového čipu „Hamoa“ by údajně mohla existovat i levnější osmijádrová verze „Purwa“). Každý čtyřjádrový klastr může být nezávisle uspaný a lze pro něj nezávisle nastavovat frekvence (frekvence jednotlivých jader v klastru jsou, zdá se, mezi sebou svázané).

Čtyři jádra Oryon sdílí společnou L2 cache, podobně jako to dělá Intel u svých E-Core. Nicméně tato L2 cache je výrazně větší, má kapacitu 12 MB s 12cestnou asociativitou. Latence by zřejmě měla být průměrně 17 cyklů, tedy podobná jako u L2 cache jádra Intel Lion Cove (které má stejnou 3MB kapacitu L2 cache na jádro, avšak privátní). L2 cache běží na stejné frekvenci jako jádra v klastru. L2 TLB je osmicestný a má více než 8000 položek.

Tato cache by měla být inkluzivní, jsou v ní tedy zkopírované obsahy L1 cache všech jader v klastru (toto má pomáhat s energetickou efektivitou). Cache má být optimalizována na komunikaci jader mezi sebou a sdílení dat mezi nimi (a podporuje i požadavky jader z vedlejších klastrů). Podporuje až 50 současných požadavků na data z paměti pro jedno jádro a celkově až 220.

Naopak pokud data nejsou nalezená v L2 cache, podporují tzv. page walkery obsluhu až 16 současných požadavků na data pro každé jádro – tedy až 192 pro všech 12 jader procesoru.

Tento klastr údajně již teď podporuje integrování osmi jader místo čtyř, což možná byl plán pro původní jádra Phoenix, která Nuvia oficiálně chtěla nejdřív nasadit v serverech (ale asi hlavně proto, že to je oblast, kde nejsou třeba další technologie jako GPU, Wi-Fi, modem, a je tedy přístupná startupům). Je možné, že budoucí výkonnější procesory Qualcommu ještě toto oživí.

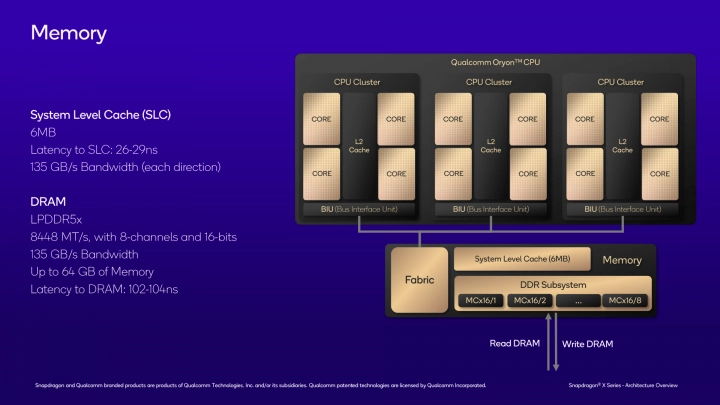

Před pamětí už jen SLC, žádná L3 cache

Nad L2 cachemi klastrů není společná L3 cache, která by paměťový subsystém unifikovala. Ale celý SoC ještě obsahuje tzv. System Level Cache (SLC), která tuto roli supluje, avšak zároveň cachuje data i pro další komponenty, jako je integrované GPU, NPU anebo jednotka pro zpracování obrazu z kamer.

Tato SLC cache má kapacitu 6 MB a podle Qualcommu dosahuje latence okolo 26–29 ns a propustnost 135 GB/s v obou směrech (tedy současně 135GB/s čtení i 135GB/s zápis). Propustnost je stejná i u samotné paměti DRAM (také 135 GB/s), ale pokrytí požadavků na data v rámci SLC by mělo být energeticky úspornější a s nižší latencí.

Operační paměť používaná procesory Snapdragon X Elite a Plus je LPDDR5X běžící efektivně na frekvenci 8448 MHz, použitých je osm 16bitových kanálů, jde tedy o paměti se standardní šířkou 128 bitů, jaké má třeba základní řada procesorů Applu (M1/M2/M3/M4) a běžné PC procesory s „dvoukanálovými“ pamětmi. Qualcomm uvádí, že latence RAM je typicky 102–104 ns. Maximální kapacita RAM, která se bude dát v počítačích s těmito procesory koupit, je 64 GB.

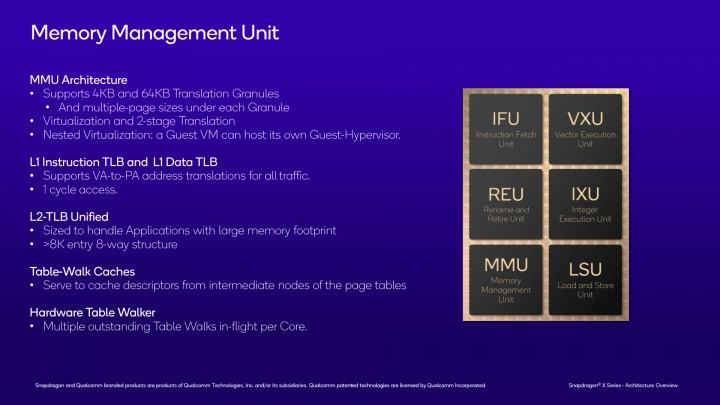

Jádro a L1 cache

Jednotlivá jádra mají jen privátní L1 cache. L1 instrukční cache (pro kód programu) má kapacitu 192 kB s 6cestnou asociativitou a Fetch z ní každý cyklus čte až 16 instrukcí (64 bajtů). Instrukční L1 má iTLB první úrovně pro 256 položek s 8cestnou asociativitou. Datová L1 cache má kapacitu 96 kB také s 6cestnou asociativitou. Latence bohužel Qualcomm neuvádí. Datový L1 TLB má 224 položek se 7cestnou asociativitou. Kapacity L1 cache jsou o dost větší než u x86 procesorů Intelu a AMD, ale Oryon má pořád menší L1 datovou cache než Apple (128 kB).

Podporované jsou 4kB a 64kB stránky, což je odlišnost proti Applu, který používá 16kB stránky. Windows pravděpodobně používají 4kB velikost kvůli kompatibilitě, malé stránky vedou k lepšímu využití RAM. Větší stránky mohou vést k plýtvání RAM podobně jako velké alokační jednotky v souborovém systému. Ale s velkými stránkami je možné trochu lépe využívat TLB, takže mohou zlepšit výkon. Je možné, že 64kB stránky jsou už trošku moc a 16kB stránky Applu by byly lepší kompromis než 64 kB. To je nicméně z hlediska instrukční sady ARM nestandardní velikost, kterou si Apple může prosadit kvůli tomu, jak tvrdou rukou může řídit svou platformu a i nezávislé vývojáře softwaru. Windows jsou mnohem otevřenější platforma, takže je pro ni asi vhodnější obětovat pár procent potenciálního výkonu navíc a zůstat u starých 4kB stránek.

Jádro má samozřejmě dnes standardní pokročilé technologie prefetche dat do L1 a L2 cache a pokročilý prediktor větvení, který je víceúrovňový. Qualcomm uvádí, že postih při špatně odhadnutém větvení je 13 cyklů, což trochu naznačuje, jak je zhruba dlouhá pipeline jádra. Obě tyto součásti jsou kritické pro schopnost udržet jádro plně zaměstnané a předcházet prostojům, což ve výsledku znamená, že kód se zpracuje rychleji (čili výkon na 1 MHz je vyšší).

8 dekodérů, masivní RoB

Fáze dekódování je obsluhována 8 paralelními dekodéry, což je očekávané od hodně velkého jádra ARM (Intel se tomuto ale už v Lion Cove také vyrovnal a Apple s ARMem v posledních architekturách zkoušejí 10 dekodérů). Dekodéry překládají instrukce ARM na micro-opy (uOpy), s nimiž jádro interně pracuje, přičemž jedna instrukce může být přeložena do jednoho nebo více uOpů.

V tomto tedy v rozporu s populárním spojováním architektury ARM s koncepcí RISC není v podstatě rozdíl proti x86 procesorům (a až tak velký rozdíl není ani v počtu instrukcí, kterých je také velký počet). Distinkce CISC versus RISC nemá pro dnes moderní procesory téměř žádnou praktickou relevanci, primární přetrvávající odlišnost mezi koncepcí ARMv8/v9 a x86 (respektive x86–64) je v tom, že ARM má všechny instrukce s délkou 32 bitů, zatímco u x86 je proměnná.

Reorder Buffer, který tvoří okno instrukcí, které jádro najednou vidí a v kterém může provádět své optimalizace a vyzobávat připravené operace k okamžitému vykonání mimo pořadí, má kapacitu „víc jak 650 operací“, což znamená, že je větší než RoB velkého jádra Intel Lion Cove (576). Jádro má přes 400 fyzických obecných registrů a také přes 400 fyzických SIMD/FPU registrů pro přejmenování registrů architektonických.

Kolik ALU máš? Aneb backend jádra

Celočíselná část má šířku 6 pipeline a obsahuje 6 ALU. Čtyři ALU jsou zřejmě jednoduché, dvě komplexní, protože Qualcomm uvádí, že jádro umí provádět dvě násobení za cyklus. Na dvou z těchto pipeline je s ALU také jednotka pro větvení. Každá z těchto pipeline má před sebou vlastní frontu Reservation Queue o 20 položkách.

Počet šesti ALU je dnes už dost standardní, nebo brzo bude. Patrně ho zvolilo AMD v Zenu 5 a také Intel Lion Cove. Na druhou stranu jádra Applu i Cortex-X4 a Cortex-X925 už se snaží přidávat ještě víc ALU.

Čím vyšší počet ALU ale v jádru je, tím těžší je hledat jim práci. Sedmá a osmá ALU jsou asi často aktivní malé procento běhu procesoru, takže „deficit“ jen šesti ALU třeba proti osmi je asi v realitě poměrně malý, ač to (+33 %) na první laický pohled může vypadat jako masivní rozdíl.

Stále 128bitové SIMD jednotky

FPU, respektive vektorová/SIMD jednotka má čtyři pipeline, což je stejné jako u Applu nebo i u Intelu (Cortex-X925 je ale ambicióznější s 6 pipeline), každá pipeline má Reservation Station o 48 položkách. Jádro umí na všech čtyřech pipeline zpracovat celočíselná i floating-point sčítání i násobení. Vektory umí datové typy INT8, INT16 a vyšší, FP16, FP32, FP64. Nejsou podporované novější formáty používané pro AI jako BFloat16 nebo čerstvé FP8.

Jak už ale bylo řečeno, nejsou podporovány instrukce SVE ani SVE2, jednotka pracuje s klasickými SIMD instrukcemi Neon. A tím je i dána šířka vektoru a fyzické jednotky 128 bitů. Nicméně ani jádra Cortex s SVE2 nemají širší jednotky, takže se rozdíly stírají.

Celkově mají jádra ARM v tomto nevýhodu proti výkonným jádrům Intelu a AMD, které mají 256bitové, nebo (Zen 5, serverové Intely) dokonce 512bitové jednotky SIMD, takže jejich teoretická výpočetní kapacita je u každé jednotlivé pipeline dvojnásobná, nebo dokonce čtyřnásobná.

Load/Store část má také čtyři pipeline/AGU. Každá má Reservation Station o 16 položkách a datové šířky, s kterými čtecí a zapisovací pipeline pracují, jsou také 128 bitů (takže je možné uložit nebo načíst data pro 128bitový vektor Neon jednou operací). Všechny tyto pipeline jsou univerzální, umí tedy zpracovat jak čtení, tak zápisy – zde šly Nuvia/Qualcomm opačným směrem než Intel, který naopak v poslední architektuře všechny jednotky udělal jednoúčelné.

Jádro Oryon tudíž umí udělat až čtyři zápisy nebo čtyři čtení za cyklus, nebo jakoukoli kombinaci maximálně čtyř operací. Podporována je technika Store to Load Forwarding, která obchází paměť, pokud se čte z adresy, na kterou předtím CPU data zapisuje. Fronta pro čtení má 192 položek a fronta pro zápisy 56 položek.

Virtualizace, emulace?

Procesor podporuje virtualizaci, včetně tzv. Nested Virtualization, což znamená, že můžete spustit další hypervizor v rámci operačního systému, který je už sám virtualizovaný. Podle Qualcommu také při návrhu bylo dbáno na odolnost proti různým side-channel útokům typu Spectre, proti kterým má jádro ochrany (respektive „mitigations“, což nemusí být nutně neprůstřelná ochrana, ale třeba jen i opatření na ztížení takových útoků). V některých částech procesorů je údajně pro data použito blokové šifrování, aby byla před side-channel útoky data „obfuskována“.

Qualcomm také prozradil, že jádro Oryon má i jisté speciální úpravy zaměřené na to, aby na něm rychleji běžely programy pro x86 procesory, tedy přesněji řečeno, aby při použití překladu/emulace takových programů v reálném čase byl výkon vyšší. Mělo by jít například o hardwarovou podporu v jednotce FPU, která se při běžném ARM režimu chová trochu jinak než na x86 (x87) a obsluha těchto odlišností by hodně srážela výkon, tudíž jádro při emulaci je instruováno, aby se samo přepnulo do režimu odpovídajícímu x86.

Podobně zřejmě Oryon podporuje přepnutí jader do režimu, který respektuje striktnější paměťový model architektury x86 (toto ovlivňuje mnohovláknové programy, ne jednovláknové). Technologie Rossetta 2 od Applu využívá pokud známo v podstatě stejné techniky (popisuje je třeba tento článek), také integrované v jádrech jeho procesorů.

Toto znamená, že snížení výkonu x86 aplikace na Snapdragonu X Elite nebude tak velké oproti nativnímu běhu na jádrech x86, jaké bylo doteď pozorováno u počítačů s Windows běžícími na starších jádrech Cortex, která byla ale také sama o sobě pomalejší. Jinými slovy, výkon x86 aplikací považovaný obecně u ARM Windows za špatný (jiná věc je, že většinou to lidé asi nemají moc podložené reálnými čísly, takže nemusí jít o úplně realistické sentimenty) by s novými procesory Qualcommu měl být výrazně lepší. Úplně plný výkon bude samozřejmě ale jen v nativních aplikacích přímo zkompilovaných pro instrukční sadu ARM.

Tyto hardwarové funkce pomáhající v emulaci budou využívány překladačem Prism ve Windows 11, který je sám o sobě vylepšený. Pro připomenutí – Microsoft má tuto technologii překladu x86 aplikací na ARM počítačích na trhu už od roku 2017 (podpora 64bitových aplikací přišla o něco později), tedy déle než Apple.

Závěrem

Architektura Oryon by měla být docela silná a odpovídá to asi i výkonnostním číslům, které Qualcomm slibuje a za pár dní snad už budou i doložená. Jádro neobsahuje nějaká velká překvapení, tým Nuvie na věc šel patrně konzervativně a bez riskování zopakoval recepty, které předtím jeho vedoucí použili pro jádra Applu: tedy široké jádro s velkou L1 cache. Typické jsou pro to i ty velké sdílené L2 cache místo sdílené L3 cache.

Nicméně současně se také inženýři nesnažili hned Apple trumfnout v počtu dekodérů nebo ALU (což se trošku zdá, že zamýšlí ARM u Cortexů linie X), takže má možná nyní vyváženější design, byť třeba nebude tak výkonný jako širší nejnovější Apple M4.

Neobjevila se tedy nějaká exotická úplně nová technika nebo rys či nějaký unikátní a potenciálně převratný (nebo fatální v případě neúspěchu) nápad. I když je možné, že něco takového ještě přijde v dalších generacích – že vývoj pokračuje a přijdou Oryony 2, 3 a tak dále, je už oficiálně potvrzené.

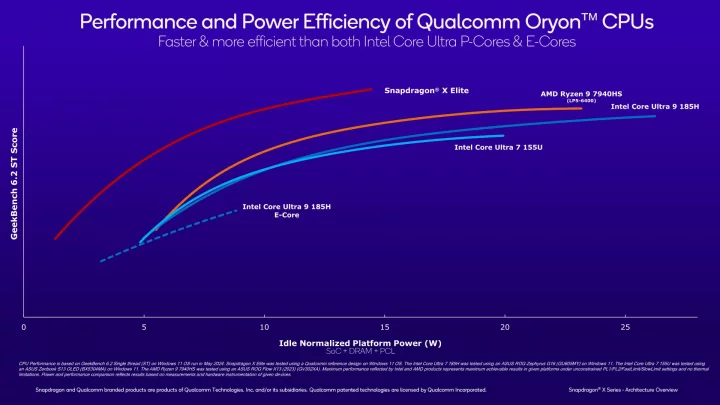

Loňské x86 procesory poraženy, ty aktuální teprve uvidíme

Jádro Oryon má vyšší IPC (výkon na 1 MHz) než aktuální konkurence v podobně procesorů AMD Ryzen 8000 (Zen 4) a Intel Meteor Lake (Redwood Cove), které tak podle Qualcommu má porážet i přes nižší frekvence (maximálně 4,25 versus ~5,1 GHz v noteboocích). Přitom má mít také nižší spotřebu jednoho jádra, podle Qualcommu by Snapdragony X Elite měly mít maximální spotřebu v jednovláknových aplikacích někde okolo 15 W proti nějakým 23 W u AMD (Ryzen 9 7940HS) a 27 W u Intelu (Core Ultra 9 185H – všechna tato čísla jsou od Qualcommu, takže si s verdikty raději počkejte na nějaké nezávislé recenze).

AMD i Intel ale v létě uvedou nové generace procesorů, které mohou tyto výsledky pochopitelně změnit (Apple také mezitím přišel s novým procesorem M4). Výsledná situace pak nemusí být, že by „Nuvia“ Snapdragon X Elite porážel všechnu konkurenci, jak to bylo předběžně slibováno, ale určitě by měl být konkurenceschopný. Pak už to samozřejmě bude na schopnostech Qualcommu prodat čip výrobcům notebooků a tom, jak schopní budou zase tito výrobci při prosazení těchto notebooků u zákazníků.

Zdroj: AnandTech