AVX-512 bude rozšířením x86 instrukcí typu SIMD z šířky 128 bitů (u SSE až SSE4) a 256 bitů (u AVX/AVX2) na 512 bitů. Teoreticky by tedy mohly vést k zdvojnásobení propustnosti některých operací, pokud takto široký vektor budou schopné saturovat. Zajímavé je, že toto rozšíření má být od 14nm generace Knights Landing sdíleno s procesory či akcelerátory Xeon Phi. Protože ale zavádějí novou sadu registrů (ZMM), budou instrukce AVX-512 potřebovat explicitní podporu operačního systému.

Podle informací, které uvádí italský web Bits and Chips, Intel rozšíření AVX-512 alespoň ze začátku uvede jen do profesionální sféry. Aktivní tedy bude jen u procesorů Xeon pro servery, ale nikoliv u čipů Skylake na desktopu, které mají být uvedené koncem letošního léta.

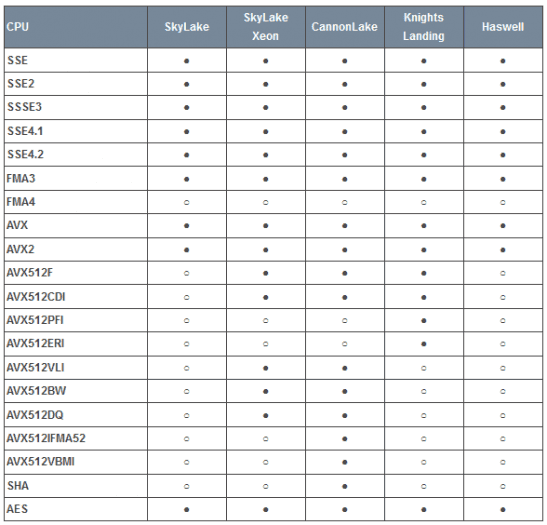

Podpora AVX-512 se bude mezi různými procesory lišit

AVX-512 také nebudou monolitickou sadou instrukcí. Jak vidíte v následující tabulce, obsahují devět komponent, z nichž ani serverový Skylake nebude umět vše. Xeony Skylake mají umět jádro sady AVX-512 Foundation (AVX512F), což by mělo být přímočaré rozšíření většiny instrukcí AVX na 512 bitů. Dále AVX-512 Vector Lengths Extension (AVX512VLI), což bude naopak adaptace instrukcí nově zavedených v rámci AVX-512 na menší 128bitové a 256bitové registry sad SSE a AVX.

Dále sadu AVX-512 Conflict Detection Instructions (AVX512CDI) pro řešení konfliktů, což má usnadňovat vektorizaci kódu. A co bude důležité pro multimediální kód – už v generaci Skylake bude AVX-512 umět také operace s celočíselnými hodnotami (8 bitů a 16 bitů v rozšíření AVX512BW a 32bitů a 64bitů v rozšíření AVXDQ), což využijí například enkodéry videa do HEVC nebo VP9.

Knights Landing bude umět značně jiný subset operací: základní AVX512F a AVX512CDI pro detekci konfliktů. Zbytek instrukcí podporovaných u Skylake neumí, zase ale bude umět unikátní rozšíření AVX512PFI a AVX512ERI. První z nich značí instrukce pro přednačítání (prefetch), druhé pak Exponential and Reciprocal Instructions, tedy instrukce pro výpočet transcendentních matematických funkcí.

Podpora AVX-512 u procesorů Intel Skylake, Cannonlake a Kinghts Landing (Zdroj: Bits nad Chips)

Cannonlake bude mít instrukce pro SHA-1/SHA-256

Tabulka webu Bits and Chips také ukazuje další rozšíření plánovaná pro čipy Cannonlake, které by měly přijít po generaci Skylake na 10nm procesu, údajně v roce 2017. Cannonlake dostane vše, co bude umět Skylake, ale nikoliv specifické instrukce Xeonu Phi Knights Landing. Nově ale přibudou rozšíření AVX512VBMI (AVX-512 Vector Byte Manipulation Instructions) a AVX512IFMA52 (AVX-512 Integer Fused Multiply Add). První z nich bude přidávat některé instrukce vynechané v AVX512BW – například permutaci bajtů nad 512bitovým vektorem. Druhé pak bude rozšířením celočíselných operací FMA3 spojujících v jednom kroku součet a násobení na 512bitové vektory.

Kromě toho si také můžete všimnout, že Cannonlake má přidat další rozšíření specializované na akceleraci kryptografie: po AES přijde u 10nm procesorů na řadu také algoritmy SHA-1 a SHA-256 (Intel SHA Extensions). Tabulka ovšem u Cannonlake neuvádí, které instrukce budou vyhrazené Xeonům, a které (pokud vůbec nějaké) se dostanou i do desktopu. Můžeme tedy doufat, že v roce 2017 se 512 vektory dostanou i do běžných PC, zároveň bych se ale radši připravil i na eventualitu, že to bude jako u Skylake a AVX-512 stále zůstane jen v serverech či superpočítačích. Určitý impuls správným směrem by zde mohlo dát AMD, pokud by AVX-512 implementovalo i v desktopu. Jaké má ale tato firma ve směru 512bitových instrukcí plány, není v tuto chvíli vůbec známo.

Zachrání to Xeon E3?

Ještě je třeba dodat, že z pohledu desktopového uživatele chtivého těch nejprogresivnějších rozšíření instrukční sady ještě nemusí být všem dnům konec. Intel nespecifikuje, kterých Xeonů se AVX-512 bude týkat. Možná by tedy mohlo být i u řady E3, pasující do desktopového socketu LGA 1151. Tyto procesory bývají často podporovány běžnými spotřebitelskými deskami a někdy se dají dokonce pořídit relativně levně (přinejmenším levněji než Core i7). Možná, že cesta k AVX-512 tedy povede touto cestou. Ovšem za předpokladu, že desktopové čipy fyzicky budou toto rozšíření podporovat na úrovni křemíku. Je možné, že jej Intel vůbec neimplementuje a pak budete k jeho otestování potřebovat skutečně serverový čip Xeon E5.

Socket LGA 1151 pro procesory Skylake na desce ASRock IMB-190 (Zdroj: ComputerBase)

Zdroj: Bits and Chips