Nevím, zda máte ještě všichni v živé paměti dobu před uvedením procesorů Haswell. Tehdy jsme měli v docela velkém předstihu mnoho informací o architektonických změnách těchto čipů, včetně například toho, že jádro dostane čtvrtou ALU, L4 cache (eDRAM) a podobně. Příchod Skylake je proti tomu takový zvláštní. Kromě taktů a podobných detailů jsme se nedozvěděli nic bližšího o jádrech procesoru nejen během týdnů před jeho premiérou, ale dokonce ani po ní. To bylo o to víc zvláštní, když recenze u tohoto „tocku“ ukazovaly nárůsty IPC, které se blížily spíše „ticku“. Nicméně tento dluh teď Intel částečně umazal na konferenci IDF, kde přece jen závoj poodhalil.

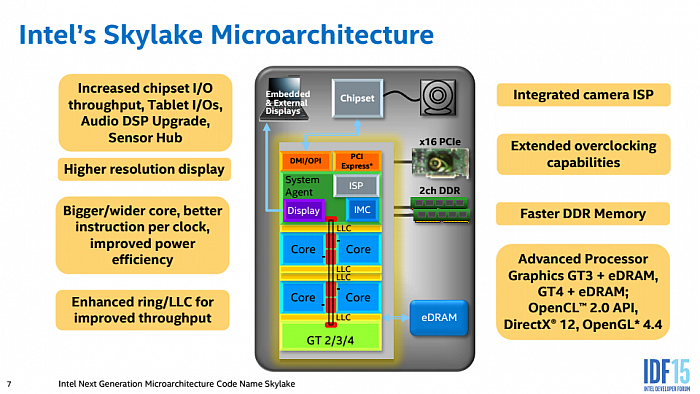

Že se poslední dobou Intel soustředí na mobilní sféru nejen u „malých“ procesorových architektur (Silvermont, Airmont), ale i u těch velkých, původně desktopových, není nic nového. A v tom, co firma říká o nejnovějším Skylake, je toto opět potvrzeno – tyto procesory už nejsou dělané jen pro vysoce výkonné procesory pro servery a stolní PC, ale vedle notebooků i pro tablety s řádově nižšími limity spotřeby. První, čím se Intel v prezentaci na IDF pochlubil, je charakteristicky to, že Skylake má zatím největší škálu použití co do typů a rozměrů zařízení, v nichž jej lze použít, a co rozsahu TDP, na něž lze tuto architekturu škálovat. A kromě rozhraní, která tradičně má mít desktopový procesor, má také různé periférie specifické pro tablety, jako podporu pro senzory nebo vlastní DSP pro zpracování obrazu z fotoaparátu.

Na druhou stranu to neznamená nějakou technologickou stagnaci. Jak hned uvidíme, na architektuře Skylake Intel stále odvedl patřičnou práci s vývojem, včetně úprav zaměřených na výkon. Ty se (kromě dalších komponent jako čipsetu nebo grafického jádra) týkají jak jader CPU, tak tzv. „uncore“, tedy jejich obslužné infrastruktury a paměťového subsystému.

IDF 2015: Architektura procesorů Skylake

Jádra Skylake: širší a hlubší Out of Order

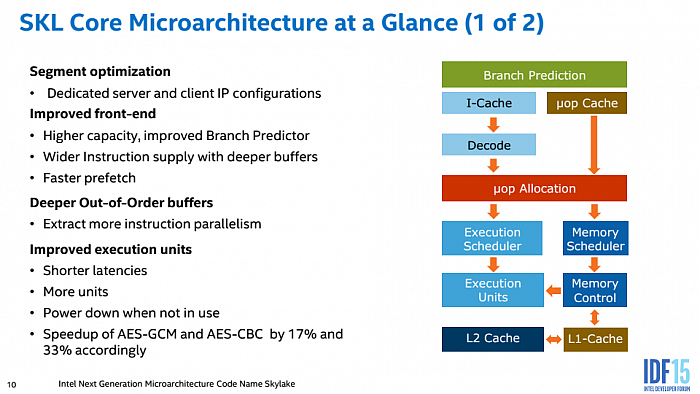

Na začátek: zdá se, že u Skylake nebude existovat jen jedna základní verze jádra, která by se pak objevila v podstatě stejná ve všech variantách – tedy jak v notebookových, tak v serverových a desktopových čipech. Intel zmiňuje, že pro serverová CPU a pro segment „client“ (tedy desktopy, notebooky, tablety) má dvě zvláštní, na tyto role optimalizované větvě architektury. Ačkoliv to není přímo řečeno, tato segmentace znamená například absenci podpory AVX-512 v desktopovém Skylake. Zdá se, že tyto instrukce nejsou jen uměle deaktivované, ale desktopový Skylake pro ně vůbec nemá hardware, takže asi nebudou obsaženy ani v Xeonech-E3. 512bitový hardware pro ně ponese až Skylake-EP, který ještě není na pořadu dne a podle všeho bude vlastně jiným jádrem.

V tzv. frontendu procesoru, tedy v blocích zpracovávajících kód předtím, než dojde k vlastním výpočtům, by měla být vylepšena predikce větvení. To je zlepšení, na nějž se inženýři zaměřují dlouhodobě, neboť špatně odhadnuté větvení vede k velkým výkonnostním ztrátám. Posílen by měl být také prefetch (přednačítání dat z paměti). Slajdy zmiňují širší „zásobování instrukcemi“, což by mohlo znamenat větší výkon instrukčních dekodérů.

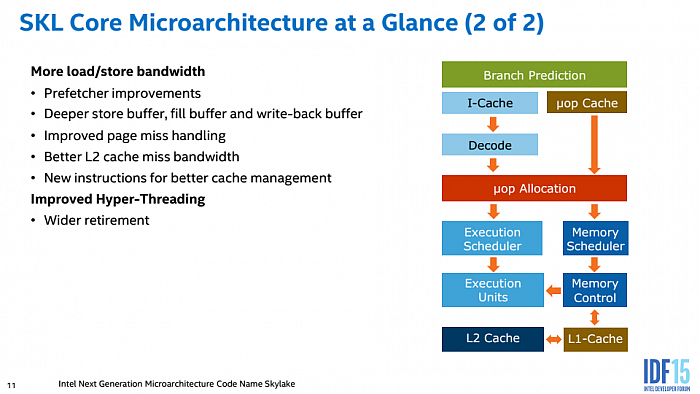

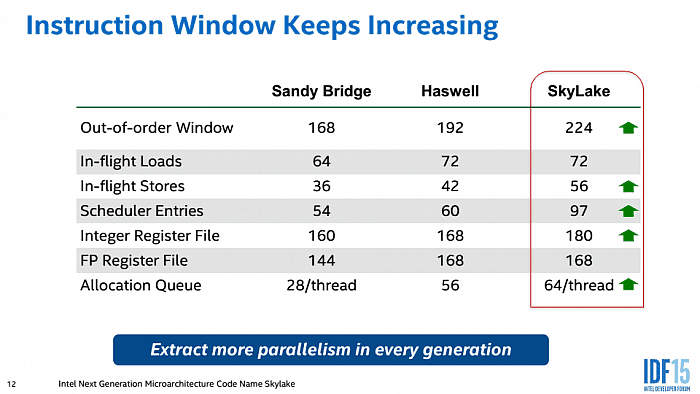

Intel u Skylake posílil systém vykonávání instrukcí mimo pořadí (tzv. „out of order execution“). Ten pracuje s větším „oknem“, tedy větším blokem vykonávaného programu naráz. Tím pádem lze více přehazovat instrukce, lépe tak zaměstnat výpočetní jednotky a vykonat více operací za takt. Jak se zvětšily různé fronty a buffery, můžete vidět na slajdu, srovnávající Skylake s Haswellem a Sandy Bridge. Skylake pracuje naráz až s 224 instrukcemi (Haswell: 192), scheduler instrukcí má místo 60 hned 97 míst a počet zápisů dat, které může mít CPU naráz ve frontě (a tedy je optimalizovat) je 56 instancí místo 42 u Haswellu. Jádro má také více hardwarových registrů, sloužících k přejmenování registrů architektonických, čímž se dají eliminovat přístupy do paměti.

Tyto zvětšené buffery a fronty představují evoluční posilování architektury, ovšem jejich dopad na výkon nemusí vůbec přímo úměrný daným číslům. Už u Haswellu se zdálo, že tyto struktury nebyly příliš velkými brzdami výkonu a jejich zvětšování u Skylake se také zdá se neodráží v dramatickém nárůstu výkonu na takt. Patrně se zde tedy projevuje zákon klesajícího užitku. Jinými slovy, tuto architekturu je pro Intel stále obtížnější pohánět k vyššímu IPC.

Výpočetní jednotky navíc?

Nějaké změny by Skylake mělo mít i v samotných výpočetních jednotkách, k těm ale bohužel tolik konkrétních detailů není. Slajdy zmiňují, že by dokonce mohly být nějaké přidány. Ale jaké, to je opět otázka. Intel zmiňuje, že podstatné zvýšení propustnosti by mělo být v šifrování AES. Další instrukce by pak měly mít snížené latence (což znamená, že trvá méně cyklů, než je výsledek operace k dispozici; vyšší latence může zpomalovat, pokud výsledek hned potřebuje další instrukce na řadě a tuto závislost nelze kompenzovat přehozením jiných operací do vzniklé bubliny). Individuální výpočetní jednotky v jádře by CPU mělo za běhu vypínat, pokud nejsou třeba, čímž šetří elektřinou. Toto platí například pro hardware zodpovědný za energeticky náročné instrukce AVX2. Intel také zmiňuje, že by se u Skylake proti předchůdcům měla zvýšit efektivita HT, při běhu dvou vláken na jednom jádře by tedy mělo být zrychlení nad úroveň jediného vlákna vyšší než s Haswellem.

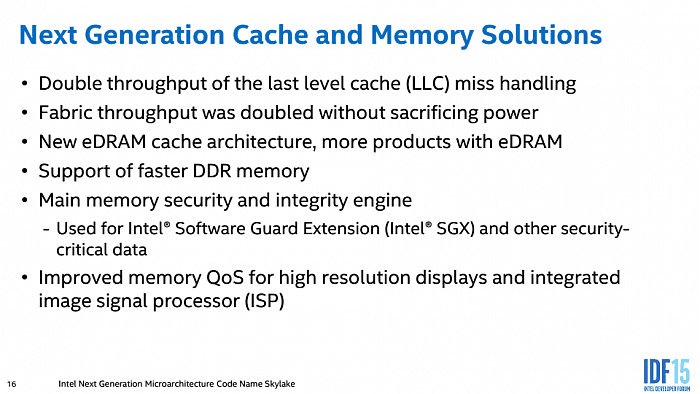

Procesor Skylake by měl mít větší výkon při práci s pamětí. Vedle zmíněného prefetche a zvětšených bufferů pro zápis z registrů by měly být efektivnější také cache, zlepšeno by mělo být řešení výpadků stránek a L2. Celkově by načítání a ukládání (load/store) mělo mít větší propustnost. Značně posílená by měla být také interní prstencová sběrnice, propojující jádra, bloky L3 cache, grafiku, paměťový řadič a další I/O. Její propustnost by měla být dokonce dvojnásobná, což se bude hodit třeba i při použití rychlejších pamětí DDR4, které Skylake nabízí.

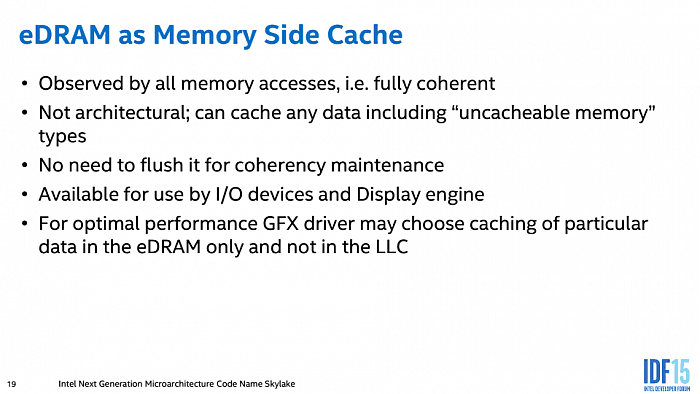

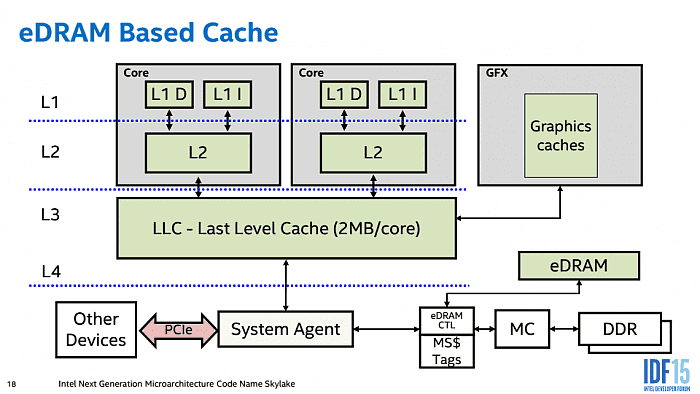

Z eDRAM je plnohodnotná L4 cache

Podstatné změny se udály u L4 cache tvořené pamětí eDRAM, kterou některé Skylaky budou volitelně mít. První změnou je, že tato cache dostala v procesoru vyhrazenou Tag RAM, což je paměťový blok, v němž CPU drží informace o tom, které části operační paměti jsou v L4 cache zkopírovány. Pro 128MB blok eDRAM jsou na to třeba 2 MB, které byly u Haswellu a Broadwellu ukrojeny z L3 cache (což je důvod, proč mají procesory řady H nebo C s eDRAM kapacitu L3 cache jen 4–6 místo 6–8 MB). Skylake už bude mít Tag RAM vyhrazenou, takže L3 neutrpí a bude mít plnou velikost. Negativem je, že tyto tranzistory jsou zabrány i u čipů, které eDRAM nemají, což je většina.

L4 cache tvořená eDRAM by nyní měla být plně koherentní bez potřeby manuální synchronizace, je přidružena k integrovanému severnímu můstku/system agentu (pod nějž patří paměťový řadič a další IO) a může cachovat celý obsah RAM. eDRAM by také nyní měla být přímo přístupná grafickému jádru i vstupně-výstupním zařízením včetně například ovladače obrazovky, zatímco dříve byl přístup k ní omezenější. Může nyní použita třeba k obnovování obrazovky v úsporném režimu, takže se pro tuto operaci nemusí probouzet některé jiné části systému.

Jádra Skylake: širší a hlubší Out of Order

Spotřeba, věčný nepřítel. Bezpečnost, věčný nepřítel

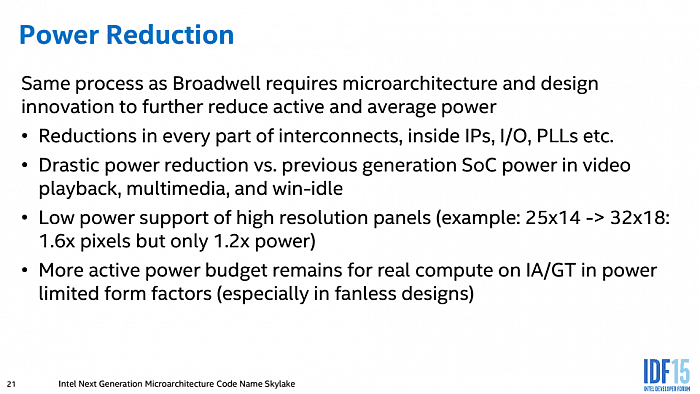

Jak už bylo nadhozeno, snad ještě větší důraz byl v Skylake kladen na spotřebu, kterou je třeba značně zkrotit, aby se byť i nízko taktované dvoujádro s čipsetem vešlo do TDP circa 4,5 W vhodného pro tablety. Jelikož je používán stejný proces jako pro Broadwell, je tíha optimalizací zcela na architektonických úpravách. Intel uvádí, že se mu podařilo ušetřit na většině interních komunikačních rozhraní a čip má značně lepší spotřebu v různých významných režimech, například při přehrávání videa nebo hudby, provozu kamery a stavu nečinnosti. Snížena by měla být i spotřeba při obsluze LCD panelů s vyšším rozlišením.

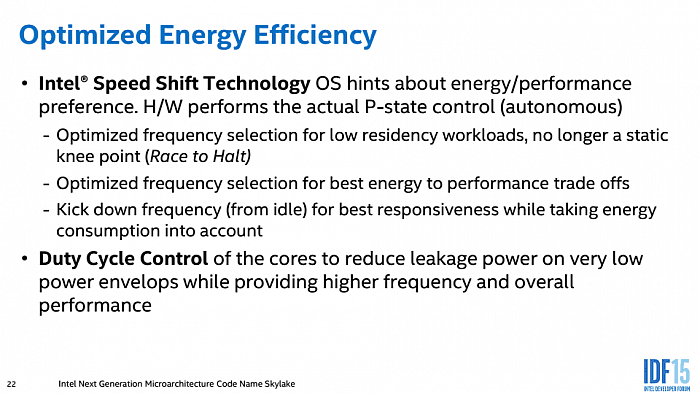

Intel Speed Shift

Co je na správě spotřeby asi nejinovativnějšího, je technologie nazvaná Intel Speed Shift. Ta spočívá v hardwarovém řízení výkonnostních režimů (tzv. P-states), zatímco dříve byla volba frekvence, na níž měl procesor běžet, záležitostí operačního systému. S použitím Speed Shift si stav, tedy frekvenci a napětí, umí procesor podle zátěže přepínat sám, což by jednak mohlo vést k lepší optimalizaci celkově spotřebované energie, kromě toho má ale přepínání v režii CPU být až 30× rychlejší. Čip může rychleji jít do turba a naopak rychleji začít spořit, když pomine zátěž, případně se pohotověji pohybovat někde uprostřed.

Procesor by skrze Speed Shift také měl lépe umět řešit stavy, kdy je zátěž nízká, ale kontinuální. To znamená, že nelze zvýšit výkon, aby se jí CPU rychle zbavilo, a poté se rychle uspat do úsporného režimu, což je u architektury x86 obvykle preferováno (tzv. model „race to idle“). Při takovéto zátěži může mít výhodu jinak méně efektivní systém big.LITTLE čipů ARM, kdy je v SoC pro takové použití připravena sada slabých, ale úsporných jader navíc. Skylake by měl být ale na podobné úlohy již také lépe optimalizován a měl by při nich spotřebovávat méně energie.

Nevýhoda systému Speed Shift je, že funguje jen s kompatibilními operačními systémy, což je v tuto chvíli toliko Windows 10. Na starších se používá tradiční řízení spotřeby. Podporu by měl eventuálně dostat také Linux, ovšem v tuto chvíli ještě hotova není. Volba frekvencí by jinak neměla být úplně nezávislá na softwaru – OS by stále měl mít schopnost určit rozsah stavů, do nichž může CPU přecházet.

Skylake má pro škrcení příkonu ještě jednu technologii: Duty Cyle Control. Nejde o nic jiného, než o „throttlování“, vkládání nečinných cyklů, čímž se sice sníží výkon, ale také spotřeba. Procesor Skylake při použití Duty Cycle Control vlastně běží přerušovaně, periodicky vypíná aktivní bloky a vrací se k práci. Prodlevy mezi aktivními okamžiky a neaktivními se mohou měnit, čímž lze snížit spotřebu i v momentě, kdy už CPU běží na své minimální frekvenci a nedokáže se podtaktovat a podvoltovat níže. Throttling tak vlastně simuluje další snížení frekvence.

Nové bezpečnostní prvky: SGX a MPX

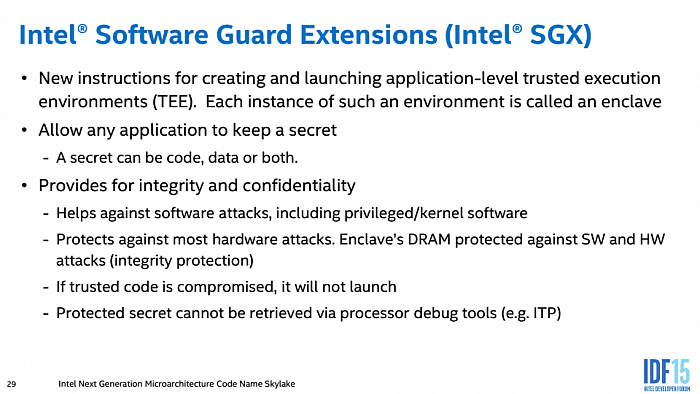

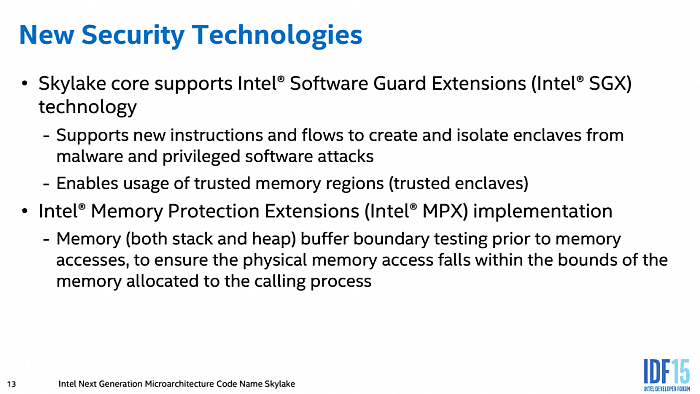

Skylake má ještě jednu hardwarovou novinku: přidané instrukce pro implementaci tzv. „trusted“ režimů a aplikací, tedy ověřeného a bezpečného prostředí pro citlivé programy. Rozšíření Intel SGX (Software Guard Extensions) spočívá v zavedení takzvaných enkláv, použitelných jednotlivými programy. Enkláva je místo v paměti, které procesor hardwarově chrání před neautorizovaným přístupem. Lze v něm tedy třeba schovávat certifikáty, které nesmějí uniknout, nebo kód DRM. Enkláva je také chráněná před útoky včetně eskalace privilegií. V tomto prostoru lze držet „tajná data,“ k nimž nemá být přístup. Zároveň je hlídána integrita kódu, který enklávu používá – když je zjištěno kompromitování, není spuštěn. Z enklávy také není možné vytáhnout obsah debugerem.

Druhým rozšířením pro posílení bezpečnosti je MPX, neboli Memory Protection Extensions. To spočívá v tom, že procesor hardwarově ověřuje, zda přístupy do paměti nepřekračují rozsah paměti, jenž byl mateřským programem prve alokován. Fyzicky je tak bráněno chybám stack/heap buffer overflow (přetečení bufferu), které by při zneužití narušily prostor jiných procesů. Při použití MPX by tak měl být procesor schopen zamezit některým útokům, které takové zranitelnosti zneužívají.

Jakožto rozšíření nejsou nicméně MPX a už vůbec ne SGX technologií, která by běžela sama od sebe; programátoři je teprve budou muset přidat do svého kódu (částečně by snad mělo stačit jen překompilovat stávající). Aplikace techniky jako MPX by totiž mohla rozbít programy, které na starších procesorech běžely, jelikož chyby v nich nebyly odhaleny. Jde tedy podobně jako u výkon zvyšujících rozšíření instrukční sady spíše o kapitál do budoucna, který bude moci být oceněn až časem.

S architekturou Skylake se tímto prozatím rozloučíme. Praktickému dopadu hardwarových změn na výkon nových jader se podívá na zoubek recenze, kterou momentálně připravujeme.