Začátkem tohoto roku se objevily zákulisní zprávy o tom, že v příští CPU architektuře svého velkého jádra chce firma ARM dosáhnout velkého skoku ve výkonu, kterým by ideálně chtěla dohnat náskok, který má se svými procesory Apple a nyní i Qualcomm s jádrem Oryon v Snapdragonu X Elite. Kvůli tomuto deficitu byli v nevýhodě výrobci například čipů do mobilů pro Androidy a motivovalo je to jako Qualcomm k vývoji vlastních jader, na čemž ARM tratí.

Cortex-X5 = Cortex-X925

Toto jádro, které údajně má kódové označení Black Hawk, bylo nyní oficiálně představeno. Nebude se ale jmenovat Cortex-X5 v návaznosti na předchůdce, ale Cortex-X925. Jde o sladění se systémem označení ostatních jader v portfoliu, kdy prostřední jádro se jmenuje Cortex-A725 a malé Cortex-A520 (jde tedy o podobné odlišení výkonu čísly 9, 7 a 5, jaké má Intel nebo AMD).

Cortex-X925 ještě „rozšiřuje“ jádro co do paralelních jednotek majících za cíl maximalizovat počet operací, které architektura dokáže zpracovat v jednom cyklu. Jádro je v těchto parametrech zřejmě dokonce širší než aktuální architektury Applu, byť zřejmě bude mít celkově nižší výkon – zejména díky horším dosahovaným frekvencím, ale možná i horšímu IPC.

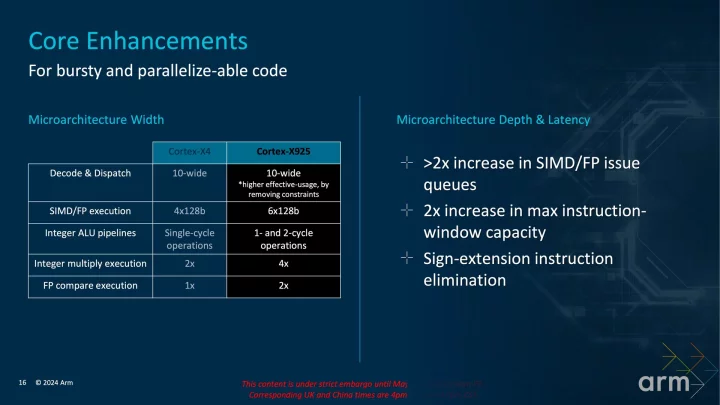

Cortex-X925 nepoužívá jako x86 procesory tzv. uOP cache pro již dekódované instrukce, místo toho vždy instrukce dekóduje hrubou silou a obsahuje 10 paralelních instrukčních dekodérů (Apple M3 a nejspíš i M4 by měl obsahovat devět). Deset operací (dekódovaných instrukcí) za cyklus zvládne i fáze dispatch.

Toto zrovna není rozšíření, protože 10 dekodérů už měl Cortex-X4. Nicméně X925 by je měl umět více efektivně využít, protože dekódování podléhá menšímu množství omezení (není to specifikováno, ale asi jde o to, že více z těchto deseti jednotek jsou komplexní dekodéry, které umí dekódovat i komplexní instrukce proti zbylým jednoduchým dekodérům, který dekóduje jen ty jednodušší).

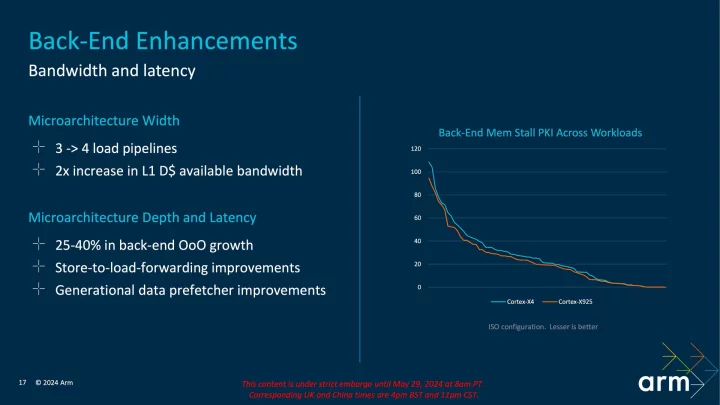

ARM zvýšil počet pipeline pro čtení z paměti, které jsou čtyři (takže je možné obsloužit čtyři operace za cyklus). V zápisech asi zůstalo u schopnosti dvou zápisů za cyklus. U L1 cache pro data zvýšena propustnost na dvojnásobek.

ARM neuvádí, že by jádro přidalo další ALU k rekordním osmi v Cortexu-X4 (a popravdě ještě asi tento počet typicky spíš není využitý, než že by byl úzkým hrdlem výkonu). Některé operace v ALU, zdá se, nyní zaberou dva cykly, což by mohlo být za účelem zvýšení frekvencí. Firma uvádí jen obecný údaj, že „hloubka“ asi ve smyslu různých front a schedulerů byla zvětšená o 25–40 %.

6-wide SIMD/FPU, ale pořád jen 128bitové vektory

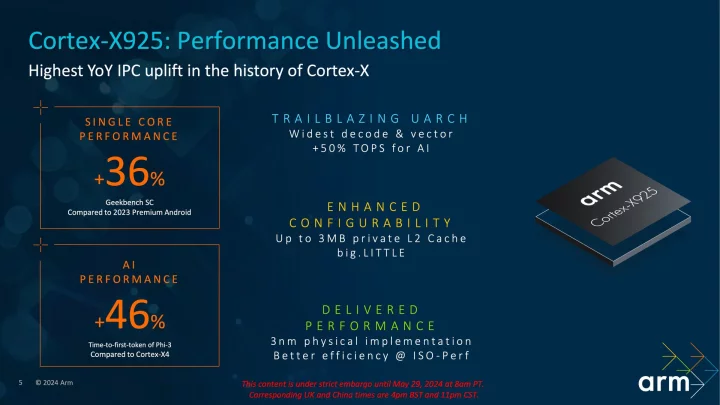

Kde ale jádro patrně ztloustlo (v dobrém slova smyslu), je jednotka SIMD. Ta má místo čtyř SIMD pipeline nyní šest těchto jednotek, čímž se hrubý matematický výkon zvyšuje o 50 %. Týká se to minimálně celočíselných instrukcí NEON a SVE 2, protože ARM uvádí toto zlepšení jako „+50 % TOPS“ a využití uvádí v AI, kde typicky půjde o inferenci používající hodnoty INT8.

Celočíselné násobení nyní umí místo dvou z těchto pipeline rovnou čtyři. U floating-point operací například došlo k posílení operací FP Compare, jádro zvládne dvě za cyklus místo jedné v Cortexu-X4. Jádro mimochodem dostalo navíc schopnost provádět operaci sign-extension už ve frontendu, aniž by to zaměstnalo vykonávací jednotky.

SIMD jednotky ale zůstávají na šířce 128 bitů, takže ač podporují SVE a SVE 2, z hlediska výkonu to nebude příliš znát proti použití starších fixních SIMD instrukcí NEON. S výjimkou případů, kdy SVE umožní vektorizovat něco, co v NEONu nešlo. Výpočetní kapacita bude kvůli tomuto menší než u jader Intelu nebo AMD (Zen 2 až 4 mají 256bitovou šířku, nadcházející Zen 5 dokonce 512bitovou, také jedna instrukce má dvakrát nebo čtyřikrát vyšší výpočetní výkon).

Při čím dál vyšších počtech jednotek se hlavním problémem stává najít pro ně práci kvůli omezeným možnostem out-of-order paralelizace (třeba kvůli tomu, že CPU čeká na data, nebo kvůli závislostem instrukcí). Čistě počet paralelních jednotek tedy nemusí být vše. Aby procesor snáze dokázal plnit velký počet jednotek prací ze sekvence instrukcí zpracovávaného programu, má podle ARMu dvakrát větší Reorder Buffer proti Cortexu-X4, tedy frontu instrukcí, v které je CPU může různě přehazovat (také se mluví o „oknu“, které procesor vidí a ze kterého může vybírat instrukce připravené k vykonání).

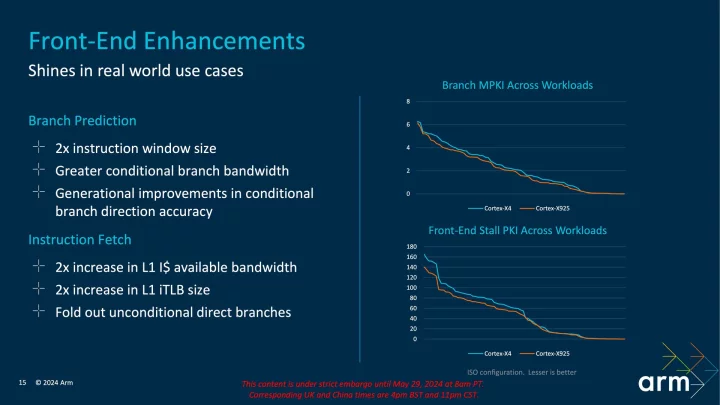

Cortex-X925 má dvakrát větší L1 instrukční TLB (translation lookaside buffer), cože je cache pro mapování adres fyzické paměti na logické adresy (v tomto případě pro kód programu), takže její zvětšení by mělo zlepšit efektivitu a výkon paměťového subsystému. U samotné instrukční L1 cache byla zvětšená její datová propustnost na dvojnásobek (tedy zvětšením šířky fetche a tím počtu instrukcí načítaných v každém cyklu), což je patrně pro hladší krmení oněch 10 instrukčních dekodérů, které z ní čtou instrukce. Jádro jinak poskytuje instrukční sadu ARMv9.2.

Jako vždy má jádro vylepšenou predikci větvení, což je oblast kriticky přispívající k využití onoho množství jednotek v jádru a tím k „IPC“ procesoru (tedy výkonu na 1 MHz frekvence). Stejně tak byl vylepšený prefetch a také store-to-load forwarding. Cortex-X925 také může mít privátní L2 cache s kapacitou až 3 MB.

Vyšší IPC a výkon než Apple A17 Pro? Na M4 ale asi nebude stačit frekvence

Toto jádro (respektive čipy, ve kterých bude použito) by většinou mělo být vyráběno 3nm procesem. Podle ARMu má dosahovat lepší efektivity – při stejném výkonu má mít nižší spotřebu než předchozí generace (Cortex-X4). Nebo současně při určité dané spotřebě dosáhne vyššího výkonu.

Nicméně v reálu bude architektura asi vždy použita k dosažení vyššího výkonu – její křivka výkonu a spotřeby bude škálovat dál/výš než u předchozí architektury. Takže spotřeba jádra může narůst, ale mělo by při tom podávat adekvátně vyšší výkon.

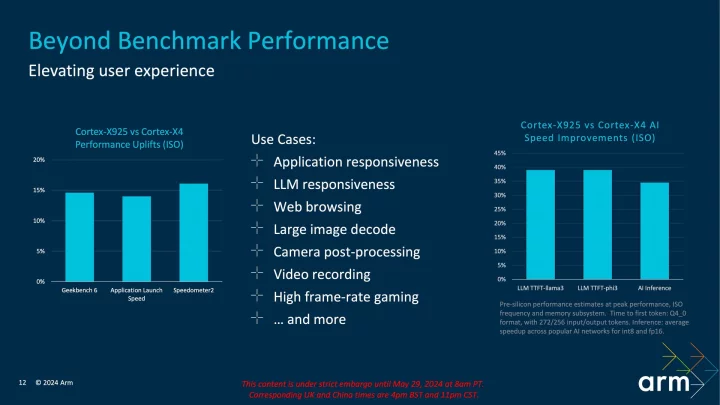

Podle projekcí firmy má Cortex-X925 mít IPC vyšší o zhruba 15 % proti Cortexu-X4 (+15 % v jednovláknovém Geekbench, +14 % v rychlosti spouštění programů, +16 % Speedometer). Celkový nárůst výkonu v jednom vlákně ale prý může být až o 36 % vyšší než u Cortexu-X4 v telefonech.

V tomto čísle je už zahrnut efekt toho, že Cortex-X925 také dosáhne výrazně vyšších frekvencí než Cortex-X4, a také softwarové optimalizace a zlepšení platformy (pokud byste měřili stejným programem bez těchto pomůcek, pak čistý nárůst výkonu pomocí IPC a taktu bude nižší, podle grafu to vypadá na +33 %).

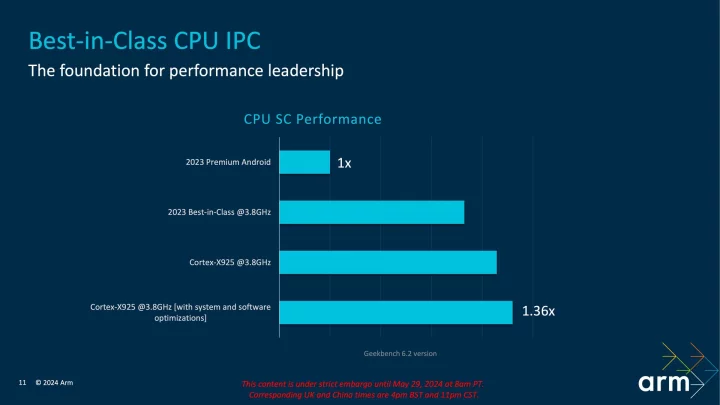

Zdá se, že dosažitelný takt bude 3,8 GHz, nebo alespoň tolik ARM plánuje v telefonech. Při této frekvenci má údajně Cortex-X925 podávat i vyšší výkon než Apple A17 Pro (ten také dosáhl taktu až 3,8 GHz), tedy alespoň v jednovláknovém Geekbench 6.2, rozdíl by měl být v řádu jednotek procent. Podle grafů ARMu má A17 Pro dosahovat zhruba 1,27× vyšší výkon než Cortex-X4, zatímco Cortex-X925 oněch 1,33× až 1,36× (s dodatečnými optimalizacemi).

Jádro od ARMu by tedy tentokrát mohlo mít vyšší IPC než Apple. I když teprve uvidíme, zda se potvrdí, že porazí i novější procesor M4 pro počítače a tablety Applu. M4 dosáhl taktů až 4,4 GHz, takže by měl být schopen uhájit výkonnostní nadvládu nad tímto novým licencovatelným jádrem ARMu (tolik k názorům, že zvyšování výkonu frekvencemi není důležité a to jediné důležité je IPC…).

Přelomový bod v konkurenci Androidu a Applu…

Nicméně pro ARM by toto byl tak jako tak velký úspěch. Dosud byla jeho nejvýkonnější procesorová jádra vždy výrazně slabší (o čtvrtinu, třetinu) v ostře sledovaném jednovláknovém výkonu. Apple na tom dost stavěl v marketingu proti telefonům se systémem Android, které byly na jádra Cortex odkázané.

Pokud by se Cortex-X925 opravdu takto vyrovnal Applu A17 Pro, byla by to pro výrobce čipů, jako je MediaTek a Samsung, skvělá zpráva. A je to něco, na co by ještě třeba před rokem asi málokdo vsadil peníze. Ačkoliv se očekávalo, že Cortexům uteče už nejen Apple, ale také Qualcomm se svými jádry Oryon, tak to zatím vypadá, že licencovatelným jádrům od ARMu se podaří dotáhnout se na tyto architektury a po dlouhé době být plně konkurenceschopný.

To by samozřejmě také bylo slibné pro použití na nich založených procesorů v noteboocích s Windows, což plánuje například Nvidia. Je ale samozřejmě třeba ještě počkat, zda se tyto projekce výkonu od ARMu potvrdí a zda konkrétní mobilní (a případně notebookové) procesory opravdu budou dosahovat takto dobrých výsledků.

Reálně se SoC s architekturou Cortex-X925 asi začnou objevovat v zařízeních až za několik měsíců. Apple mezitím asi už bude mít novou generaci A18, kterou by ARMu mohl zase utéct, ale proti původním masivním náskokům to může být relativně malé vedení, které v praxi nebude znamenat tolik.

Zdroje: AnandTech, ComputerBase