ARM tento týden uvedl novou architekturu Cortex-X3, která bude novým nejvýkonnějším jádrem CPU pro telefony a notebooky, nabízeným touto firmou. Spolu s ním také přichází nové jádro Cortex-A715, které bude X3 doplňovat. Tato linie jader (Cortex-A76 až A78, pak A710), která dříve představovala velká jádra ARMu, se, zdá se, mění v jádra vyladěná na co nejlepší výkon v malé ploše a spotřebě, takže teď budou čímsi jako E-Core u Intelu.

ARM Cortex-A715 by měl být jádrem, které před dvěma lety bylo avizováno pod kódovým označením Makalu (a tehdy u něj byl slíbený o 30 % vyšší výkon proti Cortexu-A78, za chvíli uvidíte, zda to bylo splněno).

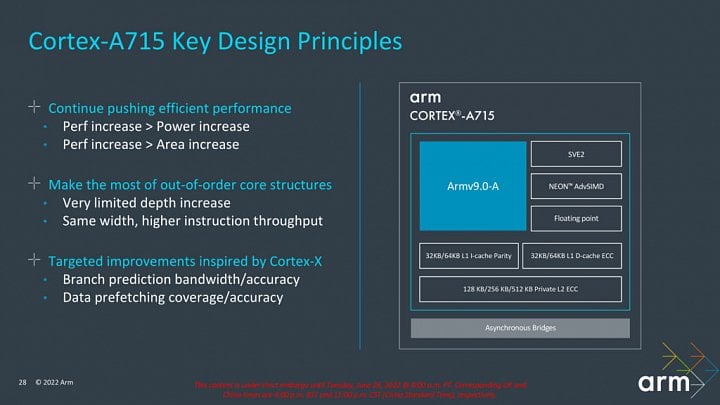

Jádro Cortex-A715 používá instrukční sadu ARMv9 a je čistě 64bitové, zcela odstranilo podporu pro 32bitový kód, což mu stejně jako Cortexu-X3 umožnilo různé optimalizace a změny. Koncepce tohoto jádra vychází z toho, že ARM rozdělil linii velkých jader na dvě větve. Jádra Cortex-X usilují o co nejvyšší jednojádrový výkon a jsou ochotné za tímto účelem obětovat nějakou tu energetickou efektivitu (vyšší výkon za cenu výrazně vyšší spotřeby) a větší investice do počtu tranzistorů (plochy na čipu).

Cortexy linie A ale mají za cíl mít co nejlepší poměr výkonu a spotřeby a zároveň výkonu a zabrané plochy. Podobně jako E-Core Intelu by měla být ideální pro dosažení vysokého mnohovláknového výkonu v určitém omezeném limitu spotřeby (alespoň v kontextu telefonů). Není náhoda, že serverovou architekturu Neoverse N určenou pro mnohojádrové cloudové procesory ARM odvozuje od Cortexu A.

Změny v jádře

Novinky v Cortexu-A715 se částečně podobají změnám v Cortexu-X3, ale u prostředního jádra byly provedeny hlavně úpravy ve frontendu (zatímco Cortex-X3 také zvýšil počet ALU v celočíselné části ze 4 na 6). Obě společně vyvíjené linie se teď také, zdá se, víc diferencují.

Posílené prediktory větvení

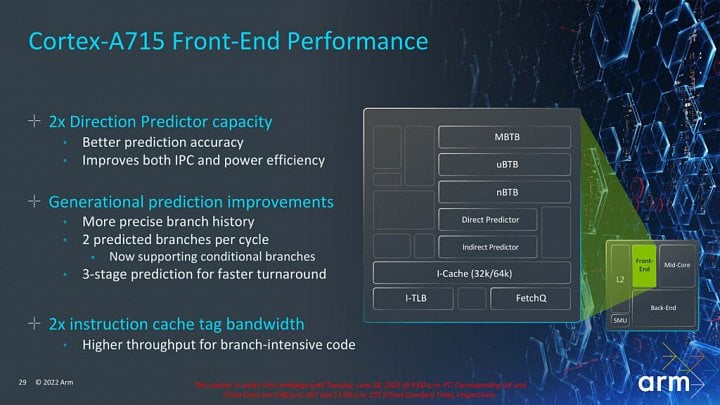

ARM se hodně soustředí na predikci větvení a prefetch, protože tím pomáhá energetické efektivitě (ale také tím zvyšuje IPC jádra), ty jsou v jádru Cortex-A715 opět vylepšené. Obecně má stoupnout přesnost predikce (úspěšnost odhadu). Direction Predictor má dvojnásobnou kapacitu a historie větvení má být přesnější.

Cortex-A710 používal dvě úrovně predikce větvení – rychlou L0 s latencí 0 cyklů a přesnější L2 predikci s latencí dva cykly, která případně rychlou první predikci zkoriguje. Cortex-A715 má místo toho třístupňovou predikci, přidávající ještě mezistupeň s jednocyklovou latencí predikce a přesností někde mezi L0 a L2 prediktory.

Také ale byl zvýšen výkon prediktorů. Jádro umí provést predikci dvou větví za jeden cyklus a nově to umí i pro podmíněné větvení (conditional branches). Toto pomůže v kódu, kde je větvení velmi časté. Pro takové případy také byl zvětšen výkon vyhledávání tagů v L1 cache pro instrukce, což by mělo pomáhat, když se kvůli větvení z cache načítá více separátních sekvencí instrukcí současně.

Víc dekodérů místo uOP cache

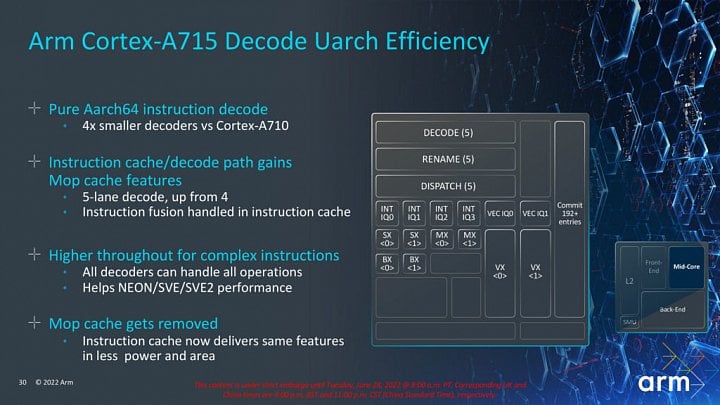

Velká změna je u instrukčních dekodérů. To, že jádro je čistě 64bitové, dovolilo výrazně zmenšit instrukční dekodéry. Údajně až na čtvrtinovou velikost proti Cortexu-A710 a také mají mít nižší spotřebu. Už u Cortexu-X3 jsme viděli, že ARM díky tomuto přidal další dekodér navíc, a ještě si mohl dovolit zmenšit uOP cache pro již dekodóvané instrukce, jejímž smyslem je normálně šetřit energii tím, že se fáze dekódování instrukcí přeskočí (a šetří se tím i místo, protože jádro pak potřebuje méně dekodérů).

V Cortexu-A715 se ARM zřejmě rozhodl, že spotřeba zmenšených enkodérů je dostatečně nízká a uOP cache není třeba, takže toto jádro ji zcela odstraňuje a všechny zpracované instrukce nejprve projdou dekodérem. Vrací se tak zpět před Cortex-A77, který toto vylepšení zavedl (ale na druhou stranu uOP cache stále zůstává u velkého jádra Cortex-X3). Místo uOP cache přidal ARM jádru další instrukční dekodér, kterých tedy jádro již má pět místo čtyř, a dokáže tedy dekódovat a k dalšímu zpracování odeslat pět instrukcí za cyklus. V předchozím jádře uOP cache prováděla fúzování mikroOPů, tato schopnost je teď, zdá se, zajišťována ještě před fetchem na úrovni instrukční L1 cache.

Eliminace uOP cache zhorší o něco výkon, ale větší kapacita dekódování by to měla vyrovnat zpět (Cortex-A710 dokázal poslat pět instrukcí z uOP cache, ale přímo z dekodérů jen čtyři). Kromě toho jsou všechny dekodéry nyní komplexní a dokáží zpracovat všechny instrukce. Dříve bývala část jednodušší a některé složitější instrukce mohly být zpracované jen vybranými komplexními dekodéry (toto používá pro zjednodušení i Intel).

Zlepšení v load-store části

Naopak počty samotných vykonávacích jednotek ALU a FPU se nezměnily, ARM u tohoto jádra tedy ponechal „backend“ při starém a zaměřil se na to, aby byl jeho výpočetní potenciál lépe využitý, k čemuž slouží předešlé popisované změny ve frontendu. Pravděpodobně to také znamená zachování 128bitových vektorů u instrukcí SVE2 (což ale bude souviset i s tím, že se jádro v big.LITTLE konfiguracích dál páruje se starým Cortexem-A510).

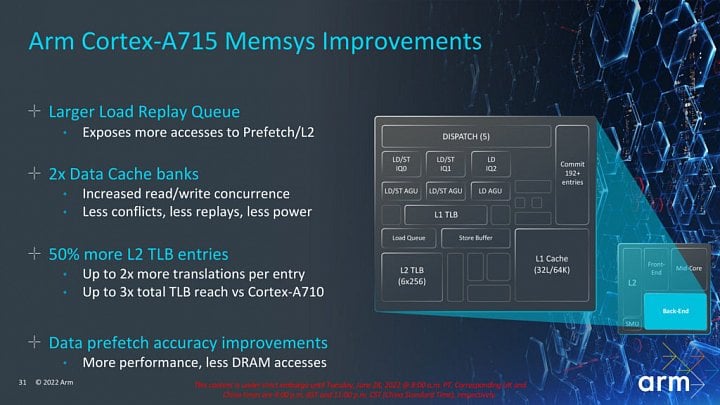

Změny jsou nicméně v load-store části – cíl je opět stejný, lépe využít stávající výpočetní zdroje tím, že jednotky nebudou čekat na data z paměti. L2 TLB byl zvětšen o 50 %, ovšem navíc může jedna položka uchovávat dvakrát víc virtuálních adres, takže za určitých okolností se efektivní kapacita až ztrojnásobuje.

Dále ARM zvýšil počet banků, ze kterých se skládají datové cache (asi L1 i L2?). Toto umožňuje efektivnější přístup, kdy je lépe možné kombinovat současné čtení i zápis a také dochází k méně konfliktům.

Také byla prohloubena fronta Load Replay Queue, takže je možné zpracovávat současně více požadavků na data z L2 cache. A jádro by také obecně mělo mít lepší prefetch zlepšující výkon CPU a omezující počet potřebných přístupů do paměti.

Drobné zlepšení pro výkon, ale slušný skok v efektivitě

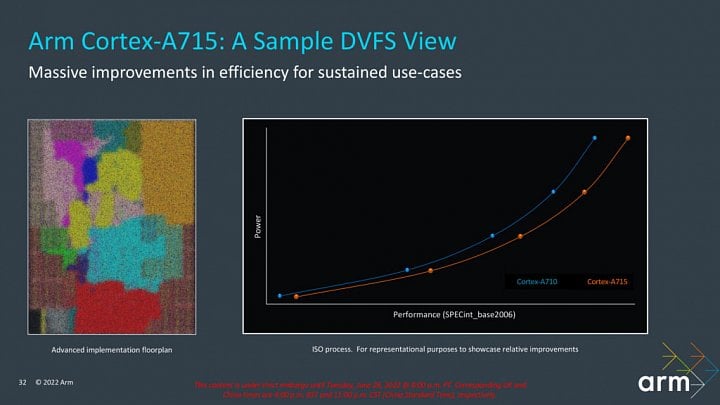

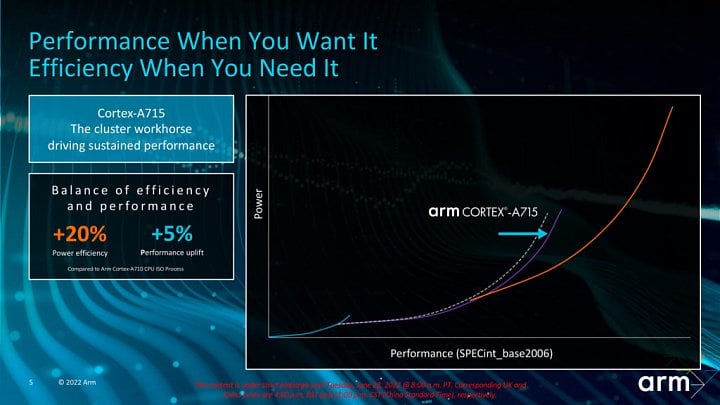

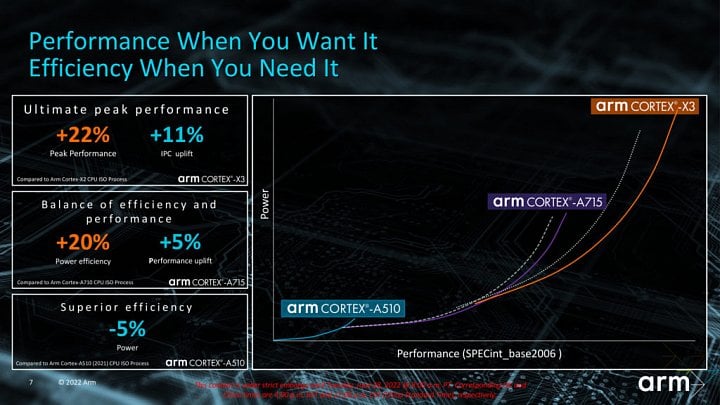

Výsledkem těchto změn je jádro, které není ve výkonu nějak moc převratné. Podle ARMu má při stejné spotřebě dosahovat asi o 5 % lepšího výkonu, než dosáhne Cortex-A710 při použití stejného výrobního procesu. Nicméně pokud by se ekvalizoval výkon, má Cortex-A715 běžet stejně rychle jako Cortex-A710 s o 20 % nižší spotřebou. ARM ale také uvádí, že Cortex-A715 má dosahovat zhruba podobný absolutní výkon jako Cortex-X1, tedy „velké“ jádro z doby před dvěma lety.

Nicméně se zdá, že ARM úplně nesplnil avizovaný cíl z roku 2020, že A715 (Makalu) bude mít o 30 % lepší jednovláknový výkon proti Cortexu-A78. Proti tomuto dva roky starému jádru má Cortex-A715 jen asi o 15 % vyšší IPC (výkon na 1 MHz) a navýšení frekvence asi zbytek nedožene. Zlepšení nového prostředního jádra/E-Core jsou tak hlavně v tom, že má nižší spotřebu.

Roadmapa a vylepšená verze malého jádra Cortex-A510

ARM v poslední době uváděl novou architekturu velkého (a v posledních letech velkého a prostředního) jádra každý rok. Toto bude pokračovat i v následujících letech. Firma již nyní sdělila kódová jména příštích dvou generací – následující jádro Cortex-A7xx bude „Hunter“ a další po něm „Chaberton“. Zatím o nich nic dalšího sděleno není, ale aspoň tedy víme, že i v roce 2023 i 2024 přijdou nové či aktualizované architektury.

Podobnou roadmapu také ARM ukázal pro linii malých úsporných jader (jako byl Cortex-A53, A55 a A510). V té letos nové jádro uvedeno nebylo, jak už jsme zmínili, Cortex-X3 a A715 se budou dál párovat s existujícím jádrem Cortex-A510. Jeho nový následník by údajně měl být vydán v roce 2023 a má kódové označení „Hayes“ (jádro A510 je „Klein“). Tudíž nová generace této linie přijde v příští generaci současně s jádrem Hunter (a asi také Cortexem-X4).

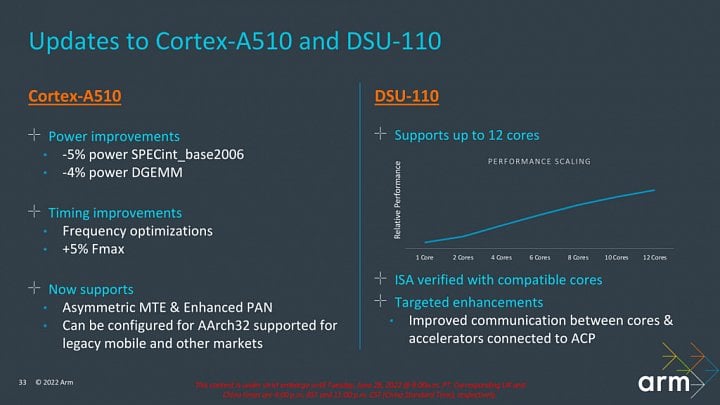

Jako náhradu nového malého jádra ovšem ARM také něco má. Jádro Cortex-A510 prošlo menší inkrementální revizí či refreshem. Ta by neměla měnit jeho plochu, ale údajně asi o 5 % snižuje jeho spotřebu (a tím zlepšuje energetickou efektivitu). ARM uvádí také o 5 % vyšší maximální dosažitelné frekvence. Také je podporována jeho integrace do až 12jádrových SoC. Nové ARM procesory s Cortexem-A715 a případně Cortexem-X3 by měly asi obvykle používat tuto aktualizovanou mírně účinnější verzi jader A510 místo původní.