Už loni se objevily informace, že po loňském novém integrovaném GPU Gen11 chystá Intel na letošek úplně nové GPU, jehož architektura Gen12 nebo po novém Xe bude zřejmě největší inovací integrované grafiky Intelu za několik posledních let. Letos tato architektura přichází na trh v procesorech Tiger Lake a prvním novodobém samostatném GPU Intelu Xe.

Minulý týden Intel odhalil procesory Tiger Lake a jejich vylepšený 10nm proces SuperFin. Spolu s tím prozradil i v čem je nová tato GPU architektura „Xe LP“, takže můžeme v tomto článku podniknout její analýzu.

Xe LP: nová architektura na začátku nové GPU éry Intelu

„Architektura Xe“, či asi lépe řečeno architektura Xe první generace, po níž budou následovat další, není úplně stoprocentně nová. Podle nynějších odhalení vychází z toho, co předtím Intel vyvinul v architektuře Gen11/Ice Lake (původní kódové jméno je také Gen12).

Ale jsou zde opravdu velké změny (řekli bychom, že například větší, než mezi GCN a RDNA u AMD), takže opravdu lze mluvit o určitém rebootu a tom, že Intel vstupuje do nové éry s novým architektonickým začátkem, v souladu s dřívějšími průsaky, dle nichž Gen12/Xe bude u Intelu největší změnou za tuto dekádu.

Podpora DirectX 12: Ultimate ještě ne, jen Feature Level 12_1

GPU Gen12/Xe LP patří hardwarově na úroveň DirectX 12 grafik, přesněji na tzv. feature level DirectX 12_1. Nepodporuje ještě nové DirectX 12 Ultimate. Podporuje funkce Bindless Resources Tier 2, Tiled Resources Tier 2, Raster Order Views a Conservative Rasterization.

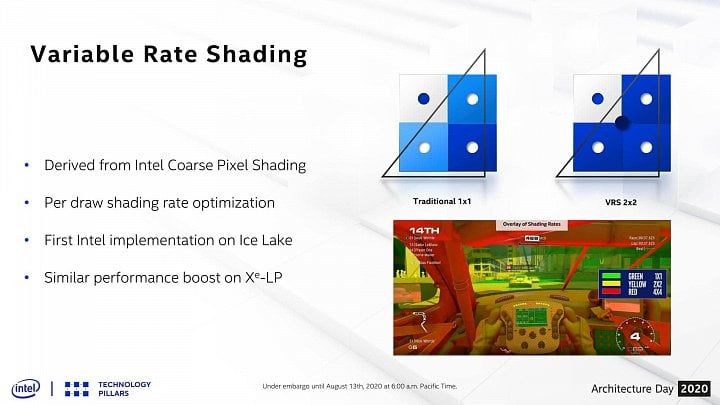

A také Variable Rate Shading, ale jenom ve formě Tier 1 (stejně to má už Gen11), kdežto DX12 (Feature Level 12_2) Ultimate vyžaduje Tier 2. Ten ještě Xe LP neumí a také postrádá nové funkce Sampler Feedback, Mesh Shaders a DirectX Ray Tracing (DXR) 1.1. Ray tracing přinese Intel příští rok v nové architektuře Xe HPG pro samostatná GPU a je možné, že ostatní součásti také.

Jeden Slice z grafiky Xe: +50 % výpočetních jednotek, 2× rychlejší geometrie

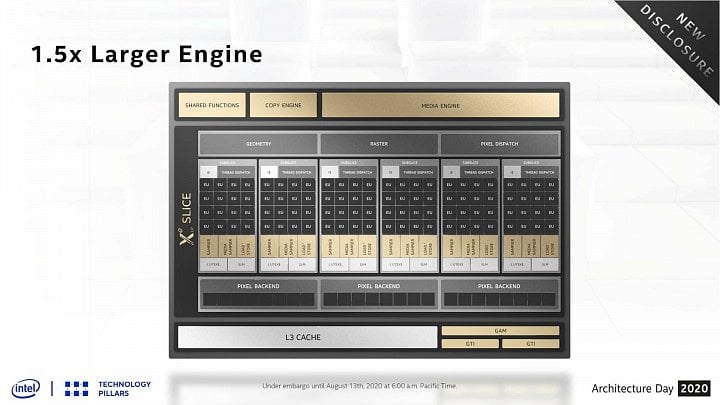

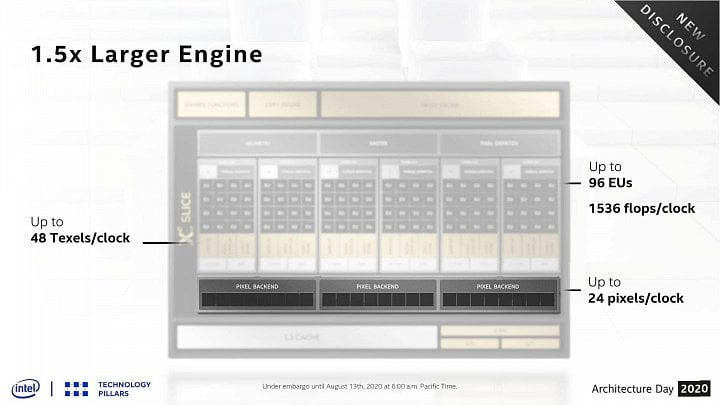

Grafiky Intel jsou tvořené z jedné nebo více „slice“, přičemž slice obsahuje všechny komponenty potřebné pro GPU – frontend, geometrii, výpočetní jednotky, texturovací jednotky i rasterizační jednotky. U Tiger Lake je stejně jako u Ice Lake použitá jen jedna slice, ale architektura Xe LP ji zvětšila o 50 %, takže místo 64 EU (512 shaderů) obsahuje 96 EU (768 shaderů). Texturovacích jednotek je 48 a rasterizačních (ROP) 24.

Intel uvádí, že se u této grafiky počítá s frekvencemi přes 1600 MHz na procesu SuperFin (téměř 50% navýšení taktu proti Gen11/Ice Lake), což znamená výpočetní výkon přes 2,46 TFLOPS při standardní přesnosti FP32. GPU přitom podporuje i výpočty v FP16, kdy je výkon dvojnásobný a celá slice tedy zvládá 1536 (768×2) floating point operací za cyklus.

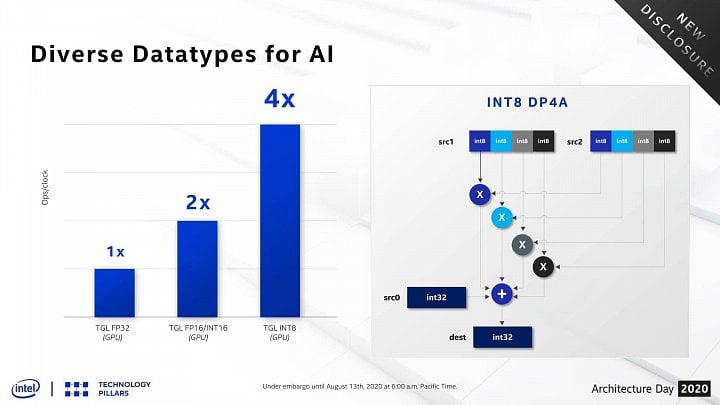

Nově Xe LP také podporuje operace DP4A – IINT8 Dot Product – jde vlastně o operace nad čtyřmi hodnotami INT8. Tyto INT8 operace lze provést čtyři místo jedné FP32, takže „TOPS“ jsou čtyřnásobné proti FLOPS ve výpočtech FP32.

V architektuře Xe LP má vše v této slice o 50% vyšší výkon díky o polovinu většímu počtu jednotek proti 64EU slice v Gen11. Výjimkou je geometrický výkon. Geometrický engine je jeden na slice, takže při rozšíření slice by se poměr narušil sil. Intel proto výkon geometrického enginu rovnou zdvojnásobil: zvládá 2 primitivy/trojúhelníky za cyklus (po cullingu nepotřebných primitiv).

Protože je geometrický engine součástí slice, bude tak v případě většího GPU s vícero slice výkon geometrie škálovat (architektura Gen9 v Skylake měla jeden geometry engine pro všechny slice, což bylo úzké hrdlo).

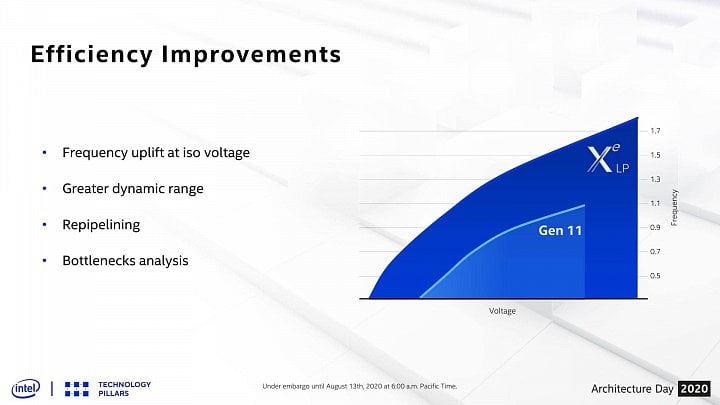

Současně má Xe LP zvyšovat i efektivitu samotných jednotek, takže výkon nebude zvýšen jen taktem a „šířkou“ GPU. Tyto úpravy bohužel Intel příliš nechce prozradit, údajně ale jde o eliminaci různých interních „úzkých hrdel výkonu“.

Článek pokračuje na další straně informacemi o nové architektuře samotných výpočetních jednotek.

Galerie: GPU architektura Intel Xe LP pro samostatná GPU a Tiger Lake

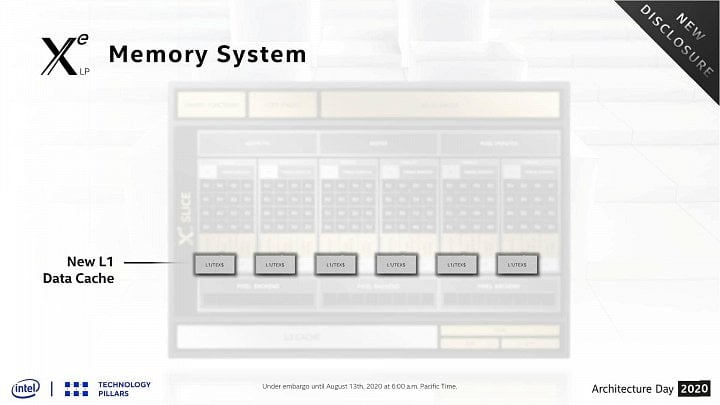

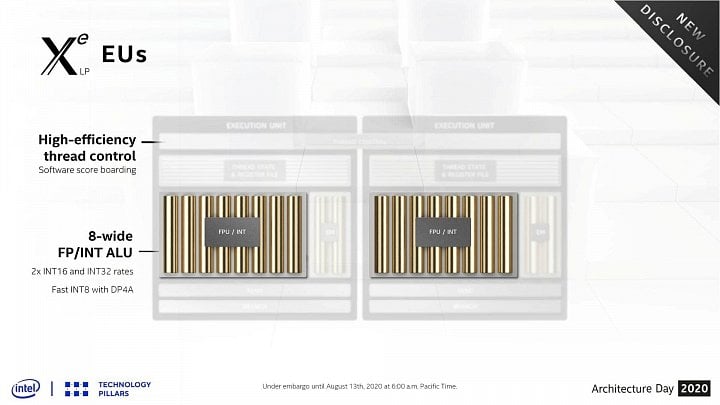

Velká změna bloku EU: ze 2×SIMD4 na SIMD8+SIMD2

Slice jakožto blok se dělí na menší „subslices“. V případě Xe LP neboli Gen12 je těchto subslices šest. Jedna subslice obsahuje 16 EU (128 shaderů) a čtyři texturovací jednotky, které ale dohromady zvládají osm texelů za takt (navýšení na 2×). Každá subslice má údajně vlastních 64 KB L1 cache pro data a textury.

Změna řízení a uspořádání EU mezi Gen11 a Xe LP

Jeden blok EU se v předchozí generaci GPU (Gen11) skládal ze dvou SIMD4 enginů (celkem 8 shaderů/ALU), které sdílely blok pro řízení vláken/dispatch a nebyly stejné – jeden SIMD4 uměl floating-point a integer instrukce, druhý floating-point a komplexní instrukce („Extended Math“).

Minimální šířka wavefrontu či warpu (tak se označuje sada operací, která je jednotkám přidělována) ovšem odpovídala SIMD8, takže podle typu operace se někdy prováděl na dva cykly.

Dva EU jsou teď sdružené dohromady

V Xe LP/Gen12 je toto výrazně přepracováno. Intel sdružil vždy dvojice EU, které mají teď dohromady jen jednu společnou jednotku pro řízení vláken/dispatch, což má být více efektivní. V GPU bude tím pádem méně těchto jednotek, takže se současně zpracovává méně wavefrontů s operacemi.

Současně se změnily samotné shadery v EU. Místo dvou nestejných SIMD4 je v EU nyní jeden SIMD8 s osmi ALU/shadery. Tyto jednotky dokáží zpracovávat floating point i integer operace (všimněte si, že nyní dokáže INT operace zpracovat osm shaderů a už ne jen čtyři, u FP není změna).

Komplexní matematické operace, které byly dříve vedlejšákem druhého SIMD4, teď zpracovává výhradně separátní SIMD2 jednotka s dvěma ALU jen pro tyto operace. Tento SIMD2 je v každém EU jeden, a dá se zřejmě použít paralelně s primárním SIMD8. Ale nemá zřejmě jednotky pro běžné FP/INT operace, takže se počet shaderů z tohoto SIMD2 nesčítá s hlavním SIMD8.

Toto omezení počtu jednotek schopných komplexní matematiky asi více odpovídá charakteru zátěže, který toto GPU bude potkávat, mělo by také asi víc odpovídat tomu, jak jsou výpočetní jednotky vyvážené u architektur Nvidie a AMD.

Díky použití SIMD8 (bloku 8 shaderů) také nyní nejmenší možná velikost wavefrontu (SIMD8) prolétne jednotkami v jednom taktu a nepotřebuje více cyklů. Toto typicky přináší lepší využití výpočetních prostředků, nižší latenci zpracování a nakonec lepší výkon. Stejnou změnu udělalo AMD v architektuře RDNA/Navi (SIMD32 wavefront na SIMD32 jednotce) proti architektuře GCN (SIMD64 wavefront na SIMD16 jednotce, což potřebovalo čtyři cykly).

Galerie: GPU architektura Intel Xe LP pro samostatná GPU a Tiger Lake

Článek pokračuje na další straně informacemi o přechodu z harwarového na softwarový score boarding a změny v uncore grafiky.

Méně je někdy více: Softwarové hlídání dat místo hardwarového pro lepší efektivitu

S řízením vláken pro jednotlivé EU a shadery souvisí ještě jedna změna, která je možná jedna z nejdůležitějších. Dosavadní GPU Intelu používala pro scheduling vláken tzv. hardwarový score boarding. To znamená, že GPU si samo hlídalo, zda mají vlákna k dispozici data, které potřebují, a tudíž je možné je spustit (pokud se vlákno začne vykonávat a data nejsou, je problém). Toto dovoluje začít operace provádět automaticky hned, jak se data dostanou do potřebných mezipamětí/registrů. Ale nevýhoda je, že hardwarová implemenace je velmi komplexní na spotřebu, tranzistory a asi i propojení bloků. Tudíž se z ní stala překážka stojící v cestě zvyšování výkonu.

Nvidia například toto opustila u Kepleru a nechala hlídání těchto závislostí zcela na kompilátoru. Samotné GPU se tedy před těmito hazardy nechrání a kompilátor v ovladači musí hlídat, aby vlákna byla spuštěna až v době, kdy data budou k dispozici. Toto není snadné odladit a asi to může vést k tomu, že scheduling bude konzervativní a ne tak rychlý, jako by mohl být.

Ale z GPU se odstraní hodně komplexity, takže se stejnou spotřebou najednou může běžet na vyšším taktu a obsahovat víc jednotek. V duchu rčení méně je někdy více je tedy toto „zhoršení“ hardwaru a přenesení břemene na software (takový trošku RISC přístup) ve výsledku přínos. U Keplera to vedlo k značnému zvýšení výkonu a efektivity proti předchozí architektuře Fermi s hardwarovým řešením a u Xe LP to pravděpodobně bude mít podobná pozitiva. Znamená to však zásadní změnu z pohledu softwaru a ovladačů, takže Intel měl asi hodně práce s portováním různého nízkoúrovňového kódu.

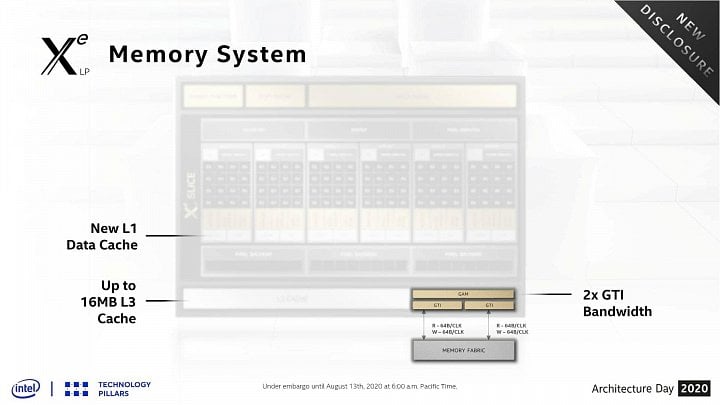

Velká L3 cache grafiky

Jak už bylo řečeno, jednou změnou Xe LP bylo použití větší 64KB L1 cache pro každou subslice. Intel ve schématech neuvádí L2 cache, která dříve existovala, ale zatím má nyní grafika Xe LP velmi velkou L3 cache. Pozor, nemluvíme o separátní L3 cache procesoru, tato je jenom pro GPU. L3 cache grafiky by měla být sdílená pro všechny slice v GPU, pokud by jich bylo víc, a může mít ve velkém GPU kapacitu dokonce až 16 MB. V integrované grafice procesoru Tiger Lake má kapacitu 3,8 MB.

Pro srovnání – výkonné Navi 10 používá v této roli 4MB L2 cache, u Nvidie v generaci Turing má 4MB L2 cache skorohighendové GPU TU104 (GeForce RTX 2080 Super). Takže Intel zde grafice v poměru k její velikosti dává opravdu hodně cache. Navíc je dost rychlá, má propustnost 128B/cyklus, což je při 1600 MHz skoro 191 GB/s.

Integrovaná verze Xe v Tiger Lake bude mít vyšší propustnost

Nejen propustnost cache se zvýšila. V integrované grafice Tiger Lake bude iGPU také mít vyšší propustnost do paměti a do systému. Tyto procesory mají pořád dvoukanálový řadič pamětí (šířka 128 bitů), ale podporují vyšší frekvence LPDDR4X (4266 místo 3733 u Ice Lake). A v pozdějším steppingu se přidá také podpora LPDDR5–5200 (až 86,4 GB/s) pro ještě vyšší propustnost. Toto bude klíčové pro uživení výpočetně výkonnějšího GPU.

Současně se u Tiger Lake také zrychluje připojení do systému. Procesor má dvojnásobnou propustnost na sběrnici mezi jádry (respektive jejich bloky L3 cache, mezi nimiž probíhá komunikace), GPU a řadičem pamětí. Intel totiž zdvojil interní ringbus, CPU má místo jednoho dva. Propustnost je proto dvojnásobná.

Vylepšená komprese barev

Fyzickou propustnost pamětí bude jinak GPU také umět efekivněji využívat. Intel uvádí, že je použitá vylepšená bezeztrátová verze komprese barev a Z-bufferu, která by měla dosahovat lepších kompresních poměrů, takže reálně se využije při přenosech do RAM menší pásmo. Tato komprese je jinak podporována také multimediálním blokem a výstupem na obrazovku, takže i při přenosech mezi nimi se ušetří propustnost (a v noteboocích potenciálně i energie).

Intel DG1 a SG1

Xe LP je jen jedna z připravovaných větví GPU architektury, kterou Intel chystá. A to jakási výchozí nejnižší linie, které bude použitá na méně výkonné samostatné karty a integrované grafiky. Po iGPU v Tiger Lake by tedy měla sloužit ještě v samostatné grafice Intel Xe DG1 (Discrete Graphics 1), která by zřejmě měla mít 128bitové paměti GDDR5.

Tip: První grafická karta Intel Xe ukázána, podívejte se na fotografie vzorku pro desktop

Stejné samostatné GPU bude údajně také osazeno v počtu čtyř kusů na jedné desce na serverové kartě Intel SG1. Jejím smyslem bude poskytnout pro servery s Xeony akcelerované dekódování a enkódování videa. Intel k tomu dříve používal celé procesory pro desktop či notebooky (na PCI Express kartě tak běžely vlastně virtuální PC včetně RAM). Teď bude stačit už jen GPU.

Tip: Intel oznámil Xe HPG: herní GPU pro nadšence s podporou ray tracingu, už v roce 2021

Odvozeně ale budou existovat výkonnější herní grafiky už i s akcelerací ray tracingu (XE HPG), serverové výpočetní karty pro umělou inteligenci (Xe HP) a ještě výkonnější architektura pro superpočítače (Xe HPC), kde se bude používat až „big iron“ přístup s velmi pokročilým pouzdřením, několikačipové heterogenní architektury s integrovanou pamětí a vůbec drahé výrobní postupy, které by v standardním hardwaru asi nebyly možné.

Galerie: GPU architektura Intel Xe LP pro samostatná GPU a Tiger Lake

Zdroj: AnandTech