Předně – ačkoliv se původně očekávala spíše paměť typu DDR3 nebo GDDR5 (a mohlo se spekulovat o tom, od koho by ji Intel odebíral), je nyní poměrně jisté, že půjde místo toho o paměť typu eDRAM (embedded DRAM). Tu používá například IBM ve svých serverových procesorech, u Intelu to však bude čerstvá novinka. O to více, že tento čip si firma (která přestala s výrobou pamětí DRAM v roce 1985) vyvinula sama a bude ho také vyrábět ve svých továrnách, na nejnovějším 22nm procesu s 3-D tranzistory.

Právě o eDRAM vyráběné na 22nm procesu bude totiž Intel v červnu (júni) referovat na konferenci VLSI 2013. Jak již bylo řečeno, výroba eDRAM je pro Intel novinkou a načasování poměrně přesvědčivě svědčí o tom, že své místo najde právě v Haswellu, jenž vyjde ten samý měsíc. Referát Intelu údajně popisuje poměrně zdařilou implementaci paměti eDRAM, byť prý nedosahuje parametrů té od IBM (která ale jde do velmi drahých čipů). Má o něco nižší hustotu a také potřebuje o něco častější obnovování (okolo 100 µs při 95 °C). Buňky této eDRAM jsou mnohem menší než buňky SRAM (používané u pamětí cache) – 0,029 µm² oproti 0,092 µm²; jejich kapacita má být asi 17,5 Mb/mm².

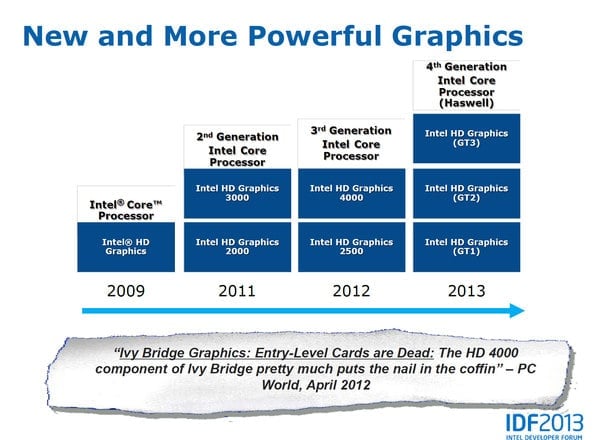

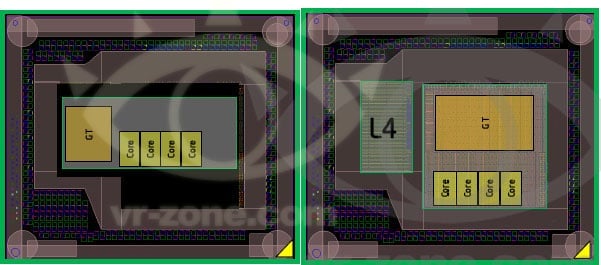

Haswell s integrovanou grafickou eDRAM (Zdroj: VR-Zone)

David Kanter z RWT se na základě různých zdrojů informací domnívá, že velikost této paměti má přesně dle starších zvěstí činit 128 MB a její sběrnice má být široká 512 bitů (a k těmto číslům se přiklání i Anand Lal Shimpi z webu AnandTech). Čip s eDRAM by dle jeho propočtů měl měřit zhruba 70–80 mm², z čehož „úložný prostor“ samotný činí nějakých 60 mm² a zbytek padne na rozhraní a obslužnou logiku. Přenosová rychlost z této paměti by měla činit nejméně 64 GB/s, pravděpodobně to prý bude ještě víc. Intel chce výkonem těchto čipů (Haswell řady H a R) údajně dohnat či pokořit kartu GeForce GT 650M od Nvidie.

Výroba bude dražší než při běžné DRAM (navíc je třeba přihlédnout k tomu, že jde pro Intel o nové odvětví), nicméně Intel prý hodlá za čipy s touto pamětí účtovat přirážku ve výši nějakých 50 USD. Pokud by Intel místo toho vyrobil například čip Atom podobné velikosti, mohl by za něj mít sice větší tržbu, nicméně použití volné kapacity v továrnách na eDRAM mu „hodí“ vyšší marži, neboť jde o méně komplexní čip (méně vrstev spojů například).

Čip eDRAM navíc Intel udá v rámci již existujícího procesoru. Jde vlastně o způsob, jak zákazníkům prodat co nejvíce výrobků z vlastních továren (které je třeba co nejlépe zaměstnat a ne vždy se to daří). Navíc Intel s čipy s HD 5200 může urvat část tržeb, které by jinak šly za diskrétní grafiky ve prospěch Nvidie nebo AMD. Tato strategie, kdy se Intel snaží na sebe stáhnout produkci co největšího podílu součástek v počítači je již zřejmá nějakou dobu – po čipové sadě, grafickém jádře se firma začíná poohlížet například po regulátorech napětí. Díky integrování komponent může Intel zvyšovat „přidanou hodnotu“ svých čipů a bránit se tak tlaku na snižování cen (a tedy marží a tržeb).

V souvislosti s integrovanou eDRAM se objevila ještě jedna spekulace. K této paměti by snad úrý měl mít přístup i procesor (snad přes prstencovou sběrnici), a mohla by tak skutečně sloužit jako velká L4 cache (jak o tom hovořila vůbec první zpráva loni). Jinými slovy, alespoň v určitých úlohách by z její kapacity mohly profitovat i negrafické úlohy běžící na CPU. Tuto možnost prý naznačovala prezentace Intelu na IDF 2013 v Pekingu, nicméně potvrzené to není.

Dle mého názoru by tomuto použití mohly bránit i softwarové problémy, navíc je klidně možné, že paměť není připojená na ringbus, nýbrž přímo ke grafice samotné. Myslím, že použití eDRAM coby obecné L4 cache není příliš pravděpodobné a nejspíše zůstane v říši spekulací – velmi rád se ale v tomto ohledu budu mýlit.

Zdroje: Real World Technology, AnandTech