Strojové učení neboli „umělá inteligence“ (pod čímž se dnes myslí zejména používání neuronových sítí) se v posledních dvou-třech letech stala zlatým dolem pro GPU – zejména od Nvidie – jelikož těmto čipům výpočty neuronových sítí shodou okolností jdou hodně dobře. Nemusí to tak ale být napořád, protože pro toto pole mnoho různých hráčů chystá plně specializované čipy („ASIC“), které by mohly být levnější a efektivnější co do využití energie. Jde například o Google, Intel, ale momentálně se údajně hodlá přidat také enterprise větev firmy HP, která se nyní jmenuje HPE.

HPE prozradilo, že má vlastní program čipů pro AI, které zřejmě budou hodně specifické svou architekturou, ale zároveň také svým využitím. Půjde o výpočetní akcelerátor nazvaný zatím DPE (Dot Product Engine), jehož primárním určením má být využití v extrémních podmínkách například na kosmických zařízeních, tedy třeba v družicích a sondách. Toto použití klade velké nároky na spotřebu čipu nebo velikost celého řešení a HPE údajně vyvíjí vlastní řešení proto, že se v současné nabídce nedá nalézt nic ideálního pro tuto oblast.

DPE zřejmě není úplně typický akcelerátor neuronových sítí, i když tuto úlohu také dokáže provádět. Podle HPE je dobře uzpůsoben pro vektorové maticové výpočty podobně jako třeba Tensor Cores u GPU Volta od Nvidie. Ale nemá pro ně zřejmě být plně natvrdo „zadrátovaný“. Podle kusých informací, které HPE poskytlo, údajně je v nějaké míře rekonfigurovatelný (teoreticky by se tedy mohl podobat FPGA) a může sloužit pro různé typy neuronových sítí, ale zřejmě i pro jiné operace. Prý by měl dokázat akcelerovat třeba i transformace (DCT, FFT) a konvoluce.

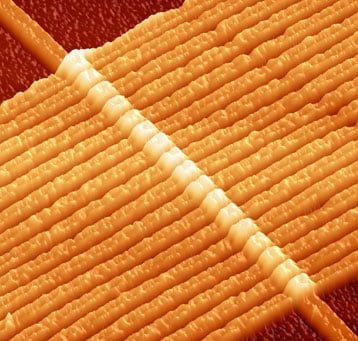

Podle webu Next Platform prozradil Tom Bradicich, který je v HPE manažerem serverů, IoT a sektoru „Converge Edge“, že akcelerátor DPE má v nějaké míře používat memristory. Patrně jde tedy o technologii směřující stejným směrem, jako projekt „paměťové architektury“ The Machine. To hodně ztěžuje snahy předpovědět, čeho by mohla být schopná, a také asi znamená, že uvedení do praxe je spojeno s nejrůznějšími riziky – projekt může být zpožděn, může se ukázat, že jde o slepou uličku a tak podobně.

Čip dokonce údajně z části pracuje analogově, což může být efektivnější než digitální výpočty. Navíc v případě, že bude integrován s nějakým také analogovým senzorem, by to možná mohlo dovolit aplikaci i přímo na vstupní analogová data. HPE údajně počítá s tím, že by tyto čipy mohly fungovat v roli akcelerátoru připojeného k počítači ve stylu GPU, ale také přímo integrované v nějakých zařízeních, kde by data zpracovávaly okamžitě „na místě“, čímž by se ušetřily nároky na propustnost směrem k řídícímu systému.

To, na čem zde HPE pracuje, by tedy asi mohlo být výrazně odlišným přístupem k výpočtům „umělé inteligence“ proti jak GPU, tak ASIC akcelerátorům dneška. Tím pádem by ale také tato technologie mohla mít svoje unikátní vlastnosti a pokud by se skutečně osvědčila (a nebyla enormně drahá), pak by se možná mohla dočkat aplikací i mimo ono úzce vymezené pole čipů pro družice.