Momentálně znamená označení „nejpokročilejší technologie výroby čipů“ 5nm výrobní proces, na kterém už fungují první mobilní SoC jako Snapdragon 888 nebo Apple M1; pro další segmenty jako jsou PC je pořád „bleeding edge“ 7nm čip. Snad příští rok by se mohly objevit 3nm čipy, ale vývoj už pokročil i dál. IBM, které sice prodalo své továrny, ale vývoj a výzkum polovodičových technologií realizuje dál, teď oznámilo úplně první demonstrační čip, který je vyrobený 2nm procesem – pilotní pokus, který prošlapává cestičku k sériové výrobě takového křemíku za pár let.

Vyrobení 2nm čipu či čipů je práce vývojového centra IBM v americkém Albany (stát New York), v němž probíhá výzkum ve spolupráci s privátními i akademickými partnery. Tyto technologie se pak mohou dostat do receptů používaných ke komerční výrobě například v Samsungu, jehož technologie byly historicky spojené s IBM (firmy měly společnou alianci ještě s AMD/GlobalFoundries a Motorolou).

První 2nm čip je zatím zřejmě jen pokusným testovacím čipem, který obsahuje tranzistory a zřejmě buňky SRAM. Nejde ještě o nějaký funkční procesor, který by se přímo dal používat, o to v těchto prvních krocích na nové technologii nejde, ale údajně jsou na něm jak bloky vyrobené s cílem dosáhnout vysoký výkon, tak bloky navržené na energetickou úspornost.

Až 333 milionů tranzistorů na mm²

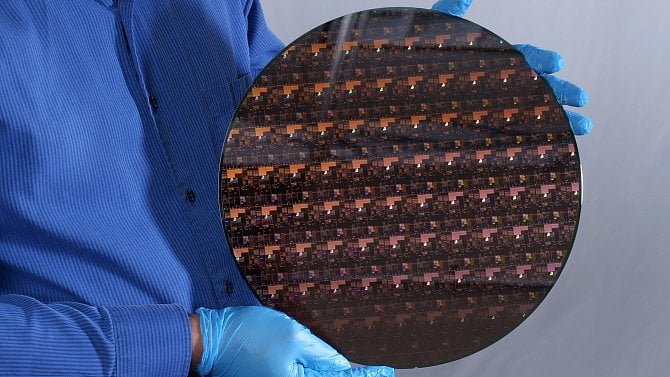

Podle IBM pokusná 2nm technologie, kterou firma demonstrovala vyrobením zkušebního waferu, který můžete vidět na fotkách, umožní až o 45 % lepší výkon proti 7nm čipům (není ovšem řečeno, s jakým procesem se porovnává, zda s tím od Samsungu, nebo od TSMC). Alternativně s ním lze u čipu běžícím na stejné frekvenci/výkonu zredukovat spotřebu až o 75 % oproti čipu vyrobenému 7nm procesem.

Nebylo přímo sděleno, jakou má 2nm čip hustotu tranzistorů, údajně jich obsahuje 50 miliard na ploše velké jako nehet, což však je dost vágní. AnandTechu zástupci firmy sdělili, že se tím myslí plocha asi 150 mm², což by dávalo hustotu okolo 333 milionů tranzistorů na milimetr čtvereční, ale asi to nemusí být moc přesné, protože se vychází ze zaokrouhlených čísel. Pro srovnání: 7nm proces TSMC má dosahovat hustoty až 91,2 milionů na mm², 5nm pak 171,3 mm² (7nm technologie Intelu má prý dosáhnout až 237,18 milionu na mm², což ilustruje, jak číslování Intelu není srovnatelné – ovšem srovnatelné také nejsou metriky, kteýrmi se k těmto číslům dochází).

Je asi dobré říct, že „nanometrová čísla“, která se dnes procesorům dávají jako jména, neodpovídají skutečné velikosti struktur, a to už dlouhou dobu. Jsou volena tak, abyste si mohli vztáhnout vlastnosti technologie k těm starším – k 3nm, 14nm, 65nm procesu a tak dále. Samozřejmě do toho vstupuje i marketing.

Skutečné velikosti struktur jsou proto o dost větší, IBM například uvádí, že rozteč tranzistorů mezi sebou je 44 nm a nejmenší šířka brány tranzistoru je 12 nm. Tyto rozměry jsou výrazně redukované proti předešlým procesům a to je to, co označení „2nm proces“ (v porovnání se starším 3nm, 5nm) má vyjadřovat.

Tranzistor s více nanodestičkovými kanály

Tranzistory čipu už nejsou dnešního typu FinFET, IBM podle fotografií z mikroskopického řezu implementovalo tranzistory, u nichž je kanál tvořen nanodestičkou s bránou okolo celého jejího průřezu – respektive, brány jsou v tranzistoru nad sebou tři, pro zlepšení vlastností. Jde o strukturu, která se také nazývá MBCFET (Multi-Bridge Channel Field Effect Transistor) nebo GAAFET (Gate All-Around FET). Výška tranzistoru s těmito třemi vrstvami nanodestičkového kanálu je 75 nm, ale mezi jednotlivými destičkami je dělící výplň jen 5 nm. Při výrobě byla použitá expozice pomocí EUV záření.

Podobné tranzistory chystá Samsung pro svůj 3nm proces, TSMC je má nasadit až později, zřejmě také na 2 nm. IBM uvádí, že vrstva kovových spojů pak zase byla také vyrobená pomocí EUV, a to pro všechny kritické vrstvy.

Tři roky do reálného nasazení?

Před časem jinak IBM bylo také první firmou či institucí, které se podařilo vyrobit čip 7nm procesem (2015) a poté také první 5nm čip (2017). Na tom IBM také jako první demonstrovalo tranzistory typu GAA-FET. Mimochodem všimněte si, že tyto zářezy na pažbě předcházely každý o tři roky dobu, kdy se reálně dostal na trh první čip s danou technologií, i když vyvinutou jinde (pro 7nm i 5nm proces to byly čipy od TSMC v telefonech Applu, který má pro agresivní nástup nové technologie nejlepší finanční a obchodní podmínky).

Na základě toto by se dalo předvídat, že Apple by mohl mít v mobilech 2nm procesory ARM v roce 2024, s Qualcommem, Samsungem a dalšími výrobci mobilních čipů v těsném závěsu. V PC hardwaru třeba od AMD by pak mohlo nasazení přijít až třeba o rok až dva později. Nepůjde nicméně o přesně stejnou technologii, jakou teď použilo IBM. Pro sériovou výrobu si TSMC a Samsung jistě vyvinou i vlastní postupy, i když část může být licencovaná právě od IBM.