Včera jsme psali o tom, že procesory x86 – minimálně ty od Intelu – dostanou rozšíření APX (Advanced Performance Extensions), což je zásadní změna v programování těchto CPU. Intel ale také chystá velké změny v SIMD instrukcích s technologií AVX10, která sjednotí vektorová rozšíření, v jejichž subsetech je teď nepořádek, a také by měla řešit problém big.LITTLE procesorů. Ale hrozí, že to bude na úkor pravého 512bitového AVX-512.

Instrukce AVX10 byly oznámeny spolu s APX, ale nejde o jejich součást, nýbrž o samostatné rozšíření, které je evolucí či modifikací dnešních SIMD instrukcí AVX-512. Použití AVX10 nebude také na APX nijak vázané. O co tedy v těchto instrukcích jde?

AVX10

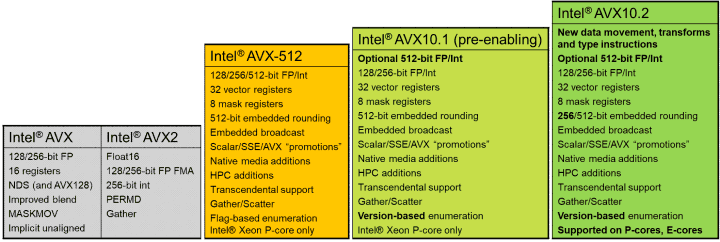

V prvé řadě AVX10 pod sebe balí všechny možné dosud uvedené subsety AVX-512, kterých je mnoho, takže programátoři je budou moci brát jako jednu garantovanou skupinu (nicméně některé, zdá se, nebyly zahrnuty – například instrukce VP2Intersect, přítomné jen v procesorech Tiger Lake). AVX10 ve své první verzi AVX10.1 bude z velké části přejmenování AVX-512, ovšem s jednou významnou změnou – umožňuje totiž, aby místo 512bitových instrukcí procesory mohly pracovat jen s 256 bity (nebo dokonce jen 128 bity).

Už dnes u AVX-512 je to tak, že procesory již podporují verze 512bitových instrukcí AVX-512, které mají jen 256bitovou šířku, nebo 128bitovou. Jsou tedy na úrovni AVX(2) nebo SSEx, ale navíc mají výhody nových funkcí, které přineslo AVX-512 – to poskytuje zejména maskové registry, Gather/Scatter a různé další věci. Také poskytují 32 vektorových registrů, zatímco AVX(2) 16 registrů ymmx a SSEx jen 8 registrů xmmx. Efekt tedy bude podobný jako u APX, které přidává další registry obecným instrukcím zpracovávaným v základních celočíselných ALU.

Tato zlepšení činí SIMD instrukce flexibilnějšími, takže je snazší optimalizovat různé algoritmy – pro programátora, ale také pro autovektorizační kompilátor. Tudíž použití takových polovičních a čtvrtinových verzí AVX-512 je výhodné proti AVX(2) a SSEx – snáze se programuje a také je někdy možné dosáhnout lepšího výkonu, byť hrubá výpočetní kapacita daná počtem jednotek a jejich šířkou se nezmění. Podle Intelu by mělo být možné kód zkonvertovat z SSEx nebo AVX(2) na AVX10 jednoduše rekompilací (i když to nemusí optimálně vytěžit výkonnostní potenciál).

Tyto menší verze instrukcí AVX-512 ale dosud měly jednu zásadní slabinu. Procesory nyní nikdy nepodporují jenom je. Vždy je to současně spojeno s tím, že v procesoru jsou přítomné plné 512bitové registry AVX-512 (zmmx), a to zároveň znamená podporu celého základního AVX-512. Intel tak nepodporuje poloviční 256bitové instrukce AVX-512 na malých jádrech E-Core, která proto umí jen AVX2. A jak známo, to pak vedlo k nutnosti vypnout AVX-512 i na velkých jádrech.

AVX10 toto změní – bude fungovat už i jen s 256bitovými registry, kterých ale bude 2× více než u 256bitových registrů AVX (ymmx). Pokud procesor bude mít jen takto široké registry a SIMD jednotky, bude pořád moci používat ony poloviční verze instrukcí a bude moci avizovat podporu AVX10. Dokonce by to mělo být tak, že by měla být možná i jen podpora čistě 128bitová, což se ale v dohledné době možná používat nikde nebude.

(Skoro) AVX-512 i pro big.LITTLE procesory

Intel jinými slovy osamostatnil 256bitovou verzi instrukcí AVX-512, které se budou moci používat i tam, kde 512bitové plnotučné instrukce nikoliv. A to budou budoucí big.LITTLE procesory Intelu. AVX10 v 256bitové verzi bude totiž podporované na „malých“ (i když ve skutečnosti spíš sedí středních) efektivních jádrech E-Core. A díky tomu bude možné zapnout podporu AVX10 také na velkých jádrech P-Core.

Ovšem ta také dostanou jen 256bitovou verzi. Bude to tedy u nich degradace potenciálního výkonu proti ideální původní podpoře plnotučného AVX-512, ale v kruté praktické realitě je to zlepšení, protože v hybridních CPU se to nedalo využít, zatímco nyní 256bitové AVX10 půjde, a bude tedy zlepšovat výkon v mnohovláknových aplikacích.

512 bitů už jenom na Xeonech

AVX10 ale bude nadále umožňovat i 512bitovou verzi, která bude plně ekvivalentní dnešnímu AVX-512 schopnostmi i výkonem. Jenže tato podpora je na rozdíl od podpory 128bitových a 256bitových instrukcí nepovinná, volitelná. Intel sdělil, že tyto instrukce budou podporované jen na procesorech, které budou mít samá velká jádra (P-Core). Znamená to patrně, že budou jenom na Xeonech.

Toto pak má pokračovat i v budoucích verzích instrukcí AVX10. První verze AVX10.1 má zřejmě být poprvé exponována pro uživatele na procesorech Xeon Granite Rapids, které budou mít onu volitelnou 512bitovou podporu. Tato verze je taková první zaváděcí, v podstatě představující jen přejmenování AVX-512. Až následující verze AVX10.2 reálně přinese procesory, které budou mít jen užší verze těchto instrukcí, a až tato verze se tedy objeví v oněch big.LITTLE procesorech pro PC. Zatím nevíme, zda to bude v architektuře Arrow Lake, Lunar Lake, nebo v jaké přesně generaci. V AVX10.1 zřejmě ještě nebudou úplně všechny funkce nabízené u 512bitových instrukcí replikované také na 256bitových (jde o dílčí věci, dané detaily toho, jak jsou instrukce kódované, například funkce „embedded rounding“). Toto bude u AVX10.2 již dořešené. A také má AVX10.2 už přinést některé zase nové operace, které v AVX-512 ještě nebyly.

Inovace, nebo kolotoč problémů, které si Intel sám zavinil?

Oproti APX není tedy AVX10 až taková velká věc, jde spíše o změnu kódování instrukcí a uvolnění některých dříve existujících (ale ne fundamentálně daných, spíše arbitrárních) omezení. A lze říci, že místo nějakých inovací a nových nápadů se zde Intel v podstatě jen potýká s problémy, které si předtím sám nadělal svou koncepcí hybridních (big.LITTLE) procesorů míchajících jádra P-Core a E-Core. Také zatímco u APX se alespoň na první pohled zdá, že jde o evidentně dobrý a přínosný nápad, u AVX10 se přinejmenším vkrádají pochybnosti.

Dá se totiž hned namítnout, že Intel měl lepší možnost. Místo tohoto si mohl prostě dát tu práci a zprovoznit 512bitové registry zmm pro AVX-512 u jader E-Core – jako to AMD udělalo u jader Zen 4 a Zen 4c. Problém by byl vyřešen elegantně a hned, aniž by to přidělalo problémy vývojářům softwaru, kompilátorů a všeho ostatního okolo toho. SIMD jednotky jader E-Core by pořád mohly být užší a zpracovávaly by 512bitové operace ve více cyklech. Ale běžely by na nich stejné instrukce a stejný kód jako na P-Core (a jako na spoustě už existujících procesorů). U P-Core by tedy nemusel být degradován výkon a mohly mít dále plnohodnotné 512bitové implementace. Celkový výkon v mnohovláknových aplikacích by byl ještě lepší.

A co je možná ještě důležitější, programátoři by nemuseli psát zvlášť kód pro 512bitové verze instrukcí a zvlášť pro 256bitové verze instrukcí a integrovat do aplikace obě dvě verze kódu. Přičemž to je už práce navíc ke kódu v AVX2 a nejspíš také SSEx pro starší procesory. AVX10 svým přístupem vytvořilo ještě další fragmentaci navíc, 256bitové operace AVX10 budou muset být v programech opět další codepath navíc. Ti vývojáři, kteří investovali čas do optimalizací založených na instrukcích AVX-512, teď budou mít velkou radost (nebo kupovat procesory od AMD).

Bohužel je tu také možnost, že Intel dokonce bude 512bitové instrukce upozaďovat, a jednou by je dokonce mohl odebrat i z Xeonů. Intel totiž uvádí, že z dnešních instrukcí AVX-512 se stává „legacy“, které bude podporováno „for the foreseeable future“, ale ne nutně navěky. Intel tedy může vývojáře jednou dotlačit k tomu, aby přepsali nebo překompilovali kód na AVX10, a odebrat podporu pro původní AVX-512. I když doufáme, že se to nestane a firma pořád bude v 512bitových instrukcích vidět nějaký přínos (dnes jasně pomáhají procesorům Xeon, byť Intelu možná vadí, že už pomáhají i novějším procesorům AMD).

Ústup od širších vektorových instrukcí lze teď vidět u ARMu. Ten přišel před lety (2016) se SIMD rozšířením SVE a později SVE2 (to přidává možnost práce s integery), které mělo za cíl od šířky vektorového registru abstrahovat a jeho vektory mají šířku až 2048 bitů, přičemž jsou ale zpracovávány mnohem méně jednotkami (rozděleně na mnoho cyklů). Jenže když po letech SVE přišlo v jádrech Neoverse a Cortex, ARM se vrátil k jen úzkým 128bitovým jednotkám SIMD, takže reálně je výpočetní výkon jen někde na úrovni instrukcí NEON. Architektura Neoverse V1 měla jako jediná 256bitové (ale jen floating-point) jednotky, ale další generace V2 je také zmenšila na 128bitové. Nevíme, zda to není přechodné a zda se jednou ARM nepokusí opět být ambicióznější a přinést 256bitové a 512bitové výpočetní jednotky, které by zvýšily výpočetní potenciál tak jako AVX(2) a AVX-512. Zatím to ale vypadá, jako by na to firma rezignovala.

Doufejme, že to nebude celkový směr, kterým se vývoj CPU bude ubírat, protože bychom přišli o jednu z možností, jak zvyšovat výkon procesorů na jedno vlákno, účinnou třeba v multimediálních aplikacích, ale potenciálně i hrách. I když je pravda, že podle některých hlasů je přínos širších vektorů omezený, například podle Linuse Torvaldse je optimum 256 bitů. Nicméně to může být ovlivněno tím, že se méně věnuje takovému druhu softwaru, který ze SIMD nejvíc benefituje – jádro operačního systému má pro ně spíš omezené využití, někdy jde spíše o sekundární aplikace, jako například zrychlení operací MEMCPY/MEMSET pomocí SIMD instrukcí. Asi teď nelze říct o moc víc než ono „uvidí se časem“.

Jednodušší značení a verzování

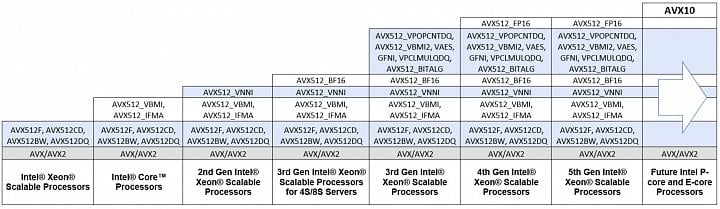

Co je u AVX10 ale poměrně přínosné, i když se to netýká přímo fungování křemíku, je změna v tom, jak se budou chovat další rozšíření. Část negativních postojů k AVX-512 byla způsobena i tím, že tato instrukční rozšíření jsou fragmentována na velký počet subsetů, kde každý má vlastní individuální flag, který programátor musí detekovat. A bohužel je to tak, že různé procesory přinášely další nová rozšíření, ale také u nich někdy chyběla některá předchozí, takže to, jakou sestavu instrukcí AVX-512 určitý procesor podporuje, vytvářelo docela složité grafy (je pravda, že toto vzniklo hlavně kvůli Xeonům Phi).

Takto postupně narůstal počet různých sad instrukcí AVX-512. V rámci AVX10 se přejde na číselné verzování a chaos bude o hodně menší

I AVX10 bude v budoucnu asi nabalovat nová rozšíření, ale Intel uvádí, že v nich bude větší pořádek. Nové přídavky budou označeny číselným verzováním (tedy například AVX10.2, AVX10.3…). A do budoucna má platit, že vyšší číslo vždy bude zahrnovat všechny podmnožiny, které byly v předchozích nižších verzích. Nemá se tedy stát, že novější CPU nějaký kus instrukcí přidá, ale jiný zase odebere, a pro programátory bude snazší detekovat, jaké instrukce CPU umí a zvolit na základě toho v kódu správnou verzi SIMD funkcí.

Podpora u AMD: zatím nejsou informace

Jak už bylo řečeno, AVX10 se chystá nejdříve v procesorech Granite Rapids a poté zejména v zatím neupřesněných procesorech Core pro notebooky a PC. Zatím nevíme, kdy a případě pokud vůbec je převezme AMD. To velkou většinu nových instrukcí vymyšlených Intelem přejímá (což dává smysl vzhledem k tomu, že Intel má dominantní pozici na trhu). Neplatí to úplně vždy, například TSX a SGX se v procesorech AMD neobjevily (je pravda, že zrovna s nimi byly stále se opakující problémy).

V tomto případě snad není s podporou AVX10 – i třeba paralelně s dosavadním AVX-512 – příliš velký problém, takže by je AMD mohlo akceptovat. Ale protože Intel má coby autor náskok v implementaci, asi se v Ryzenech a Epycích objeví až roky po Intelech.