Minulý týden Intel pořádal akci nazvanou Architecture Day 2018 a odhalil řadu plánovaných novinek, zejména architekturu 10nm procesorů Ice Lake, které mají konečně vyjít koncem příštího roku. Těch odhalení ovšem bylo víc. Jedno z menších, ale hodně zajímavých je první procesor Intelu, který zkombinuje architekturu velkých procesorů „Core“ s jejich širokými výkonnými jádry a Atomy s jejich pomalejšími a menšími, ale úspornějšími jádry. Oficiálně se nám potvrdily zprávy, že Intel chystá vlastní variaci na heterogenní vícejádra, kterým ARM začal před lety říkat big.LITTLE. A tento procesor je navíc hodně speciální svým způsobem výroby: jde totiž o 3D vícečipové pouzdro se zatím asi nejpokročilejší MCM technologií.

Lakefield: Ice Lake a Atom v jednom

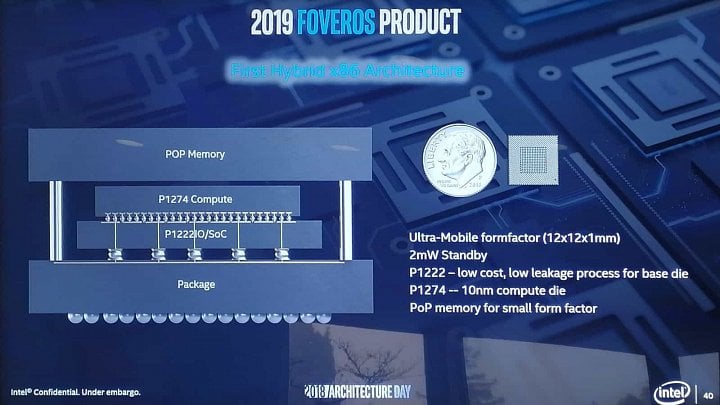

Intel procesoru, o němž je tu řeč, zatím nedal oficiální jméno, ale podle starších neoficiálních zdrojů má snad kódové označení Lakefield (což v sobě příznačně spojuje slova používaná v kódových jménech velkých CPU a Atomů). Procesor bude vyráběn 10nm procesem a měl by podle Intelu být uveden v roce 2019.

Pětijádro 4+1

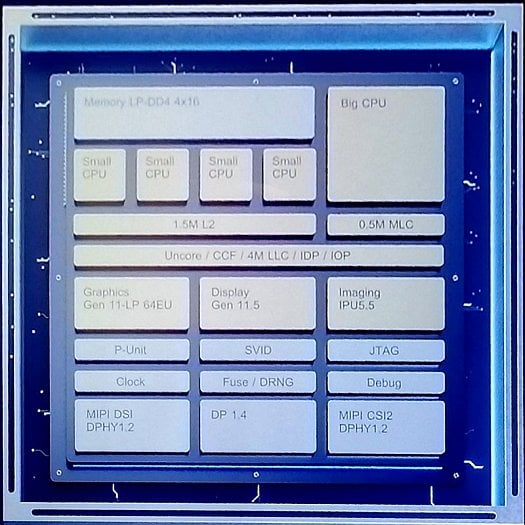

Konfigurace bude hodně atypická. Jde sice o mobilní čip podobný Atomům, ale skládá se ze dvou čipů – CPU a čipsetu, nejde tedy o čistý SoC. CPU část má nečekaně (i když se o tomto faktu objevily drby) lichých pět jader. Je totiž integrována čtveřice jader Atom, zřejmě architektury Tremont, což je příští generace jader Atom na 10nm procesu. Velké jádro bude jenom jedno jediné. Má jít o architekturu Sunny Cove, tedy o stejné jádro, jaké použijí velké procesory Ice Lake. Zatímco u ARMů byla vždy jader „big“ aspoň dvojice, Intel tak neučinil, snad kvůli ploše čipu nebo spotřebě.

Přítomnost jádra Sunny Cove/Ice Lake má tedy za cíl evidentně jen a pouze jednojádrový (jednovláknový výkon), který by mohl být konkurenceschopný s desktopovými CPU (ovšem to samozřejmě bude záviset na jeho frekvenci). Na všechno ostatní bude SoC mít malá jádra Atom. Bude asi hodně zajímavé porovnat toto zvláštní pětijádro s čipem, kde by ona malá jádra byla nahrazená třeba jenom jedním velkým jádrem navíc. Bude také zajímavé vidět, jak Intel vyřeší problém s tím, že malá jádra neumí všechny instrukce těch velkých. Je možné, že kvůli tomuto bude například nutné u jádra Sunny Cove deaktivovat instrukce AVX až AVX-512, pokud je Tremont neimplementuje. Jinak by nebylo možné mezi nimi migrovat procesy.

Schéma heterogenního procesoru Intel s jádry Tremont a Sunny Cove/Ice Lake, prosinec 2018 (Zdroj: AnandTech)

Schéma heterogenního procesoru Intel s jádry Tremont a Sunny Cove/Ice Lake, prosinec 2018 (Zdroj: AnandTech)Čip by měl mít poměrně slušné GPU, bude totiž přítomná grafika architektury Gen11 s 64 EU – tedy se stejným počtem výpočetních jednotek jako grafika GT2 v Ice Lake, kde má mít v mobilních čipech až přes 1 TFLOPS výkonu. Ovšem zde bude použita varianta „LP“, což znamená o dost nižší takty (dnes například Atomy mají maximální boost jen na 700–800 MHz proti 1,1–1,25 GHz u desktopových a notebookových procesorů). Výstup bude podporovat MIPI DSI a DisplayPort 1.4 a další rozhraní, přítomný bude blok pro zpracování obrazu z kamery a další věci obvyklé u mobilních čipů.

Procesor bude mít paměťový řadič LPDDR4 se čtyřmi 16bitovými kanály. Tím bude možné použít čtyři čipy LPDDR4, ale celkem bude šířka pamětí jen 64 bitů jako u jednokanálové DDR4. Celkem komplikované to bude se systémem mezipamění cache. Jádra Atom budou sdílet 1,5 MB L2 cache, jádro Sunny Cove zřejmě bude mít vlastní privátní 512KB L2 cache, nad čímž pak ještě bude 4MB L3 cache (či „LLC“ cache) sdílená pro vše.

Technologie Foveros: 3D čiplety u Intelu

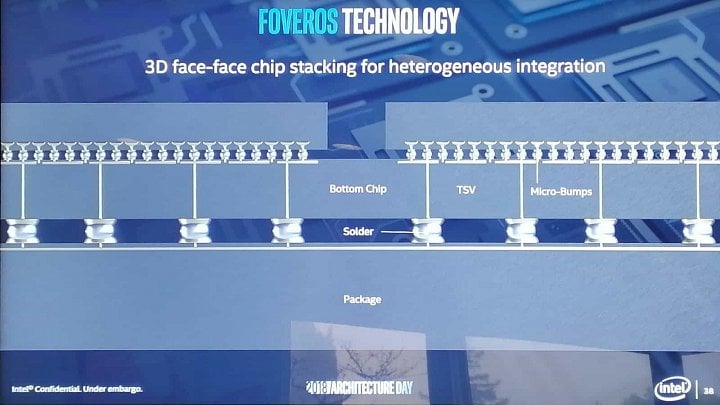

Nakonec ještě větší překvapení než počet jader nebo big.LITTLE ale je, že tento „SoC“ je tvořen dvěma propojenými čipy, respektive „čiplety“. Kromě 10nm části s CPU a GPU je totiž použit ještě druhý čip vyráběný na starším a levnějším procesu, který implementuje funkce čipsetu, takže samotný 10nm čip bude moci být malý. Nemusí zde ale jít jen o cenu, tato technologie umožňuje vyladit procesy použité pro horní a spodní vrstvu na odlišné parametry v rámci stejné generace technologie, například použít pro CPU výkonnou a pro čipset úspornou variantu procesu.

Tyto dvě části tak budou vyráběné odlišným postupem, ale hlavně je na tom zajímavá jejich integrace. Nejsou totiž jen na společném substrátu (to už má Itnel dlouho u procesorů řady U/Y), jsou naštosované na sobě. Díky tomu mohou být propojené velmi malými spoji, které by měly umožňovat velmi rychlou a velmi energeticky úspornou komunikaci mezi oběma polovinami „SoC“ Lakefield. Schopnosti tohoto propojení by měly být ještě lepší, než při použití křemíkového interposeru.

V podstatě jde totiž o to, že funkce druhého I/O čipletu (čipsetu) a interposeru byla spojena do jednoho. Intel využil toho, že čipset má nízkou spotřebu a tedy může být ve spodní vrstvě, a zabudoval ho přímo do křemíku, který by jinak byl pasivním interposerem obsahujícím jen kovové spoje. Jde tedy o čipletové řešení pokročilejší než u čipletů u AMD (u procesorů Epyc 2). Skrze tuto spodní část jsou vedené kontakty z horního čipu do substrátu dole pomocí kanálů TSV.

Schéma procesoru s pouzdřením Foveros, kde jsou v horní vrstvě dva výpočetní čiplety (Zdroj: AnandTech)

Schéma procesoru s pouzdřením Foveros, kde jsou v horní vrstvě dva výpočetní čiplety (Zdroj: AnandTech)Intel tuto technologii nazval Foveros a Lakefield je její první aplikací či testovacím čipem. Ovšem v budoucnu by měla být použita právě v serverech, kde Intel také zřejmě začne vyrábět čipletové či MCM procesory. Také v těch by tedy mohly přijít 10nm CPU čiplety v horní vrstvě a úspornější 14nm I/O a čipset integrovaný v interposeru pod nimi. V případě Lakefieldu ještě navíc bude možno osadit paměť LPDDR4 nahoru na horní vrstvu pomocí pouzdření PoP (package on package), což ale už není nic nového, toto se používá běžně. V serverech to kvůli vyšší spotřebě a potřebě vyšších kapacit asi nehrozí.

Srovnání technologie Foveros a pouzdření s můstky EMIB, což je varianta křemíkového interposeru (Zdroj: AnandTech)

Srovnání technologie Foveros a pouzdření s můstky EMIB, což je varianta křemíkového interposeru (Zdroj: AnandTech)2mW spotřeba

Pokud se ptáte, jaký smysl bude big.LITTLE procesor Lakefield mít kromě toho, že na něm byla technologie Foveros poprvé vyzkoušena v praxi, není odpověď zatím úplně jasná. Těžko říci, zda jde o kompletní náhradu dnešních lowendových procesorů, v nichž jsou jen jádra Atom, nebo zda ho Intel chce mít jako nějaký výkonnostní mezistupeň. Pravděpodobně bude cílem hlavně mobilní oblast, Intel totiž avizuje "ultramobilní" provedení s rozměrem pouzdra jen 12 × 12 mm. Podle oficiálního sdělení vzniklo toto řešení na přání nejmenovaného konkrétního zákazníka, jenž chtěl procesor s vyšším (jednovláknovým) výkonem než mají jádra Atom, ale zároveň jejich úsporné charakteristiky. Požadována byla údajně spotřeba ve standby pouhé 2 mW, což asi s deriváty velkých procesorů pro notebooky nebylo možné. Intel tedy zřejmě navrhl Lakefield jako hybrid, kde je většina infrastruktury postavena jako u úsporného SoC. Jen je dovnitř přidáno ono jedno velké jádro, které se během nečinnosti prakticky kompletně vypne a izoluje od napájení, a spouštěno je jen když je třeba.

Zda je tímto zákazníkem nějaký výrobce počítačů, tabletů či mobilních zařízení, nebo naopak přišel z oblasti embedded, není bohužel jasné. Nevíme proto ještě, zda se s Lakefieldy budeme mít tu čest normálně setkávat, nebo zda se třeba objeví jen ve sféře IoT nebo v jiných „schovaných“ umístěních. Podle Intelu ale Lakefield nebude produktem na objednávku jen pro onu konkrétní firmu, má být naopak běžně nabízen v ceníku i dalším zákazníkům. Tudíž by se v nějakém tabletu či podobném přístroji snad mohl objevit. Jak už bylo řečeno, uvedení Lakefieldu má být příští rok, takže na trhu by se pak asi mohl objevit někdy v průběhu roku 2020.

Obzvlášť zajímavý bude ovšem Lakefield v tom případě, pokud se tyto hybridní mixy dvou architektur osvědčí a začnou se v osobních počítačích s procesory x86 používat šířeji. Možná, že jednou se několik pomocných malých jader stane běžnou součástí procesorů pro běžné notebooky a možná i stolní PC...