Architektura Silvermont – jádro

Již nějakou dobu víme, že bude Silvermont vykonávat instrukce konečně stylem „out-of-order“ (jako klasické desktopové procesory nebo třeba VIA Nano a Bobcat od AMD), což by samo mělo přinést masivní zlepšení výkonu. A to i přesto, že jádro ztratí funkci HT (již nebude zpracovávat dvě vlákna naráz). Tato schopnost omezovala nevýhody koncepce in-order, nyní se ale asi již nevešla do „rozpočtu“. Vnitřnosti Silvermontu jsou také stále stavěny na zpracovávání jen dvou instrukcí za takt, stejně jako u staré architektury.

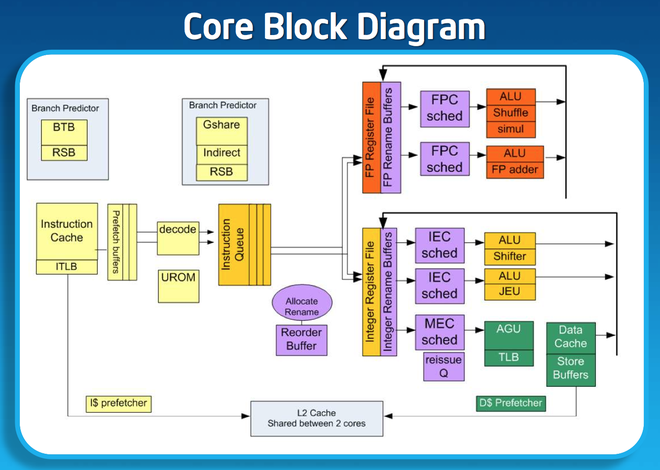

Jak celočíselná část, tak FPU jsou dvouportové (dvě ALU, dvě AGU), jak můžete vidět na schématu (v tomto ohledu se tedy čip podobá Bobcatu či Jaguaru). Pokud ale máte ve frontě instrukce jak pro ALU, tak pro FPU, můžete teoreticky poslat ke zpracování nárazově čtyři. Dva jsou i instrukční dekodéry, Intel je ovšem poněkud vylepšil, čímž klesl počet instrukcí, které jsou prováděny přes mikrokód, a tedy velmi pomalu. Jak velké jsou změny v samotných výpočetních jednotkách zatím nevíme – minimálně některé instrukce jsou rychlejší nebo mají kratší latenci (mělo by konkrétně jít třeba o celočíselné násobení nebo některé instrukce počítané FPU).

Schéma jádra Saltwell (32nm Atom)

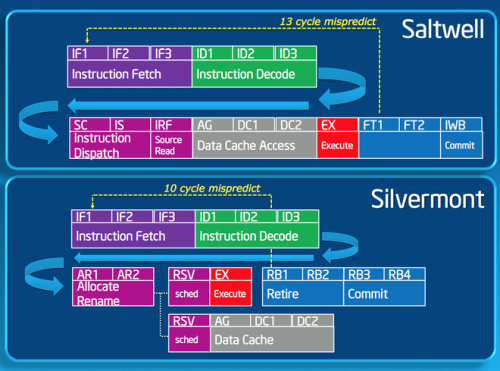

Původní architektura Bonnell měla 16 stupňovou pipeline. V Silvermontu má pipeline 14-17 stupňů (počet kroků závisí na tom, jaký typ instrukce se zpracovává). Pokud nejsou třeba data z cache, lze tři stupně přeskočit, takže cena za špatně odhadnuté větvení klesne ze 13 cyklů na 10. Prediktor samotný by měl být značně posílen a přibude k němu i jednotka pro předpověď nepřímého větvení. Součástí pipeline je také Loop stream buffer, ze kterého lze brát hotové dekódované instrukce, pokud je detekováno vykonávání smyčky (lze tak ušetřit energii neopakováním redundantních kroků).

Pipeline Silvermontu ve srovnání s in-order Atomy

Silvermont bude podporovat o něco více instrukčních rozšíření než staré Atomy – dostane navíc SSE4.1a SSE4.2 a co je možná důležitější, také AES-NI (to už jsme ovšem věděli), neboť šifrování pomocí slabého CPU by jinak bylo utrpením. Přibude i hardwarový generátor náhodných čísel. Samozřejmostí je 64bitový režim, který ovšem Intel může u některých modelů zakázat. Co procesory mít nebudou, jsou 256bitová vektorová rozšíření AVX a AVX2 nebo instrukce FMA3. V tomto ohledu bude mít AMD mírnou výhodu, neboť Jaguar již podporuje i AVX; má nicméně jen 128bitové jednotky SIMD, takže podpora má význam spíše kvůli kompatibilitě, než kvůli výkonu. Intel zase díky vypuštění AVX ušetří množství tranzistorů (procesor nemá 256bitové registry YMM a s nimi spojenou infrastrukturu).

Cache, paměťový subsystém a AGU

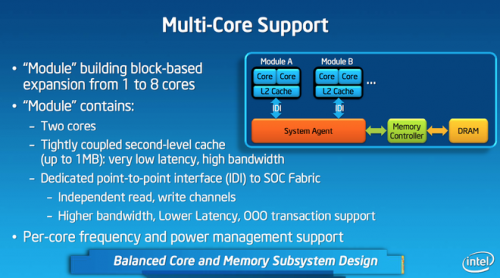

Základní jednotkou čipů bude modul obsahující dvě jádra CPU a L2 cache o velikosti 1 MB, která je mimochodem rychlejší než u Saltwellu (latence snížena o 2 cykly, bohužel ale nevím, s čím se zde srovnávalo). Mezi oběma jádry ovšem až na L2 nedochází k žádnému sdílení zdrojů. L1 cache v jádrech nicméně zůstaly beze změn: 32 KB pro data a 24 KB pro instrukce je asi podle Intelu optimální. Moduly lze dohromady nakupit čtyři, takže maximální počet jader je u Silvermontu osm.

Modul Silvermontu: 2 jádra a L2 cache

Již předchozí generace Atomu měly paměťový řadič na čipu, interně bylo ale vše stále realizováno přes prastarou sběrnici FSB. Silvermont s touto pamětihodností končí a severní můstek, paměťový řadič a moduly již budou přímo propojené normální interní sběrnicí. To by mělo snížit latence a zvýšit propustnost. Doposud totiž integrovaný paměťový řadič kvůli zastaralé koncepci v podstatě nepřinášel zrychlení. Vyšší výkon pamětí bude důležitý zejména pro grafické jádro výsledných čipů SoC.

Načítání dat do registrů a vůbec přístupy do paměti jsou nyní také prováděny mimo původní pořadí (jsou tedy optimalizovány). Za takt dokáží AGU vykonat jedno čtení, jedno uložení či oboje zároveň. Vylepšen byl i „store to load forwarding“ (tedy situace, kdy procesor požaduje z paměti data, která předtím sám zapsal, a je tedy možné se vyhnout čtecí operaci). Pro efektivnější běh Intel zvětšil bufery TLB a Atom bude také přímo podporovat načítání dat nezarovnaných v paměti (včetně 128bitových hodnot, což se bude hodit třeba pro instrukce SSE).

Spotřeba a turbo

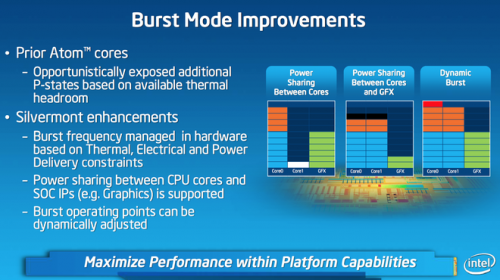

Turbo starších Atomů (bylo-li vůbec dostupné) nebylo příliš sofistikované. Procesor prostě dle TDP omezoval dostupnost vyšších P-stavů. Jádra nemohla v případě potřeby „sníst“ příděl jiných bloků na čipu (například GPU či nečinného jádra CPU), byť by byly vypnuté a energii samy nespotřebovávaly. Silvermont bude mít jako modernější čipy jednotku pro řízení spotřeby. Příděly TDP bude možno „přesouvat“ mezi částmi čipu, při rezervě se bude CPU moci přetaktovat nad běžný takt, a krátkodobě bude dokonce smět přešvihnout TDP, pokud bude teplota čipu dosti nízká, aby byl náhlý přebytek tepla bezpečně absorbován. V praxi by se tato zlepšení mohla projevit například v lepší odezvě operačního systému.

S turbem souvisí ještě jedna věc – jádra Silvermontu mohou najednou běžet na různých taktech, a to i v rámci jednoho modulu. Pokud mají rozdílnou frekvenci dvě jádra v modulu, zůstane společná L2 běžet na vyšší z obou hodnot.

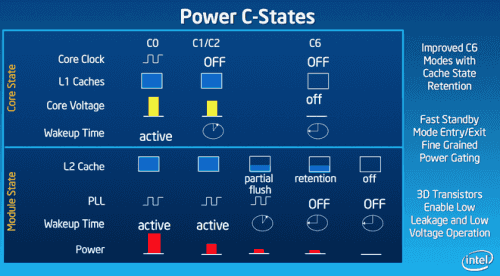

Na (údajně) nízké spotřebě Silvermontu se samozřejmě podepíše 22nm proces s nízkými úniky proudu a dovolující čipu běžet na nižších napětích. Jádro nicméně také přinese různá zlepšení v šetřících funkcích. Power gating by měl být sofistikovanější a také byly zrychleny přechody do a z šetřících stavů (C-stavy).

Silvermont - postupný přechod do C-stavu

Pro přechod do hlubších stavů s nízkým napájením, který trvá obecně déle, má Intel jeden zlepšovák. U těchto stavů je třeba uložit obsah pamětí cache (jinak by byl ztracen), zápis do paměti ale chvíli trvá. Intel jej proto realizuje po částech a jak jsou jednotlivé bloky vyprazdňovány, může přísun energie pomalu snižovat ještě předtím, než je modul a cache odpojen úplně. Jelikož zejména v mobilním zařízení se mezi stavy přechází pořád, mělo by toto opatření mít pozitivní dopad na výdrž baterií.

Závěr

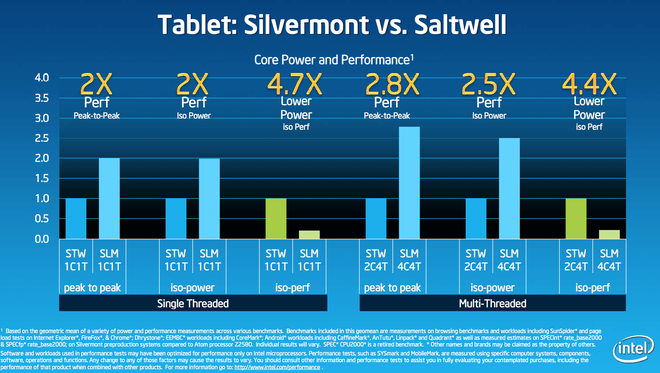

Jaký přesně bude výkon čipů s architekturou Silvermont je záhadou, kterou rozlousknou až benchmarky. Zdá se však, že frekvence jader by mohla povyrůst až někam do okolí 2,5 GHz. Předběžné nástřely zlepšení výkonu na takt zase ukazují na zhruba o 50% vyšší rychlost proti klasickému Atomu. Obojí dohromady už může znamenat dramatický nárůst výkonu. Na jednom vlákně by se dal čekat (velmi zhruba) dvojnásobný výkon, navíc je zde zvojnásobení počtu jader. Pokud se vyvede mobilní varianta 22nm procesu, snad to bude i se snížením spotřeby.

Nová architektura by se mohla dočkat křtu ohněm ještě tento rok – na podzim se chystá uvedení serverových Avotonů a zřejmě i rodiny SoC pro tablety či netbooky s označením Bay Trail. Do telefonů se ale asi Silvermont dostane až začátkem roku 2014.