Snímky čipů, když se k nim dostaneme, typicky bývají výrobci ukázány až po vydání. Ovšem teď se stala zvláštní výjimka a naskytl se určitý pohled dovnitř čipu, který vyjde až na konci tohoto roku nebo dokonce až v tom dalším: serverový Xeon Sapphire Rapids, který by mohl hodně zamíchat kartami a vrátit Intel na technologický vrchol, odkud ho trošku vyšouplo AMD s Epycy 7003 (a vlastně už Epycy 7002).

Je to navíc první procesor Intelu, který přejde na čipletovou stavbu. O to je zajímavější, že se nejen někdo už dostal ke vzorkům, takže jsme před časem viděli delid. Teď už dokonce procesor Sapphire Rapids byl i rozebrán a vyfoceny byly přímo detaily jeho křemíku/křemíků.

Tyto fotky má na svědomí stejný leaker YuuKi_AnS, který publikoval delidovaný procesor a teď se zřejmě rozhodl zjistit, co má Sapphire Rapids uvnitř. Separace křemíku od substrátu a jeho obroušení bohužel není udělaná kvalitně, jak to umí Fritzchens Fritz, takže zatím se nekonají detailní duhové obrázky struktur jádra.

Intel nepoužije IO čiplet

Na křemíku toho není vidět moc, ale i z tohoto už jdou poznat zajímavé věci. Za prvé: vypadá to, že Sapphire Rapids není vrstvený jako hybridní LakeField. Jak jsme viděli na předchozích fotkách, procesor tvoří čtyři prakticky čtvercové čiplety, které by měly být 10nm a obsahovat jádra CPU. Spekulovali jsme ale, že by to Intel mohl vylepšit tím, že by ještě pod nimi byl třeba 14nm IO čiplet, který by ještě navýšil množství křemíku, které celek může využívat. To ale fotka rozšmelcovaného procesoru nepotvrdila, pod CPU čiplety žádný další IO čiplet není.

To znamená, že čipletové řešení není jako u Epycu 7002 a 7003, které mají centrální IO čiplet a v něm všechny řadiče pamětí a PCI Express, což procesor do značené míry integruje dohromady. Místo toho to vypadá, že čtyřdílný Sapphire Rapids může být spíš trošku jako Epyc 7001 „Naples“, tedy že v každém ze čtyř CPU čipletů budou dva kanály DDR5, případně řadič pro pravděpodobně jeden paklík paměti HBM2e a 20 z celkových 80 linek PCI Express 5.0, kterými má CPU disponovat. Možná si vzpomenete, že v roce 2017 se Intel první generaci Epycu ve svém marketingu poškleboval, že ji drží dohromady lepidlo. Paradoxně teď Intel předvádí velmi podobné řešení.

Můstky EMIB

Naštěstí pro Intel tu možná je jedno zásadní zlepšení. Epyc 7001 měl CPU čiplety propojené jen obyčejně přes klasický substrát, což zřejmě limitovalo rychlost, latenci a energetickou efektivitu těchto propojení, architektura samotná pak také fungovala de facto jako čtyři propojené procesory místo jediného, což není optimální. Sapphire Rapids má technicky pokročilejší propojení čipletů: EMIB.

Na spodcích sejmutých křemíků jsou vidět malé obdélníčky po hranách, kde k sobě čiplety budou přiléhat. Kupodivu nejsou úplně symetrické – v jedné ose má čiplet obdélníčky tři, v druhé ose jen dva. Tyto obdélníčky jsou místa, kde je CPU čiplet připájený k můstku EMIB, jenž je uložen v pod křemíkem v substrátu. Tyto můstky EMIB jsou samy křemíkovými čipy a jde vlastně o zmenšený – a tím mnohem levnější – křemíkový interposer. Tyto můstky přesahují okraj čipletu a doslova přemosťují jeho hranice do vedlejšího čipletu (na který jsou také připájené), jak je na fotce substrátu vidět.

Když komunikace mezi CPU čiplety půjde místo substrátu skrze tyto můstky (a dvě sady pájených kontaktů), mělo by to umožňovat rychlejší a energeticky efektivnější komunikaci, snad bude i nižší latence při přechodu mezi čiplety. V tomto by tedy řešení Intelu mohlo být lepší, než „lepidlo“ od AMD. Snad se také Sapphire Rapids bude schopen chovat jako jedno monolitické CPU, místo aby v praxi měl povahu čtyř CPU/čtyř NUMA uzlů. Ale to teprve uvidíme.

Z postavení můstků a toho, že není použitý větší podkladový IO čiplet, ale asi také vyplývá, že budou propojené vždy sousední CPU čiplety, chybí propojení křížem, takže diagonálně bude muset komunikace jít na dva „hopy“ přes společného souseda čipů. Nicméně to by mohlo být vysvětleno tím, že je použitá propojovací logika typu mesh – o tom za chvíli.

Propojují EMIB přímo mesh sběrnici procesoru?

Velmi zajímavé je na těchto fotkách to, že na CPU čipletech se zdá být patrné členění na dvacet sektorů v mřížce po 4 × 5 obdélnících. Serverové procesory Intelu používají mesh propojení a členění, pro které je toto charakteristické. Asi to tedy znamená, že Intel toto zachová na úrovni jednotlivých CPU čipletů. Je otázka, zde bude celý slepenec tvořit jeden unifikovaný mesh, nebo čtyři meshe s nějakým zprostředkovaným propojením.

Rozebraný procesor Sapphire Rapids s čiplety. Tmavé bloky ukazují polohu můstků EMIB (Zdroj: YuuKi_AnS)

Rozebraný procesor Sapphire Rapids s čiplety. Tmavé bloky ukazují polohu můstků EMIB (Zdroj: YuuKi_AnS)Možná by to mohla být ta lepší varianta, tedy unifikovaný mesh: Jak bylo zmíněno, na jedné straně totiž čiplety mají jen dva můstky EMIB, zatímco na druhé tři. Vypadá to, že ona hrana (na fotce horizontální) s dvěma EMIB odpovídá čtyřem dlaždicím/blokům (sloupcům) v rámci mřížky mesh. Naopak (na fotce vertikální) hrana s třemi můstky EMIB by zdá se mohla korespondovat s pěti řadami dlaždic/jader. Možná tedy na komunikaci dvou dlaždic se sousedy ve vedlejším čipletu je vždy třeba jeden EMIB, a na hraně s pěti dlaždicemi proto nestačí dva a musí přijít třetí.

Proto by mohl procesor tvořit ucelený mesh. Kdyby totiž tvořil mesh každého čipletu jen do sebe uzavřený celek a tyto celky byly teprve propojeny nějakými rozhraními představujícími další úroveň komunikace, asi by na každé strany byl stejný počet těchto komunikačních kanálů. Nu, uvidíme později, jestli jsme se z touto interpretací trefili.

Počet jader: až 72? Nebo je v matrici 4×5 něco jiného?

Ono rozdělení čipletu na 4×5 bloků má implikaci pro počet jader. Bloků je se čtyřmi čiplety celkem osmdesát, ale uniklé specifikace mluví o tom, že Sapphire Rapids má mít „jen“ 56 jader. Je možné, že Intel klame tělem a ve skutečnosti chystá jader víc?

Více: Už unikly detaily next-gen Xeonů Sapphire Rapids: 56 jader, 350 W, 64 GB HBM2e uvnitř

Každý blok nebude ovšem jádro, protože víme, že Intel část bloků v meshi matrici nepoužívá pro jádra, ale pro řadiče paměti. Je pravděpodobné, že na DDR5 asi padne aspoň jeden blok v každém čipletu. Dále je možné, že blok bude zkonzumován i na konektivitu PCI Express 5.0, je ale otázka, kolik jich toto sebere. Pokud by stačil jeden blok v každém čipletu, pak by pořád zbývalo 4×18 bloků, tedy CPU Sapphire Rapids by mohlo mít až 72 jader.

Nicméně nevíme, zda třeba Intel potřeboval další bloky ještě na jiné věci, jako je řadič pro paměti HBM2e, které některé verze těchto procesorů prý budou mít integrované (procesor na fotkách je nemá). Nebo pro nějakou řídící jednotku, funkcionalitu čipsetu nebo specializovaný akcelerátor. Počet 56 jader by znamenal, že jen 14 z 20 bloků obsahuje jádro CPU a šest (24 na celém CPU) dalších má v sobě něco jiného.

U procesorů Ice Lake-SP se 40 jádry má mimochodem mesh matrice tvar 8×6 a jen osm pozic je spotřebováno na něco jiného, než jádro CPU. Na druhou stranu má ale také tento čip hodně dalších částí okolo této matice, kdežto Sapphire Rapids tolik periférie navíc nemá. Zde tedy budeme asi netrpělivě vyhlížet další informace.

YuuKi_AnS jinak takto zničil i další procesory, mimojiné Xeon Phi s integrovanou pamětí HMC a zdá se také čínský HiSilicon KunPeng (viz odkaz na zdroj), u těch ale nejsou snímky trosek tak zajímavé.

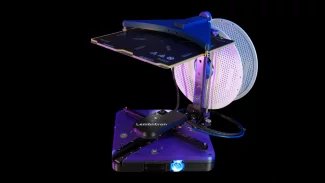

Galerie: Vzorek procesoru Intel Xeon Sapphire Rapids s čiplety a FPGA

Zdroj: Bilibili