Včera jsme psali o fotografii budoucího serverového procesoru Sapphire Rapids od Intelu, což bude derivát 10nm architektury Willow Cove/Tiger Lake pro servery, s vysokým počtem jader a instrukčními rozšířeními (AMX, výkonnější AVX-512). Sapphire Rpids vypadá hodně zajímavě, protože by mohl eliminovat deficit ve výkonu a aefektivitě, který teď Xeony od Intelu mají na Epycy od AMD.

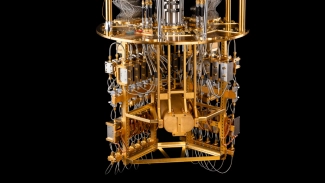

Psali jsme, že tyto procesory ba mohly mít čipletovou konstrukci, tedy že by Intel opustil monolitické řešení, na které dosud spoléhal. A toto se teď opravdu potvrdilo. Teď totiž máme od čínského zdroje další fotografie, na nichž je stejný procesor delidován a jsou odhaleny jeho pozoruhodné vnitřnosti.

Opravdu čiplety

Podle fotek, které YuuKi_AnS opět ukázal na Bilibili, Intel stejně jako AMD naskočil na vlak čipletového lepení procesorů z více kusů křemíku. Ale technologii má dost možná modernější. Na fotce jsou vidět čtyři zhruba čtvercové čiplety, které jsou ovšem nezvykle napasované jeden vedle druhého s jen nepatrnou spárou (zdá se, že něčím vytmelenou) mezi sebou.

Lze tušit, že by mohlo jít o důsledek nějakého pokročilého pouzdření, tyto kusy křemíku by nejspíš mohly být mezi sebou propojené křemíkovými můstky EMIB. Ty se funkčně podobají interposerům používaným s pamětí HBM2, ale snad by to mělo vycházet levněji. Interposer nebo EMIB by asi mohly výrazně omezit energetické ztráty a zhoršení latence, kterou způsobuje komunikace mezi čiplety u procesorů AMD, které pokročilé pouzdření nemají a spoléhají se na obyčejný substrát.

Je také možné, že Intel použil technologii Foveros a pod CPU čiplety viditelnými na fotce je ještě schovaný samostatný „IO čiplet“, jaký mají Epycy 7002. Srovnejte totiž těsné namáčknutí jednotlivých kusů křemíku k sobě s fotkou monstrózního čipletového GPU Ponte Vecchio, kterou jsme tu měli nedávno. Vypadá to hodně podobně.

Tip: Intel ukázal obří GPU Xe HPC: čtyři druhy 7nm a 10nm čipletů, HBM2 a 3D vrstvy Foveros

Delid naopak neukázal paměti HBM2, které tak tento vzorek nemá. Asi budou specializovaným řešením, ne výbavou všech procesorů Sapphire Rapids, pokud se vůbec jejich použití potvrdí.

FPGA pod IHS

Vedle čtyř CPU čipletů je ale na substrátu jeden zvláštní menší čip – vlevo, má kolem sebe narýsovaný světlý rámeček. Toto není osamocený čip s pamětí. Na přiblížené fotografii je vidět, že tento křemík má popisek Altera a jde tedy o FPGA (Intel už Alteru několik let vlastní, teď mimochodem to samé chce mít AMD s Xilinxem). Jakou roli hraje, nevíme. Jeho osamocené umístění na kraji procesoru působí dojmem, že zde asi nepůsobí jako nějaký akcelerátor zvyšující výkon – to by asi bylo použito spíš nějaké větší FPGA, nebo by jich mohl být větší počet.

Zde je FPGA možná přilepeno proto, aby přidalo nějakou IO technologii, která procesoru chybí – nebo je v této revizi křemíku nefunkční/pokažená. Ba dokonce by FPGA mohlo být přítomné čistě proto, že tento raný křemík nefunguje úplně korektně a potřebuje k rozběhání pomoct, což může být realizované právě tímto programovatelným obvodem. I když kdo ví, třeba se v tomto pleteme a nakonec tento čip bude i v sériové verzi. Pak možná přinese zajímavé nové možnosti.

Plocha křemíku je hodně velká

I bez toho budou ale tyto procesory hodně pozoruhodné svou čipletovou formou. Ta by mohla umožnit dosažení hodně vysokého výkonu, protože ze čtyř křemíků se dá realizovat procesor s mnohem větší celkovou plochou, než by dovolil monolit. A plocha znamená víc místa pro jádra, a tedy víc větší výkonnostní potenciál.

Protože unikly dokumenty se schématy socketu LGA 4677, známe víceméně, jak velký je substrát (deska) procesoru. Twitterový leaker/blogger _rogame se pokusil podle rozměrů substrátu odhadnout velikost čipu a vyšlo mu, že jeden křemík má 419 mm², což je rozměr, který by mohl mít velký serverový procesor i sám o sobě.

Celkově by tedy plocha těchto čipletů mohla být přes 1676 mm², což by bylo víc, než je ekvivalent dvou procesorů, které mají maximální možnou plochu pro monolitický čip (ta je někde mezi 700 a 820 mm², asi se to liší proces od procesu). Plocha CPU čipletů by tedy byla větší než u AMD Epycu, přičemž Intel nejspíš díky EMIB a jen čtyřem čipletům utratí méně z této plochy na externí propojení. Třetí generace Epyců Milan bude mít osm 84 mm² čipletů (stejných, jaké jsou v procesorech Ryzen 5000), celkově tedy jen 672 mm², ovšem k tomu je ještě 450–500 mm² IO čiplet vyráběný 14nm procesem.

Je možné, že Intel má IO funkce rozdělené do těchto čtyř čipletů, které jsou na fotce vidět, takže na jádra CPU by pak připadlo méně. Ovšem to nebude platit, pokud je pod CPU čiplety ještě separátní IO čiplet. I bez něj ale jeho CPU bude mít k dispozici o dost větší plochu křemíku než to od AMD. Intel by s procesorem Sapphire Rapids tedy mohl hodně překvapit, i když je možné, že proti 5nm Epycům, která mají vyjít později v roce 2022 (může to být až na jeho konci) už zase bude v nevýhodě.

Čiplety i do highendového desktopu, jako nástupce X299?

Podstatné na tomto všem je ještě to, že Sapphire Rapids by mohlo zároveň být základem pro návrat Intelu do highendového desktopu a pracovních stanic. Tam má má Intel teď pořád jenom platformu X299 se 14nm procesory Cascade Lake a vypadá to, že není v plánu po vydání procesorů Ice Lake-SP pro server vyrobit také jejich verzi pro desktop, takže by Threadrippery od AMD zůstaly bez konkurence.

Ale Sapphire Rapids by už s vyššími frekvencemi díky procesu SuperFin mělo být pro highendovový desktop dobře použitelné. Navíc by Intel možná mohl mít možnost využít čipletovou konstrukci a vyrábět menší verzi těchto CPU třeba se čtyřkanálovou pamětí a jen dvěma čiplety místo čtyř. Zde ale teprve uvidíme, co je v plánu, žádná roadmapa ukazující, co Intel v segmentu „HEDT“ plánuje, zatím neunikla. Ale šance na zajímavá výkonná CPU pro pracovní stanice by tu být měla.

Galerie: Vzorek procesoru Intel Xeon Sapphire Rapids s čiplety a FPGA

Zdroj: Bilibili