Intel na Computexu 2024 odhalil svůj next-gen mobilní procesor Lunar Lake, který vyjde letos v létě. Ten bude svou silnou NPU pohánět Copilot+ PC a má být velmi energeticky efektivní, ale extrémně zajímavý je hlavně novými architekturami CPU, které vás čekají i v budoucích procesorech Arrow Lake pro desktop. Vedle nového P-Core ale obří skok prodělalo zřejmě malé efektivní jádro E-Core, které paradoxně může být hvězdou této generace.

Už jsme probírali velké jádro Lion Cove, o kterém je také třeba říct, že je podle všeho silně inovované a zdá se, že prošlo největšími změnami od jádra Sandy Bridge či Nehalemu. Nicméně Intel přistoupil k výraznému překopání (a posílení) také u E-Core, které má označení Skymont. Toto jádro má dokonce v některých ohledech silnější parametry a mělo by dosahovat IPC velkých jader.

Skoro se z toho vkrádá myšlenka, jestli Intel neplánuje v některé z dalších generací přerušit linii velkých jader „Cove“ a začít stavět i hlavní architekturu na této linii „Montů“, původně pocházející z Atomů.

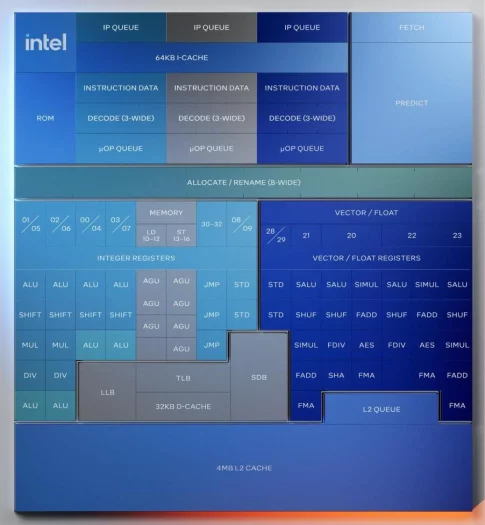

Tři klastry dekodérů, celkem devět

Skymont vychází viditelně ze základu jader Tremont a Gracemont, ale masivně ho posiluje. Nejviditelnější je to na nejpozoruhodnějším rysu architektury – vícečetných klastrech s instrukčními dekodéry. Architektury Tremont a Gracemont měly dva klastry po třech dekodérech, které se střídaly při práci, například při zpracování větvení začínal druhý dekodér zpracovávat další proud instrukcí od místa, kam skok v kódu mířil. Toto řešení je asi méně náročné komplexitou a spotřebou než přímo šest dekodérů v jednom klastru.

Skymont jde ještě dál a má celkem devět dekodérů – totiž tři klastry po třech dekodérech. Fungovat by to pak mělo stejně jako v předchozích jádrech, ale v práci se střídají a překrývají tři klastry místo dvou, jde tedy o posílení dekódovací fáze o 50 %, ovšem ne ve výkonu jednoho izolovaného klastru. Každý z těchto klastrů také může dekódovat instrukce, které jsou mikrokódované (Intel to označuje jako funkci Nanocode), což zlepšuje výkon v situaci, kdy by je kód intenzivně používal.

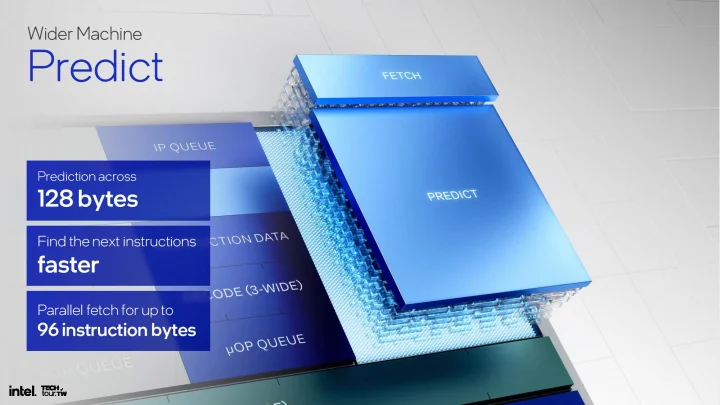

Tyto dekodéry jsou z L1 instrukční cache krmené fází fetch, která načítá celkově až 96 bajtů za cyklus, což je dost (asi by to mohlo být třikrát 32 bajtů z různých míst L1i cache, která by musela být tříportová). Fronta uOP queue, do níž jdou operace z dekodérů, byla prohloubena z 64 na 96 položek. Také prediktor větvení byl proti předchozí generace vylepšen.

Reorder Buffer větší než u Zenu 4

Fáze rename a allocate byla posílena, a zatímco v Gracemontu uměla zpracovávat šest operací za cyklus, ve Skymontu už osm operací za cyklus. Reorder Buffer (RoB), v jehož rámci může procesor přehazovat pořadí zpracovávaných instrukcí v rámci Out of Order vykonávání, je zvětšený o 60 %, což je jeden, ale ne poslední, z rysů ukazujících na velmi ambiciózní výkonnostní cíle jádra. Zatímco Gracemont používal RoB o 256 položkách, Skymont má RoB se 416 položkami.

Mimochodem, AMD používá až překvapivě malé RoB, takže Skymont ho má hlubší než architektura Zen 4 (320 položek), ale i než jádro Sunny Cove z procesorů Ice Lake, Tiger Lake a Rocket Lake (352 položek). Nynější velké jádro Golden Cove používá RoB hluboký 512 položek, nadcházející Lion Cove ale už bude mít 576 položek.

Vedle ROB byly zvětšeny také fronty v jednotlivých reservation station. A jádro má také více registrů ve svém fyzickém souboru registrů, takže má více kapacity pro přejmenovávání architektonických registrů (kvůli omezení konfliktů) při zpracovávání kódu.

Malé jádro to opravdu nebude…

Oddělenou ALU část a jednotku FPU (SIMD), což je novinka Lion Cove, jádra této linie měla již dříve, takže zde to změna není. Celkem má backend s vykonávacími jednotkami obrovských 26 portů a na těchto portech (01–07) je osm jednotek ALU. Ano, více než u velkého jádra, byť asi budou rozdělené na komplexní a jednoduché, které budou umět jen subset operací. Čtyři jednotky by asi měly umět operace SHIFT, dvě dělení a dvě násobení.

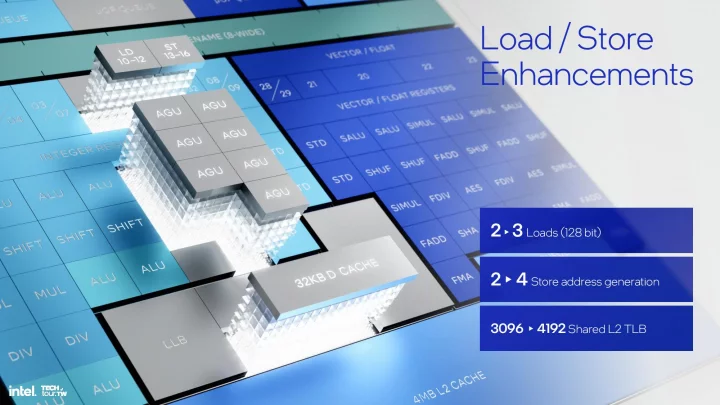

Dále má jádro samostatně tři porty s jednotkami JMP, které umí zpracovat až tři větvení za cyklus, a další dva porty s jednotkami Store Data. Hodně zajímavá je load/store část, která má sedm portů a jednotek AGU, tedy také víc než Lion Cove s šesti. Zajímavé ale je, že jen tři AGU jednotky jsou pro operace load, které zpracovávají operace čtení, zatímco pro operace zápisu (store) má jádro čtyři jednotky AGU.

Jádro tedy umí konat tři čtení za cyklus, jejichž šířka zůstává na 128 bitech, ale čtyři zápisy za cyklus, byť to je řeč o vygenerování adresy pro operaci, samotný zápis potřebuje ještě použít Store Data Pipeline. Obvykle bývá rovnováha vychýlená spíše naopak ve prospěch kapacity v operacích load (Gracemont uměl od každého dvě operace). Intel má ale zřejmě nějaké důvody, proč se mu přidání více store pipeline vyplatí – možná jsou jednodušší, a cena za čtvrtou jednotku je tak nižší. Intel také prohloubil fronty pro čtení a zápisy.

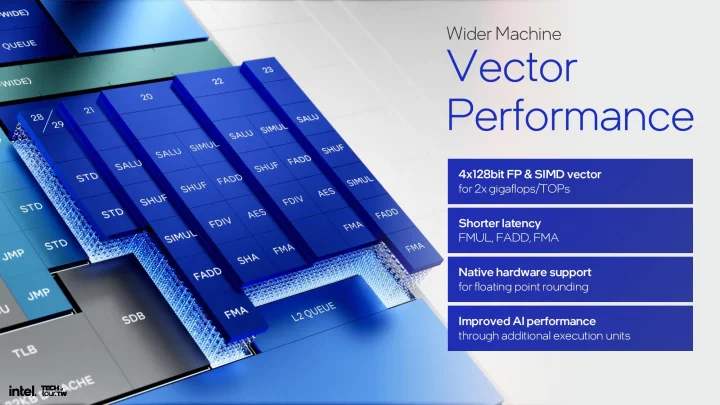

SIMD jednotka stále 128bitová, ale s dvojnásobným výkonem

Skymont má stále jen 128bitovou šířku jednotek SIMD, a je tak stále poněkud pozadu za velkými jádry ve výpočetním výkonu. Tedy oproti velkým x86 jádrům s 256bitovými jednotkami (Intel), nebo teď dokonce 512bitovými (AMD Zen 5). ARM jádra včetně těch od Applu však používají 128bitové jednotky také, včetně největších jader, takže proti těm Skymont ve velké nevýhodě není.

Předchozí jádro Gracemont mělo tři SIMD pipeline, ale jen pro celočíselné SIMD vektory, floating-point umělo počítat jen na dvou pipeline. Skymont má čtyři pipeline a u většiny operací výrazně posílenou propustnost, obvykle umí zpracovat dvakrát více instrukcí za takt, což znamená dvojnásobek GFLOPS/TOPS, které se z jádra teoreticky dají vyždímat. Tento zlepšený výkon mohou využít multimediální aplikace jako enkodéry videa, ale i AI aplikace provádějící inferenci na CPU (výkon v operacích VNNI je také dvojnásobný).

SIMD jednotka umí čtyři běžné celočíselné operace za cyklus (+33 % proti Gracemontu), dvě celočíselné SIMD násobení za cyklus (2× proti Gracemontu). Operace shuffle umí čtyři za cyklus, z čehož budou mít programátoři optimalizující kód v assembleru radost.

Floating point sčítání a běžné operace jsou možné čtyři za cyklus (2×) a také FMA umí jádro Skymont čtyři za cyklus (2×, i když nevíme), což je docela silné. Dělení umí jádro dvě za cyklus (2×). Schopnost akcelerace AES (dvě operace/cyklus) a SHA (jedna operace/cyklus) se nezměnila.

Intel uvádí, že instrukce FMUL, FADD a FMA mají také kratší latenci (na jejich výsledek se čeká méně cyklů), což se nepromítne v teoretickém výkonu, ale v praktickém ano, protože operace na sobě mohou být závislé a pak kratší latence výpočet urychluje. Jádro má také nativní hardwarovou podporu pro floating-point zaokrouhlování.

Finální fáze zpracování jsou také posílené, stupeň pipeline retire teď umí zpracovat až 16 instrukcí za cyklus místo 8. To je asi proto, aby po dokončení instrukcí jádro mohlo co nejrychleji odmáznout jejich data a položky ve frontách a uvolnit prostředky pro další operace.

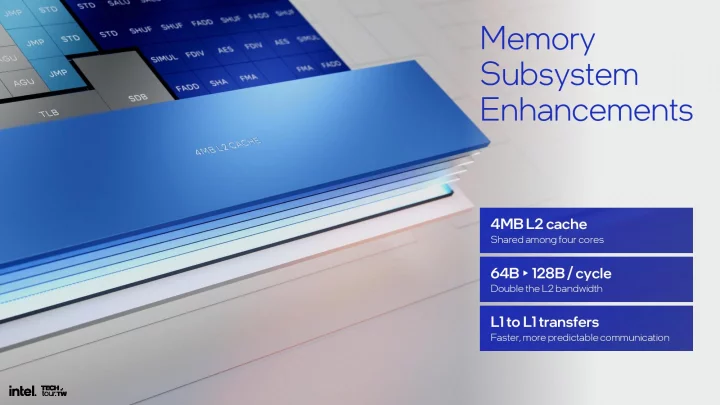

Kapacity pamětí cache se patrně nezvyšují. U jader Gracemont byla použitá L2 cache s kapacitou 2 MB sdílená čtyřmi jádry v jednom klastru, ovšem u některých procesorů (Alder Lake) byla kapacita snížená na 2 MB. U Skymontu by patrně kapacita měla být 4 MB vždy.

Propustnost dat je ale u této cache dvojnásobná, lze z ní do L1 cache a zpět přenést 128 bajtů za cyklus proti 64 bajtům u Gracemontu, což se bude hodit, aby ona posílená SIMD jednotka měla potřebná data na práci. L2 TLB byl posílen ze 3096 položek na 4192.

Nejefektivnější výkonné jádro Intelu

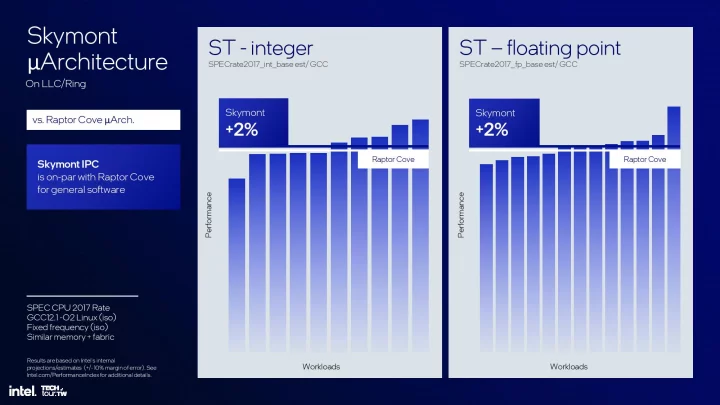

Takto firma jádro Skymont charakterizuje a něco na tom bude, protože toto jádro vzhledem k interní šířce osmi ALU nebo devíti dekodérů stěží lze nazvat malé a výkon by také měl být dost vysoko. Podle Intelu dokonce Skymont dosahuje srovnatelného IPC proti velkému jádru předchozí generace (procesory Raptor Lake), takže od toho, aby velké jádro nahradil, asi Skymont dělí hlavně dosahované frekvence. Zatím nevíme, zda budou stejné, nebo vyšší než u Gracemontu (maximálně 4,0–4,3 GHz), nebo se nesníží, což by při šířce jádra nebylo úplně překvapivé.

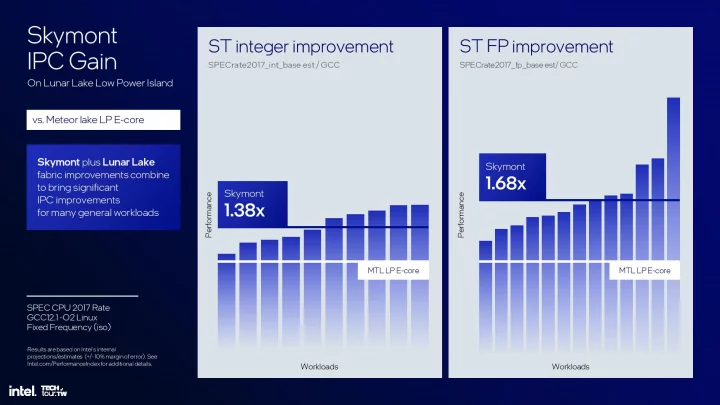

Skymont podle Intelu dosahuje až o 38 % lepšího jednovláknového výkonu na 1 MHz frekvence (IPC) oproti předchozí architektuře E-Core v celočíselných úlohách. Ve floating-point kódu, kde se uplatňuje výrazně silnější FPU/SIMD jednotka, má dokonce být IPC až o 68 % vyšší. Tyto nárůsty se dost liší podle aplikace, jak ostatně můžete vidět na grafu Intelu, uváděná procenta jsou průměr.

Toto srovnání ale není proti architektuře Gracemont, ale proti příbuznému, avšak lehce jinému jádru Crestmont, které je použito v procesorech Meteor Lake. Pozor ale na to, že jde o LP E-Core, srovnává se tedy s níže taktovanými jádry přítomnými v low power islandu procesoru, která nemají L3 cache a podle testování jim to hodně snižuje výkon. Tato jádra mají jen 2MB L2 cache, zatímco Skymont v tomto testu benefituje ze 4MB cache. Část z velmi atraktivně působícího nárůstu IPC tedy může být získána tím, že výkon Crestmontu je v testech trošku přiškrcený touto LP implementací v procesoru Meteor Lake.

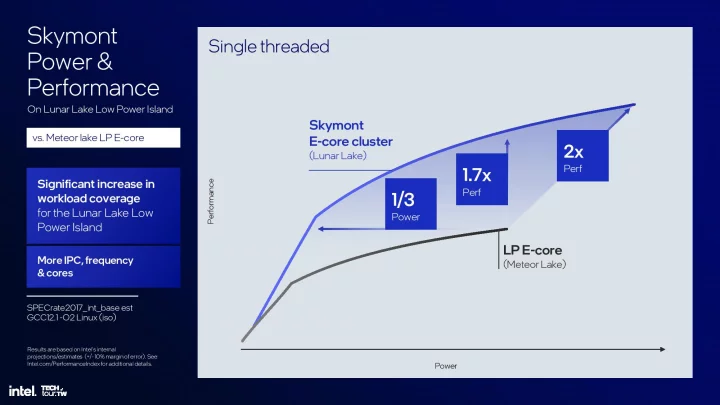

Skymont podle Intelu dosahuje až 2× vyššího výkonu než LP E-Core Crestmont (což je ale při vyšší frekvenci a spotřebě). Při stejné spotřebě jako LP E-Core Crestmont může být až o 70 % rychlejší. A pokud se sníží napětí a seštelujete výkon Skymontu na stejný výkon, jako má LP Crestmont, může spotřeba být třetinová. Takto se však křivky napětí a frekvencí obecně chovají, vypadá to tak u nových architektur často, nejde tedy o nějakou zcela unikátní úspornost tohoto konkrétního jádra.

Skymont má lepší IPC než dnešní velké jádro Intelu

Avšak jádro by mělo být dost výkonné i tehdy, když se nesrovnává s přiškrceným Crestmontem. Intel totiž uvádí i srovnání s výkonem velkých jader P-Core v procesoru Raptor Lake. Toto by mělo to být srovnání pro jádra Skymont integrovaná již s L3 cache na prstencové sběrnici procesoru, jako je tomu na desktopových procesorech (a zřejmě tomu tak bude u procesorů Arrow Lake).

V tomto srovnání má Skymont v průměru o 2 % vyšší IPC než velké jádro procesorů Raptor Lake v celočíselném kódu i ve floating-point výpočtech. Opět se to liší aplikaci od aplikace, někde je Skymont horší, někde lepší. Je to ale zajímavý výsledek. Gracemont byl takto schopen dorovnat IPC architektury Skylake, což bylo velké jádro o dvě generace starší (ovšem na roky o šest let starší). Skymont je pozadu v IPC již jen o jednu generaci.

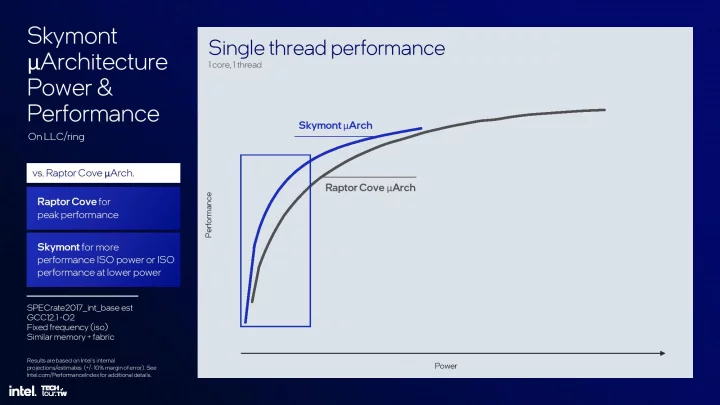

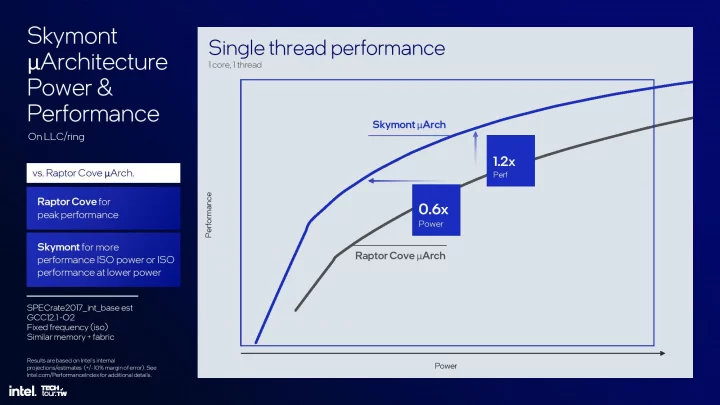

Nicméně jak už bylo řečeno, Skymont jistě bude dosahovat mnohem nižších frekvencí než velká jádra v procesorech Raptor Lake a Arrow Lake. O kolik nižší, to teprve uvidíme. Podle grafů Intelu bude maximální výkon, který se bude dát ze Skymontu vytřískat, nižší než u Raptor Lake (právě kvůli frekvenci), ovšem při výrazně nižší spotřebě. Ale na celé své škále frekvencí by jádro Skymont mělo vždy určitý výkon podávat s nižší spotřebou, než s jakou to dokáže P-Core z Raptor Lake. Rozdíl může být až 40 % spotřeby, případně při sladění jader na stejnou spotřebu může Skymont být až o 20 % rychlejší.

V reálných procesorech ale samozřejmě bude Skymont párován s jádry Lion Cove, která by na tom měla být lépe. Budou mít vyšší IPC a tím i vyšší maximální výkon než Raptor Lake. A díky 3nm výrobnímu procesu také lepší energetickou efektivitu. Skymont by jim ale měl hodně pomáhat v mnohovláknovém výkonu (nebo v mobilních procesorech ve výdrži baterie), takže jako společník může mít lví podíl na úspěchu procesorů Arrow Lake a Lunar Lake.

Skymont slibuje zajímavé výsledky nových big.LITTLE procesorů

V hodnocení je samozřejmě třeba čekat i na nezávislé testy, které by v případě procesoru Lunar Lake mohly být k dispozici v třetím čtvrtletí a pro Arrow Lake ve čtvrtém. Ale takto na papíře to vypadá, že Intel odvedl hodně dobrou práci.

Zdroje: Intel, AnandTech, Tom’s Hardware