Nová generace 3D NAND společného podniku WD a Kioxia

O této paměti jsme už psali loni, ale zajímavé je, že tehdy obě firmy uváděly, že BiCS5 bude používat 128 vrstev. Verze technologie, která nyní jde na trh, bude ovšem poněkud mírnější, nyní je oficiálně uváděno, že obsahuje 112 vrstev. Není jasné, zda zde třeba „zmizelé“ vrstvy nejsou brány jako rezerva pro zvýšení výtěžnosti nebo něco podobného, v opačném případě prostě byl finální design změněn, nebo dřívější informace nebyla správná.

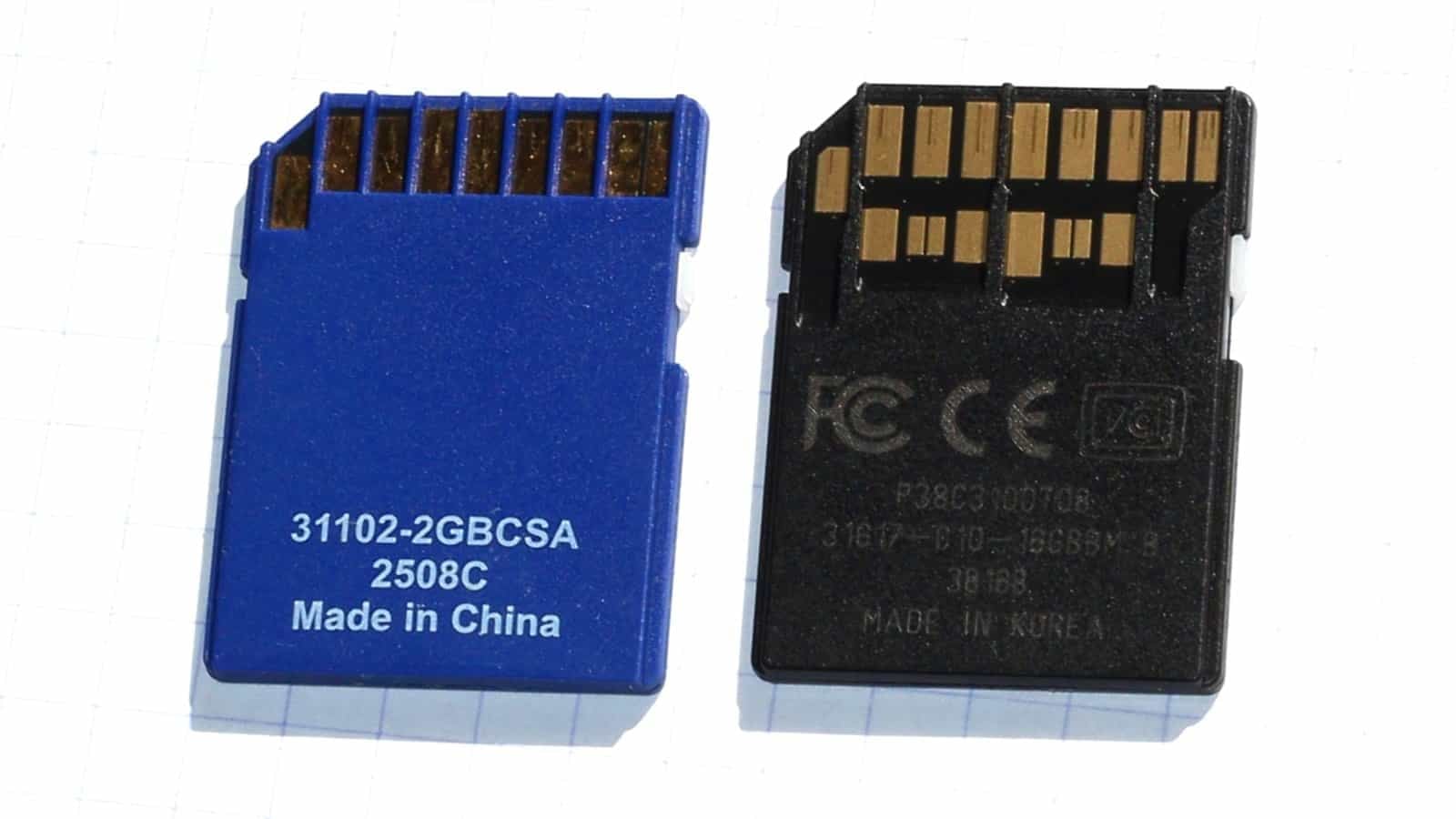

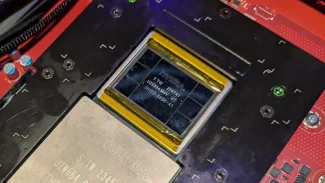

Tyto 112vrstvé čipy budou eventuálně vyráběné v kapacitě 1Tb (128 GB), což bude čip se zápisem TLC, a 1,33Tb (cca 170 GB), který bude mít stejný počet buněk, ale zápis QLC, jenž zajistí o třetinu vyšší kapacitu díky čtyřem bitům uloženým v buňce (místo tří). Tyto verze budou určené do zařízení s vyšší kapacitou. Pro levnější a menší SSD a vůbec úložiště je ale důležité, že bude nadále vyráběná i 512Gb verze čipu (s kapacitou 64 GB) se zápisem TLC. Disky pro efektivní fungování totiž potřebují paralelismus a minimálně čtyři, lépe však osm nebo dokonce víc čipů. 512Gb verze čipu bude v produkci jako první, 1Tb a 1,33Tb (QLC) verze půjdou do výroby s určitým zpožděním.

Tip: Čipy NAND a SSD od Toshiby se přejmenují na Kioxia, značka se mění kvůli prodeji firmy

Tyto čipy nevznikly pouze čistým navýšením počtu vrstev. I přímo na úrovni jednotlivých vrstev je architektura vylepšená, například použitím metody nazvané Multi-tier memory hole technology. O co přesně jde, bohužel tisková zpráva nerozvádí. Kioxia publikovala v prosinci zlepšovák nazvaný „Twin BiCS Flash“, který spočívá v tom, že se vertikální komínky pro buňky 3D NAND „vrtají“ s oválným místo kruhovým profilem. A tento profil je pak rozpůlen na dva půl ovály, které lze díky rozdělení využít jako dvě samostatné buňky a tím značně zvýšit kapacitu na jednotku plochy. Ovšem toto by asi do produkce mohlo být zavedeno až v nějaké další generaci a technologie Multi-tier memory hole tedy může být něco jiného.

Výsledkem optimalizací ale každopádně je, že každá vrstva má sama o sobě asi o 20 % lepší hustotu záznamu, což se zvýšením počtu vrstev vede k tomu, že BiCS5 poskytuje celkově asi o 40 % hustotu.

112vrstvé TLC čipy mají poskytovat až o 50 % lepší výkon

Navíc má být tato pátá generace 3D NAND od Toshiby/Kioxia/WD i rychlejší. Přenosová rychlost má být až o 50 % lepší (rychlost rozhraní má být 1,2 GT/s), zároveň má být zkrácena latence čtení a také programování (zápis) je rychlejší. Zda se to promítne do datových propustností SSD, ale bude záležet i na řadičích a firmwarech, takže toto je jenom jeden krůček, kvůli kterému všechno hned automaticky nezrychlí.

Tyto nové čipy jsou zatím dodávány jako vzorky, sériová výroba se pořádně rozjede až v druhé polovině roku. Nějaké nové modely SSD založené na této rychlejších 3D NAND by se tak asi mohly objevit koncem roku, ale většinou asi půjde až o technologii roku 2021.