Takzvaná segmentace produktů, čili vypínání některých funkcí (podporovaných jinak čipem), aby byly exkluzivní pro dražší verze, bývá často kritizována u levnějších procesorů Intel. Tam už dlouhá léta Intel vypíná nové instrukce SIMD – v době Core 2 to bylo SSE4, od Sandy Bridge nemají Celerony a Pentia AVX a AVX2.

Je to nepříjemné i proto, že programátoři nemohou počítat s jejich přítomností, což možná brzdí jejich rozšíření; takže Intel je tu vlastně i sám proti sobě. Ovšem vypadá to, že toto blokování by mohlo přestat.

Konečně méně opižlané instrukce u levných CPU

Už pár let mají Pentia aktivní HT (čtyři vlákna), což bylo dlouho takovou segmentovanou funkcí. A vypadá to, že výhledově by mohl Intel upustit i od klatby uvalené na nové instrukce. Nové mobilní (notebookové) Celerony a Pentia, která jsou založená na 10nm čipech Tiger Lake, totiž poprvé mají podporu těchto instrukčních rozšíření.

V databázi Intel ARK se již dají vyhledat Celeron 6305 a Pentium Gold 7505, což jsou 10nm mobilní procesory s dvěma jádry používající křemík Tiger Lake. A výčet jejich funkcí a výbavy potvrzuje, že u nich poprvé budou přítomné instrukce AVX a AVX2. Rozšíří se tedy i do lowendu a programátoři s nimi budou moci o trošku víc počítat (ale jen o trošku, protože je tu to moře procesorů bez nich, které Intel a v minulosti AMD doteď prodaly/prodávají plus také čipy na bázi architektury Atom).

Je zajímavé, že procesory Celeron a Pentium dokonce mají instrukční rozšíření DL Boost a GNA 2.0 (Gaussian and Neural Accelerator). Ta by přitom měla být postavená na technologii AVX-512, jelikož snad používají 512bitové registry ZMM. Ale samotné AVX-512 Celerony a Pentia nedostanou, to bude jen od Core i3 a vyšších. ARK potvrzuje, že je vypnuté.

Intel tedy vyřešil problém s nedostupností AVX2, ale u AVX-512 problém s tím, že ho mají jen některé procesory, zůstává dál. Vlastně je to možná tak, že politika firmy se vůbec nezměnila. Ono deaktivování rozšíření totiž vždy fungovalo tak, že bylo lowendu upřeno to nejnovější rozšíření.

V době SSE4 byly levné procesory omezené uměle na SSSE3. Po příchodu AVX a později AVX2 s 256bitovými vektory Intel omezil Celerony a Pentia jen na předchozí 128bitové instrukce SSE-SSE4 (což trvá ve všech derivátech Skylake). A teď, když čipy, o které běží, dostaly nové 512bitové instrukce AVX-512, Intel v křemíku vypne tyto a uspokojen jejich obětováním konečně zapne AVX a AVX2. Po 7–9 letech od jejich uvedení, mimochodem.

V desktopu možná až s platformou LGA 1700

Bavíme se zde celou dobu o 10nm procesorech pro notebooky, takže zatím není vůbec jasné, zda se stejnou cestou budou ubírat také levné procesory pro desktop. Nyní AVX a AVX2 mají vypnuté. Procesory Tiger Lake se do desktopu nepodívají, Intel místo nich vydá Rocket Lake. To ovšem asi nebude pro Pentia a Celerony použito, Intel v lowendu a v modelech Core i3 bude dál prodávat jenom Comet Lake. Je proto možné, že pokud se na desktopu také AVX2 do nejlevnějších procesorů dostane, bude to až s Alder Lake na platformě LGA 1700. Ovšem to by možná mohlo vyjít již za rok.

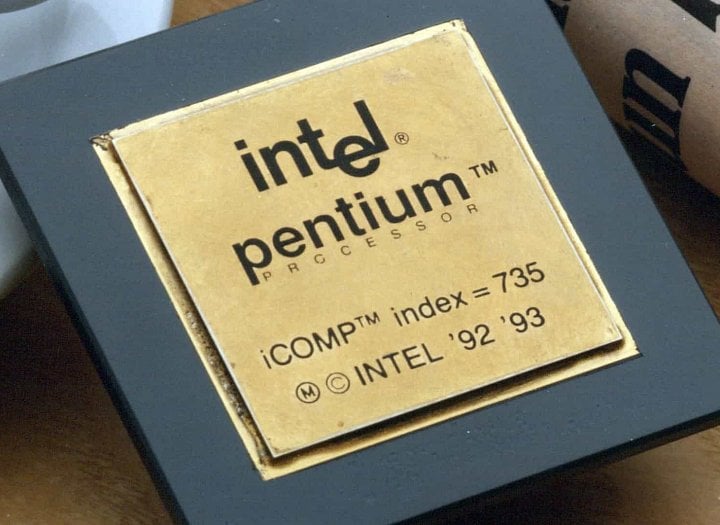

Kdysi bývalo Pentium chlouba Intelu, ale po zprofanování v éře Pentia 4 se z něj stala značka pro lowendové procesory (Zdroj: Intel)

Kdysi bývalo Pentium chlouba Intelu, ale po zprofanování v éře Pentia 4 se z něj stala značka pro lowendové procesory (Zdroj: Intel)Ideální by asi bylo, pokud by Intel přestal toto omezení provádět a všechny procesory s odpovídajícím křemíkem měly zapnuté i AVX-512. Ovšem v situaci, kdy procesory AMD také AVX-512 nepodporují, není asi argument, že mají programátoři zkomplikován život, tak silný. AVX-512 je zatím celkově málo používané, takže Intel ubližuje hlavně samotnému rozšíření a uchycení těchto instrukcí v ekosystému. V případě AVX2 je rozšíření naopak velké a podpora už i u konkurence, takže zde už se dá mluvit o tom, že jsou opravdu potřeba.

Zdroje: Tom's Hardware, Intel (1, 2)