Už jsme dnes psali o uniklých informacích vrhajících světlo na chystané paměti DDR6. Pro osobní počítače ale možná v příštích generacích nebude použitá tato paměť, nýbrž mobilní LPDDR6 a místo běžných modulů přejdeme na placaté moduly LPCAMM2. To by ale mohlo mít dost výhod, a nejen ve spotřebě. Nové paměti každopádně budou o dost odlišné, například se místo tradiční šířky 64 a 128 bitů přejde na kanály se šířkou v násobcích čísla tři.

LPDDR6–10667 až LPDDR6–14400, ale s bonusem v šířce

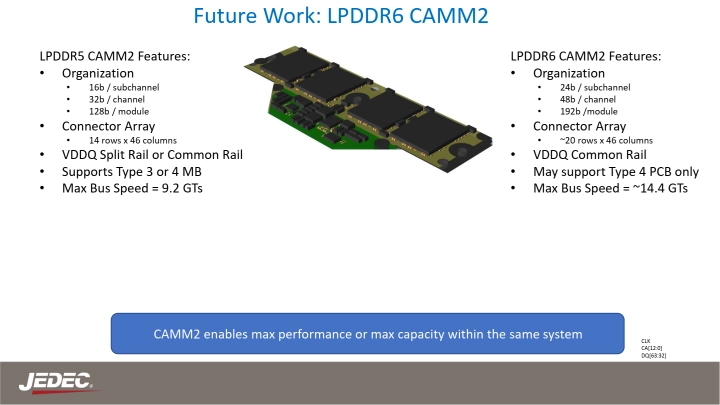

Paměti LPDDR6 mají v plánu odstartovat na efektivní rychlosti 10,667 GHz či GT/s (proti 9600 MHz specifikovaných pro LPDDR5X). Jako nejvyšší definovaná rychlost ve standardu, a na kterou by se vyráběné paměti postupně dostaly, má být 14,4 GHz. Později pochopitelně může být standard aktualizován, pokud by se zjistilo, že je potenciál laťku zvednout. Nebo z něj může být vytvořená zrychlená varianta LPDDR6X (analogicky k LPDDR4X a LPDDR5X).

Tyto rychlosti by samy o sobě byly nižší než u DDR6, avšak pozor, jde o frekvence či přenosové rychlosti (v Gb/s) na jeden bit datové šířky paměti. U LPDDR6 se ale počítá s tím, že by se kanál jednoho čipu této paměti rozšířil o 50 % – z 16 bitů na 24 bitů. To je nezvyklé (násobek tří), ale počítá se asi s tím, že by se typicky v notebooku nebo mobilu použilo stejné množství kanálů jako nyní s 16bitovými LPDDR5X, tedy například čtyři či osm čipů.

Tím pádem bychom začali místo 64bitových (v tradičním a již ne úplně přesném názvosloví „jednokanálových“) a 128bitových (čemuž se nepřesně říká dvoukanálové zapojení) pamětí používat 96bitové a 192bitové paměti. V podstatě by to znamenalo, že místo dvoukanálových pamětí se stane standardem ekvivalent tříkanálových (a místo jednokanálových budete mít kanál a půl).

V reálném nasazení by se tedy zkombinoval efekt o 50 % zvýšené frekvence a o 50 % větší šířky, takže teoreticky by propustnost narostla 2,25×. Prakticky bude propustnost jednoho čipu s 24bitovou šířkou 28,5 GB/s při rychlosti LPDDR6–10667 a až 38,4 GB/s při LPDDR6–14400.

Například běžný mobilní Ryzen, který má dnes 128bitové paměti LPDDR5X, by tedy dostal LPDDR6 se šířkou 192 bitů, a pak by měl k dispozici propustnost 307,2 GB/s (s LPDDR6–14400), tedy víc než má samostatný Radeon RX 7600 XT.

Nebinární šířky pamětí sice na první pohled nezapadají do toho, jak běžně funguje RAM, ale v praxi by se toho tolik – kromě propustnosti samozřejmě – nezměnilo. Jak bylo zmíněno, nerozšíří se jen rozhraní jednoho čipu, ale obvykle asi i celé sběrnice v procesoru, takže zůstává, že typicky budou použity čtyři nebo osm čipů. Tím pádem kapacity paměti obvykle asi budou stále násobkem dvou, pokud bude kapacita čipů následkem dvou (což nemusí, ale to už je separátní věc). Tedy stále budete v počítači obvykle mít 16, 32 nebo 64 GB (či 128, 256 GB a tak dále) paměti.

Šířka 24 bitů, Burst Length 24

Šířka čipu ale nebude komplikací ani pro potřeby interní organizace procesoru a jeho pamětí cache. Ty mají obvykle délku řádku 64 bajtů (512 bitů) a je třeba, aby se dal celý řádek jednoduše načíst z paměti bez nějakého složitého rozdělování a hlavně bez toho, aby načtená data přetékala do dalšího řádku. Což by s 24 bitů širokými čipy a třeba 192 bitů širokou paměťovou sběrnicí bylo dost nekompatibilní. Nicméně LPDDR6 na to má řešení.

Zápisy a čtení paměti neprobíhají ve skutečnosti tak, že by se přenesla jednotlivě data odpovídající šířce čipu v jednom cyklu. Místo toho se používá dávka (burst), jejíž délka (burst length, BL) je několik cyklů, u DDR je to 16. Při přenosu dostanete data za celou dávku. U DDR5 je paměťový modul o šířce 64 bitů ve skutečnosti rozdělen na dva nezávislé 32kanály, takže operace s jedním z nich přenáší najednou 32 (šířka v bitech) krát 16 (BL) bitů, což dává dohromady 512 bitů, čili jednu 64bajtovou cacheline.

LPDDR6 bude o dost jiná. Jeden čip s šířkou 24 bitů bude rozdělen na dvojici nezávislých 12bitových subkanálů a burst length bude také netypická, 24 cyklů. Když se dá dohromady šířka jednoho 12bitového kanálu krát BL 24 cyklů, vyjde vám 288 bitů.

Těchto 288 bitů přenesených jednou dávkou ovšem nebude použito celé pro data, jen 256 bitů bude datových. To znamená, že dvěma těmito přenosy se naplní nebo naopak vyprázdní přesně jeden 512bitový řádek v cache. Při použití obou subkanálů tak lze i s jediným čipem LPDDR6 obsluhovat jednu cacheline každou dávkou, ale v praxi bude samozřejmě u procesorů častější použití širší paměti s více čipy kvůli navýšení propustnosti.

Konečně reálně fungující ECC pro všechny?

Zbylých 32 bitů z oněch 288 fyzicky přenášených bitů bude také využito, ale ne pro data. Jejich hlavním využitím by mohla být implementace ochrany ECC. Ta je u ECC používaná sice interně v čipech DRAM, ale detekované nebo detekované a opravené chyby v čipu nejsou signalizovány dál řadiči pamětí v procesoru, takže je to v podstatě, jako byste ECC neměli. Výrobci totiž pravděpodobně ECC využívají hlavně k tomu, aby mohli ponechávat menší frekvenční rezervu nebo aby mohli prodat čipy, které by bez ECC už nefungovaly. Ve skutečnosti se tedy spolehlivost nemusela zlepšit, protože robustnost získanou on-package ECC výrobci pamětí takto „exploatovali“.

U LPDDR6 ale už bude těchto 32 bitů navíc ke každému 256bitovému datovému přenosu moci být použito k přenosu kontrolních součtů, takže i procesor bude moci ověřit správnost dat. Přesněji by to mělo fungovat tak, že jedněch 16 bitů lze použít pro ochranu komunikačního rozhraní, druhých 16 bitů by pak bylo separátně použito pro host ECC či signalizaci chyb z paměťových čipů do řadiče v procesoru.

Bohužel ve standardu asi není pevně dáno, že opravdu každé paměti LPDDR6 budou takto ECC poskytovat. Ona první 16bitová skupina může být místo ECC použita i pro jiné funkce, například Memory tagging. Druhých 16 bitů také nemusí povinně být použito pro ochranu linky. Alternativně je specifikace umožňuje použít pro funkci Data Bus Inversion (DBI), která snižuje spotřebu.

To, že dnes drtivá většina počítačů mimo servery nemá ochranu pamětí před chybami ECC, je velký dluh počítačového průmyslu (a platí to i pro mobilní zařízení), takže doufáme, že snad výrobci pamětí a procesorů dostanou rozum a opravdu využijí možnost dostat ECC „zadarmo“ v rámci standardu, kterou jim tímto LPDDR6 nabízí. Dnešní implementace ECC buď stojí část kapacity a výkonu (v případě in-band ECC), nebo vyžadují přidat na moduly další čipy kvůli redundanci, což paměťové moduly zdražuje a dávalo to dosud argument omlouvající absenci ochrany pamětí ve spotřebitelských počítačích a zařízeních. To, že u LPDDR6 budou bity pro ECC vždy přítomné, snad už přiměje výrobce pamětí, aby bylo ECC konečně standardem.

LPDDR6 v modulech LPCAMM2 pro desktopová PC?

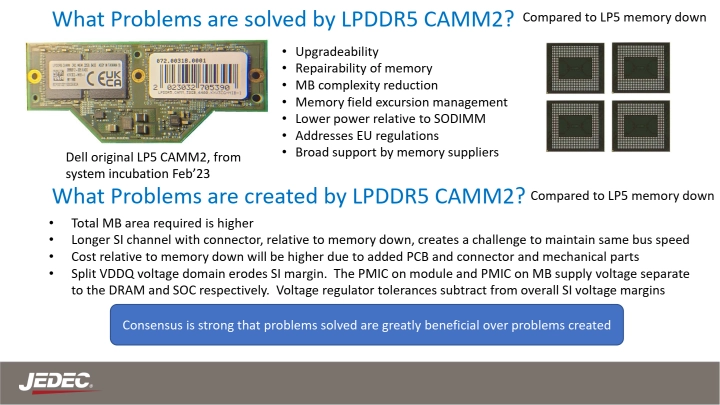

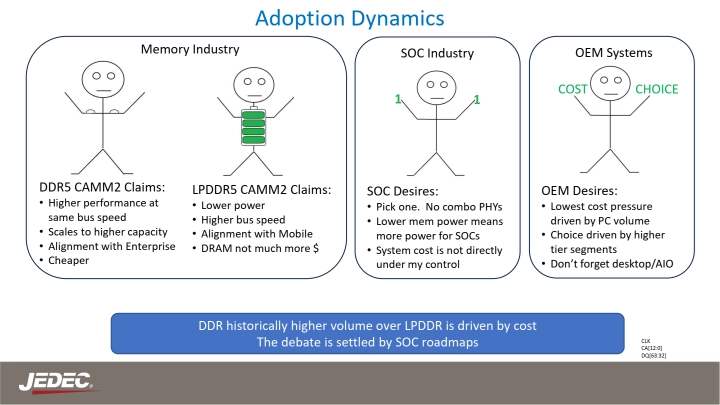

Informace o LPDDR6 unikly zřejmě z prezentace firmy Synopsys pro JEDEC. Dále se ven dostala i prezentace od Dellu, která zase ukazuje plány s paměťovými moduly CAMM2 a LPCAMM2. A tyto slajdy ukazují, že je seriózně zvažováno nebo rovnou připravováno, že by paměti LPDDR6 začaly být používány plošně v osobních počítačích místo DDR6, která by se pak používala jen v serverech.

192 bitové paměti odpovídající trojkanálu standardem v PC?

Paměti LPCAMM2 na bázi LPDDR6 budou odpovídat tomu, že čipy LPDDR6 mají o 50 % zvětšenou šířku rozhraní jednoho čipu. Počet čipů ale bude použit stejný, takže tyto moduly budou mít také větší šířku – jeden modul bude široký 192 bitů místo dnešního (LP)CAMM2 se šířkou 128 bitů a místo 64 bitů širokých modulů DIMM či SO-DIMM. Už jen tento rys by tedy znamenal zvýšení propustnosti pamětí v počítačích, které byly posledních dvacet let zaseklé na šířce 128 bitů (mimo HEDT platformy).

Globální použití LPDDR6 jak v noteboocích, tak desktopech by mohlo teoreticky o něco prodražit desktopy, kde by moduly mohly stát o něco víc než DIMMy. Také by se musela měnit montáž. V současnosti se moduly (LP)CAMM 2 musí přišroubovávat.

Nicméně prezentace ukazuje, že probíhají studie, zda by montáž nemohla být nějak řešena beznástrojově (osobně si ovšem myslím, že beznástrojové montování PC není něco, co by bylo extrémně důležité – chladiče na CPU také kvůli funkčnosti používají šroubováky, takže pokud to zajistí lepší kontakt, ať se klidně šroubují i paměti).

Výhody by ovšem byly na straně procesoru. Hodně dnešních procesorů musí mít paměťový řadič, který podporuje jak DDR5, tak LPDDR5(X), protože jsou cílené do notebooků i do desktopu. Pokud by došlo ke sjednocení na LPDDR6, stačilo by jednodušší PHY jen pro tento standard paměti. Procesory by měly menší a levnější čipy nebo čiplety. Protože obsluha paměti LPDDR6 stojí méně energie než DDR6, snížila by se spotřeba „uncore“ procesorů. Celkové TDP by to třeba neovlivnilo, ale ušetřené watty by pak procesor mohl využít v jádrech, a podat tak vyšší výkon.

Paměti LPDDR6 v modulech LPCAMM2 by v desktopech měly nižší spotřebu, ale také by dosahovaly vyššího výkonu co se týče propustnosti (latence by ale mohla být horší). Je třeba říci, že je možné také to, že desktopové procesory sice použijí kompresní moduly (CAMM2) místo DIMMů, ale zůstanou u nemobilního typu pamětí (DDR6). Pořád by to mělo výhody. Kompresní kontakty totiž zajišťují vyšší kvalitu signálu, a v herních PC by tedy dovolovaly vyšší frekvence a výkon. Také délky vodičů v deskách by mohly být kratší.

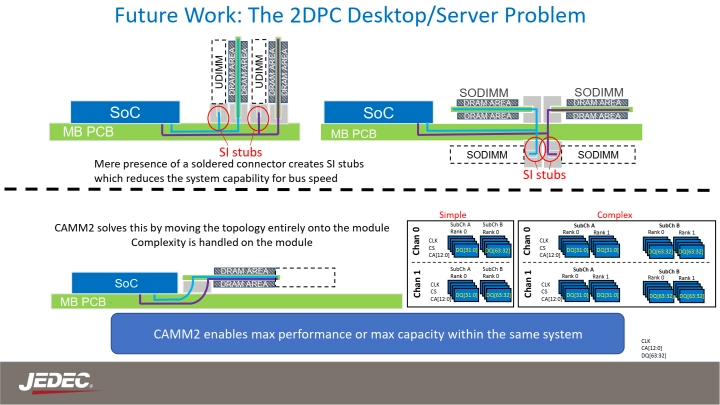

Řešení problému dvou modulů na kanálu

Jedno ze zlepšení výkonu, které by CAMM2 s DDR6 mohly přinést, je eliminace problému, kdy desky se dvěma sloty na kanál (tedy s celkově čtyřmi sloty pro paměti) mají o něco horší schopnost dosahovat vysokých frekvencí paměti. Je to kvůli tomu, že se vodiče v desce musí rozdvojovat a i u neosazeného slotu vzniká slepá „odbočka“. V té dochází k odrazům signálu a podobným problémům, které mohou komplikovat velmi citlivou vysokorychlostní komunikaci.

Moduly CAMM2 a LPCAMM2 to mají řešit tak, že na základní desce by byla jediná cesta bez rozdvojení. Tato topologie s odbočkou pro druhý modul připojený na kanálu by byla realizována v rámci modulu. V praxi by to fungovalo tak, že byste neosazovali druhý modul, ale měli byste na desce jen jednu pozici. Při koupi paměti byste ale měli na výběr mezi jednoduchým modulem, který by byl ekvivalentem zapojení jednoho modulu na každý kanál, a modulem, který by byl interně rozvětvený na dva a měl díky tomu vyšší kapacitu. Bylo by to ale celé na jednom PCB včetně onoho rozvětvení vodičů.

Toto řešení by mělo dosahovat lepšího výkonu. Avšak má to i nevýhodu, už nepůjde udělat to, že na desce ze začátku budete mít obsazenou jen polovinu slotů, avšak po nějaké době uděláte upgrade na vyšší kapacitu doplněním modulů do zbylých slotů s tím, že původní paměti si necháte nainstalované. Řešení LPCAMM2/CAMM2 by znamenalo, že musíte předchozí jednoduchý modul vyndat a prodat v bazaru nebo použít jinde. Je ovšem pravda, že pro optimální chod dnes potřebujete stejně sadu čtyř identických modulů, takže scénář dokupování dalších pamětí k existujícím modulům už asi praktikuje relativně málo uživatelů.

Záležet bude na AMD a Intelu

Postupně se objevují různé zvěsti, že výrobci počítačů chystají přechod desktopových PC (a všech notebooků) na CAMM2 či LPCAMM2 s LPDDR6. Tato uniklá prezentace dokládá, že minimálně diskuse se o tom vedou. Je v ní ovšem podotknuto, že to bude záviset na tom, jak se rozhodnou výrobci procesorů – tedy hlavně Intel a AMD (Qualcomm a další výrobci procesorů ARM se drží jen LPDDR od začátku).

Zatím se neobjevila nějaká uniklá roadmapa, která by ukazovala, jaké paměti budou používat budoucí procesory Intelu pro platformu následující po LGA 1851 (která vyjde letos pro Arrow Lake) nebo procesory AMD pro platformu, která nahradí dnešní AM5. Ovšem šance, že dojde k přechodu na LPDDR6, je evidentně nenulová.

Zdroje: JEDEC, Darkmont (1, 2), VideoCardz