Zatímco Intel nasadil do procesorů kombinaci dvou architektur P-Core a E-Core, AMD teď přichází s vlastním big.LITTLE, které bude tvořené kombinací jader Zen 4 a nové varianty Zen 4c, která se bude používat v serverech, ale také v noteboocích. Ale Zen4c je i není malé jádro. Sice zabírá mnohem menší plochu, ale architektonicky je prý plně rovnocenný velkému jádru, dokonce má mít (skoro?) stejný výkon na 1 MHz. Za „malost“ platí jen frekvencí.

AMD prezentovalo médiím něco k malému(?) jádru Zen 4c během Computexu a současně se objevil rozbor této architektury na webu SemiAnalysis. Zatím je to asi hlavně proto, že tato jádra budou tvořit „cloudové“ procesory Epyc Bergamo (proto 4c), ale takto kondenzovaný Zen by se eventuálně měl objevit také v mobilních APU – možná už v této generaci v čipu „Phoenix 2“, který má doplnit osmijádrové APU Phoenix o levnější modely.

Mnohem menší jádro se stejným IPC a funkcemi

Pokud by se koncepce Zenu 4c měla shrnout: Podle CTO AMD Marka Papermastera je smyslem tohoto jádra výrazně zvětšit hustotu tranzistorů (a tím zmenšit jeho plochu), aby se jich do určité plochy dalo nacpat větší množství právě pro potřeby oněch cloudových procesorů. Jádro má plochu zredukovanou téměř na polovinu proti klasickému velkému Zenu 4. Avšak na rozdíl od E-Core nebo klasických malých jader ARMu je u těchto jader zachovaná „identická funkcionalita“ jako u Zenu 4.

Podle AMD jádro Zen 4c (jeho kódové jméno je údajně Dionysus) není prakticky v ničem osekané a má mít principiálně stejné IPC (výkon na 1 MHz). Zásadní je také to, že AMD potvrdilo plnou kompatibilitu na úrovni instrukční sady, Zen 4c tedy bude podporovat i instrukce AVX-512, a nedojde tak k problémům, které měl s big.LITTLE Intel.

Tip: AVX-512 na Ryzenech 7000: jak užitečné je a je implementace od AMD lepší než Intelu?

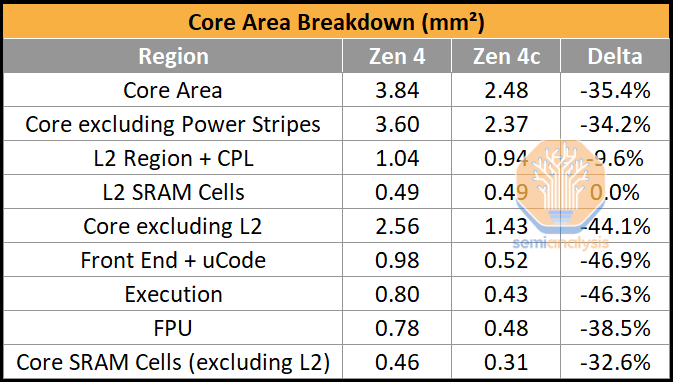

U Zenu 4c byla změněná organizace jader a cache, avšak k osekání došlo jen u L3 cache. Jádro Zen 4c má nadále 32 kB L1 cache pro data a 32kB L1 cache pro instrukce, také L2 cache zůstala 1MB (což je možná překvapení, ale je to asi kvůli onomu zachování IPC a také kvůli optimalizaci pro cloudové instance, pro které je privátní cache důležitá).

K řezu došlo až u L3 cache. AMD ji zmenšilo na 16 MB pro jeden blok CCX s osmi jádry. Naproti tomu L3 u desktopového a serverového Zenu 4 má 32 MB. Ale u mobilních APU/SoC už AMD nějakou dobu L3 cache snižuje, takže 16MB L3 cache z Zenu 4c v podstatě jen odpovídá tomu, co mají mobilní jádra Zen 4. Toto by asi mohla být jedna oblast, kde nebude platit tvrzení, že se IPC nesníží – některé aplikace menší L3 cache pocítit mohou.

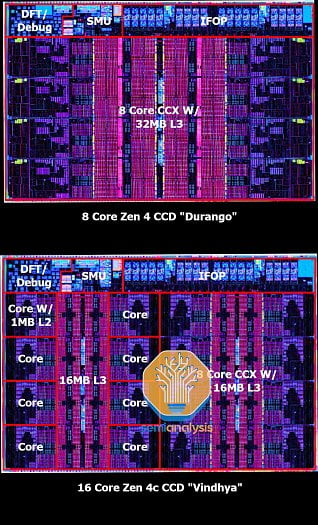

Zen 4c bude v serverech používat CPU čiplety s 16 jádry (jejich kódové označení je Vindhya), která budou ve dvou blocích CCX, ne už v jednom. Každý blok by měl mít 16MB L3 cache, takže celková L3 cache na čipletu zůstane stejná. I z tohoto důvodu bylo asi nutné L3 cache pro jeden blok zmenšit na polovinu. L3 cache totiž u Zenu 4 zabírá polovinu plochy CPU čipletu.

Hustota se zvětšila fyzickým návrhem pro nižší takty

Hlavní rozdíl proti Zenu 4 je ale v tom, že AMD přepracovalo fyzickou implementaci architektury a použilo knihovny zaměřené na vyšší hustotu tranzistorů místo knihoven určených pro vysoký výkon. Také byla eliminována příprava na TSV (vertikální cesty pro připojení 3D V-Cache), což rovněž ušetřilo místo na čipu. Celkově by CPU čiplet s 16 jádry a 2× 16MB L3 cache měl pořád měřit jen 72,7 mm², zatímco u běžného Zenu 4 je plocha 66,3 mm². Plocha křemíku tedy při zdvojnásobení počtu jader (a množství L2 cache) narostla o necelých 10 %.

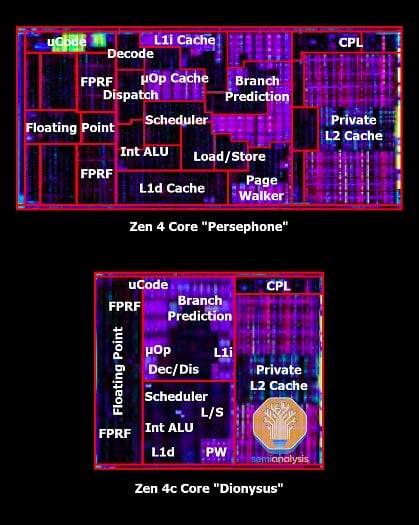

Podle dostupných obrázků jádra se zdá, že AMD změnilo i rozložení a umístění částí jádra na čipu. Zřejmě prý jsou bloky méně ohraničené, a syntéza je tak mohla „scuknout“ blíže k sobě. Má to asi být proto, že tyto hranice mezi bloky mají za cíl usnadnit testování a ověření funkčnosti CPU u nové architektury, přičemž Zen 4c jako její reimplementace je už na toto méně citlivý. Zen 4c má jen čtyři „partitions“ (frontend, výpočetní jednotky, L2 cache a FPU/SIMD). Toto samo ušetří nějaké místo, které u Zenu 4 zůstalo nevyužité.

Současně s tím pak byly použité knihovny standardních bloků zaměřené na vyšší hustotu a design, který obětuje schopnost dosáhnout vysokých frekvencí (vysoko nad 5 GHz u desktopových procesorů). Takový návrh používá tranzistory a elementy navíc (nebo větší tranzistory) na mnoha místech, aby zlepšil dosažené frekvence. To Zen 4c eliminuje, protože se u něj počítá jen s výrazně nižším taktem. Výsledný obvod se pak dá implementovat v menší ploše. Různé části jádra mají údajně plochu zredukovanou až o 35–45 %. Toto je přitom stále na stejném 5nm procesu (TSMC N5). Klíčem k tomuto zvýšení je patrně hlavně zjednodušení vodičů mezi tranzistory, tedy kovových vrstev.

Zdá se, že se nezmenšila plocha samotné L2 cache – její buňky SRAM mají stále stejnou hustotu a plochu – ale byly zmenšené její řídicí obvody. Některé další bloky SRAM v logice jádra ale byly zhuštěné, AMD u nich použilo buňky typu 6T (z šesti tranzistorů) místo buněk 8T s osmi tranzistory. 8T buňky byly dříve použité kvůli dual-port funkci (může k nim být připojen dvojí vstup/výstup), ale TSMC vyvinulo speciální 6T buňky s pseudodual-port funkcí, které toto dokáží díky double-pumped frekvenci (dva přístupy se sekvenčně odehrají v jednom cyklu na stejném rozhraní). A Zen4c údajně používá tuto technologii.

Ještě není úplně potvrzené, zda AMD nezredukovalo počet pipeline v FPU/SIMD jednotce, jako to udělalo u jádra „Zen 2 Lite“ použitého v konzolích PlayStation 5, Xbox Series X a S nebo APU Mendocino. To by už v daných operacích samozřejmě IPC snížilo.

Boost klesne hodně, ale základní a all-core frekvence v serverovém CPU mohou být skoro stejné

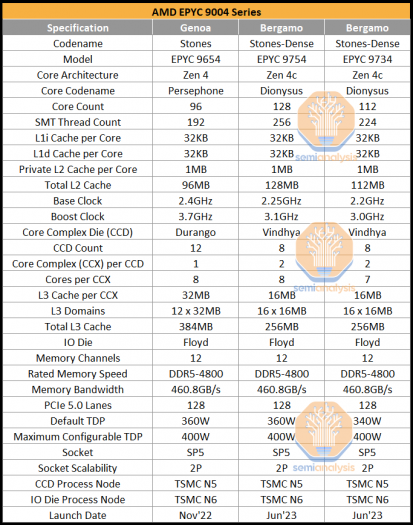

Už jsou známé specifikace dvou procesorů Epyc „Bergamo“ s touto architekturou. Plnotučný model se jmenuje Epyc 9754 a obsahuje 128 jader (256 vláken) v osmi CPU čipletech. Procesor používá stejný IO čiplet jako běžné Epycy 9004 „Genoa“, ale podle některých indicií je asi pro něj maximem osm CPU čipletů, kdežto 12 (což by umožnilo modely se 192 jádry) asi se současným provedením substrátu a pouzdra není možných.

Frekvence jsou u Epycu 9754 jen 2,25 GHz v základu a 3,1 GHz v boostu. Boost kompaktních jader Zen 4c je tedy mnohem nižší (běžný Epyc 9654 má boost 3,7 GHz), ale základní frekvence už tolik netrpí (u té je to redukce jen o 150 MHz proti běžnému modelu), takto nízké pásmo už není pro jádra jinak rezignující na vyšší takt problém. TDP je 360 W.

Vedle tohoto modelu je znám ještě nižší levnější procesor Epyc 9734, který má v každém CCX jedno jádro vypnuté, což mu ponechává 112 jader a 224 vláken. Jeho frekvence jsou ještě o něco snížené – na 2,20 GHz v základu a 3,0 GHz v boostu. Tento model má TDP 340 W. Oba procesory podporují 12kanálové paměti DDR5–4800 (čímž myslíme 64bitové kanály, které jsou ale u DDR5 reálně tvořeny vždy dvěma 32bitovými kanály – paměti tedy mají šířku 768 bitů, pokud nepočítáme ECC, které je ale také podporované). Použitý je stejný socket SP5 jako u Epyců 9004 „Genoa“, obě CPU by měla být kompatibilní na úrovni platformy a serverů (jen je asi pro kompatibilitu s Bergamem u existujících serverů třeba aktualizovat firmware).

Jádro s nízkou frekvencí může být užitečné v MT úlohách

Specifikace těchto serverových procesorů už asi mohou ukazovat, k čemu by jádro Zen 4c nebo jeho následníci mohlo být dobré v procesorech pro PC. Na první pohled je problém, pokud by dosahovalo taktů třeba jen 3 GHz místo 5+ GHz u desktopového Zenu 4.

Nicméně tato maximální frekvence je nejvíce důležitá po jednovláknové aplikace. Hlavně v noteboocích se ale v mnohovláknových zátěžích frekvence procesoru výrazně zredukuje a může se dostat na úrovně, které už dokáže obsluhovat toto zmenšené jádro Zen 4c, například ty 3 GHz. Pokud se tedy v takovéto situaci zapojí vedle klasických jader Zen 4 další jádra Zen 4c, nemělo by to vůbec ničemu vadit, pokud je jejich IPC skutečně stejné – výkonnostní charakteristika z pohledu programu zůstane stejná, a software tedy nemusí nijak řešit rozdíly jako u jader P-Core a E-Core od Intelu. Jen je třeba zajistit, aby operační systém používal tato jádra až v mnohovláknových zátěžích a v málovláknových programech a hrách preferoval velká jádra s vyšším taktem.

Mohl by tedy vzniknout hybridní (big.LITTLE) procesor, který bude mít část jader Zen 4, které budou schopné v jednovláknových aplikacích a ve hrách (ty by těchto jader ale potřebovaly víc, tak 6–8) běžet na vysokých taktech. Další část jader Zen 4c bude čekat na příležitost v mnohovláknových aplikacích, v nichž kvůli omezenému TDP tak jako tak klesne frekvence a jak Zeny 4, tak Zeny 4c se potkají na zhruba stejném taktu třeba někde okolo těch 3 GHz. Ideální výsledek by byl, kdyby jádra Zen 4c byla schopná na tomto taktu běžet s nižší spotřebou než velký Zen 4 (jinak by byla výhoda jen v nižších výrobních nákladech).

Zen 4c v lowendovém Ryzenu 7000?

Podle některých indicií by zřejmě tento princip mohl být poprvé vyzkoušen v levném procesoru „Phoenix 2“, kde by to ale bylo v mnohem menším měřítku. Tento SoC má patrně jen dvě velká jádra Zen 4 (takže hlavně pro jednovláknové aplikace, pro hry už to může být málo) a k tomu čtyři malá Zen 4c. Je ale možné, že u nich nebude toto označení použito, protože vychází ze serverové role (c jako cloud).

Více: Změna paradigmatu v procesorech AMD. První big.LITTLE Ryzen bude APU Phoenix 2

Na těchto levných procesorech by už asi mohlo být vidět, jakých Zen 4c může reálně dosahovat taktů, jak vhodný pro notebooky je a zda by případně mohl být použitelný i v desktopu. Tam to pro něj už bude obtížnější, protože nejvýkonnější Ryzeny 7000 mají i all-core boosty okolo 5 GHz, byť za to platí velmi vysokými spotřebami v mnohovláknové zátěži (limit PPT až 230 W).

Zdroje: Tom's Hardware, SemiAnalysis