Microsoft je významné jméno v softwarové oblasti a věnuje se i některým oblastem hardwaru (jako jsou myši, klávesnice, tablety a notebooky). Už bychom ale od této společnosti nečekali, že se pustí přímo do ústředních komponent počítačů, což je ale přesně to, co nyní oznámila. Microsoft ve své experimentální divizi vyvinul vlastní architekturu mikroprocesorů s vlastní instrukční sadou. Která se výrazně odchyluje od klasických dnes používaných CPU. Tato architektura se jmenuje E2 a Microsoft Research na ní pracoval už delší dobu , přičemž po jistou dobu na projektu probíhala spolupráce také s Qualcommem. Architektura E2 se značně liší od dnes využívaných klasických instrukčních sade a jader procesorů (ať už x86, ARM nebo Power, MIPS). E2 staví na architektuře typu Explicit Data Graph Execution („EDGE“).

Architektura Explicit Data Graph Execution

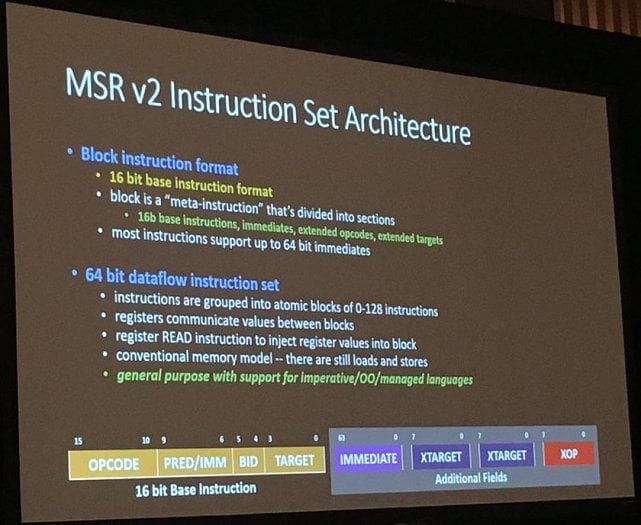

EDGE se od od klasických procesorů s vykonáváním instrukcí stylem out-of-order liší v několika věcech. Instrukční sada se trošku podobně jako VLIW více spoléhá na práci překladače softwaru, který při tvorbě binárky programu má za úkol rozdělovat kód programu do více samostatných celků (označených jako „hyperbloky“), které by explicitně zaručovaly procesoru, že je může provádět paralelně. Typické out-of-order CPU si tyto možnosti k paralelizaci hledá samo při vykonávání programu, ale překladač může nad kódem provést rozsáhlejší analýzu a měl by být schopen lepších výsledků optimalizace. U EDGE by tedy mělo obojí spolupracovat.

Kromě toho by zřejmě také architektury typu Data Graph měly v programu kódovat více informací o prováděném kódu, které by procesoru pomáhaly efektivně jej zpracovávat. Jedním ze zlepšováků by mělo být to, že by zkompilovaný kód měl explicitně zachovávat informaci o tom, jak data procházejí programem, takže procesor by měl přímo signalizováno, že výstup určité instrukce následně tvoří vstup další instrukce.

Toto je v zkompilovaných programech pro konvenční CPU problém – místo explicitních závislostí je totiž program přeměněn na operace s registry CPU, které ale jsou využívány pořád dokola a nenesou přímo původní informaci o tom, odkud kam data jdou. Pro procesor je pak velmi komplikované řešit různé možné kolize a hlídat to, aby někde nebyla použita nesprávná data nebo registry nebo čtení a zápisy nebyl provedeny ve špatném pořadí (což se označuje jako tzv. hazard).

Tato obtíž velmi komplikuje out-of-order vykonávání instrukcí a také načítání a ukládání dat do paměti (tedy operace load/store) a brání tím vyšší paralelizaci a zvýšení IPC procesoru. Architektury Data Graph by v tomto ohledu ideálně měly fungovat lépe a dosahovat vyššího IPC – při stejné frekvenci by měly dokázat zpracovat více operací za jeden cyklus. Zatímco konvenční out-of-order jádro naráží na různé bottlenecky tohoto typu, EDGE by mělo být schopné posunout výkon dál. Při vykonávání na procesorech EDGE by také měly být izolovaná data různých hyperbloků od sebe v privátních registrech, takže by mezi nimi bylo zabráněno konfliktům nebo blokování. Mezi hyperbloky by pak pomocí společných globálních registrů byly předávány jen finální výsledky.

Na experimentální CPU byly portovány Windows

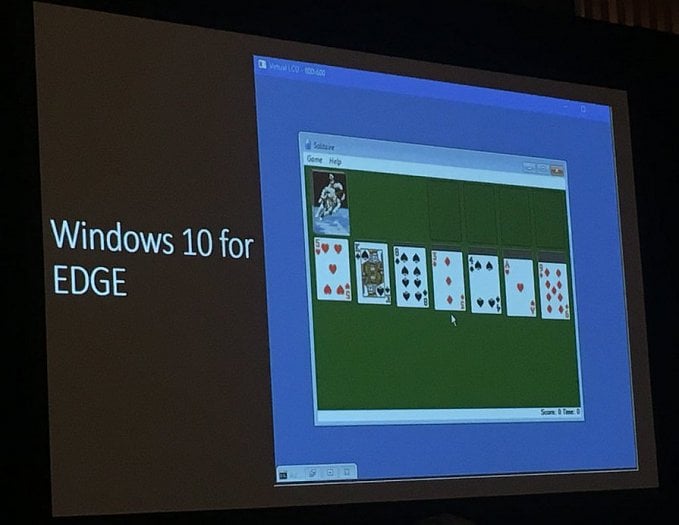

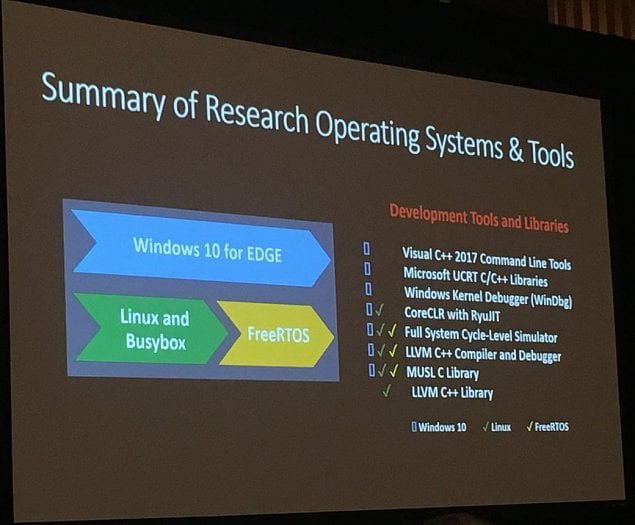

Microsoft s Qualcommem architekturu E2 prezentovali na International Symposium on Computer Architecture, kde byl naživo prezentován běžící simulátor architektury. Ovšem co je zajímavější, firma na tuto architekturu už naportovala poměrně dost softwaru a na konferenci byl ukázán systém Windows 10 bežící na simulovaném E2. Kromě toho ale byl na E2 naportován také Linux s nástroji a shellem BusyBox a také FreeRTOS. Pro architekturu existují i vývojářské nástroje včetně kompilátorů MSVC a LLVM schopných pro E2 překládat kód ve standardním jazyce C++. Architektura má také na Linuxu a Windows podporu .Net skrze port CoreCLR.

Zatím E2 běží jen v čipech FPGA

Tento projekt není podle Microsoftu zatím určen ke komerčnímu nasazení a zatím tedy asi nehrozí, že by takovéto procesory bouraly zažitá paradigmata (a ekosystémy) v praxi. Účel projektu je experimentální a možná by se dalo říct akademický. Procesory s instrukční sadou E2 dnes fyzicky jako hotové čipy neexistují, Microsoft je má implementované v FPGA. V nejmenovaném poli od firmy Xilinx údajně dokáže dvoujádrový procesor E2 běžet na taktu 50 MHz. Ve spolupráci s Qualcommem ale údajně byly studovány dvě regulérní implementace: jedno menší jádro mobilní kategorie s architekturou out-of-order označené „R0“ a výkonnější jádro „R1“, které mělo při implementaci na 10nm procesu běžet na frekvencích vyšších než 2 GHz. Zda ale tyto plány ještě budou realizovány, je ale spíš pochybné, Qualcomm se údajně z tohoto projektu stáhl, dost možná v rámci letos přijatých úsporných opatření.

Microsoft uvádí, že výsledky projektu E2 budou použité v dalších výzkumech, zároveň ale webu The Register sdělil, že nechce „vytvářet očekávání, že by konkuroval existujícím výrobcům čipů“, a část dokumentů o architektuře E2 kvůli tomu odstranil ze svého webu. To je pozoruhodné, protože čistě akademický výzkumný projekt by snad u výrobců procesorů žádné obavy vzbuzovat neměl.

Koncepce budoucnosti?

Architektura typu EDGE by ale mohla být docela efektivní a výhodná, pokud bychom měli opustit stávající instrukční sady a nebyli vázáni kompatibilitou s existujícím katalogem softwaru. Její kód je totiž blízký tomu, jak se zdrojovým kódem stejně pracují kompilátory, tudíž by nemělo být tak komplikované pro tyto CPU kód analyzovat a optimalizovat. To, že kompilátor signalizuje procesoru různé pomůcky pro efektivní optimalizaci a paralelizaci je také výhoda. EDGE by přitom ale neměl mít slabiny koncepce VLIW: jádro samo stále může provádět vlastní out-of-order optimalizaci a není závislé jen na tom, jak kód přeloží kompilátor. EDGE/E2 také stále může používat out-of-order optimalizace k tomu, aby kompenzovalo prostoje při čekání na data z paměti a cache, což je u VLIW problém. Tím pádem může kód být přenositelný na odlišně navržená jádra s touto instrukční sadou podobně jako u konvenčních CPU architektur.