V Číně mají nyní nejistou situaci okolo dostupnosti západních technologií včetně architektury a jader ARM, jinde na světě se zase ohlíží na licenční poplatky (a případně na hrozbu potenciálního odkoupení ARMu problematickým novým majitelem). Z těchto důvodů plus dalších jako je upravitelnost se čím dál víc firem (a států, vedle Číny například i Indie) poohlíží po alternativní instrukční sadě RISC-V.

Ta zatím získává body jen v embedded a mikrořadičích, kde není moc vidět, ale vypadá to, že by se přes jistou nezralost mohla možná právě kvůli politice teď dostat výš. Náskok ARMu ve výkonu je sice značný, ale firma Alibaba (respektive její dceřiná firma T-Head, ny vývoj čipů zaměřená) teď představila první už docela zajímavě vypadající jádro: Xuantie-910, s kterým RISC-V zdá se dospěl do podoby, kdy už může konkurovat sice staršímu, ale docela použitelnému „big“ out-of-order jádru ARM, Cortexu-73. Což jako začátek není špatné. T-Head má mimochodem pro různá méně náročná použití také další jádra 902, 903, 907 a 908, ta ale nebudou tak výkonná, spíš asi půjde o konkurenci Cortexů M.

Out-of-order vícejádro RISC-V

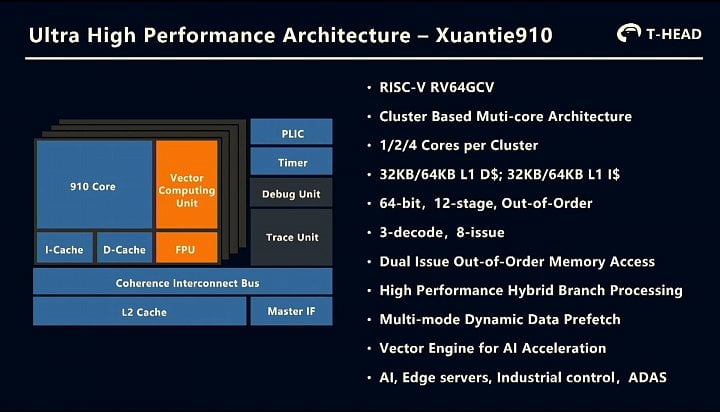

Xuantie-910 je architektura zamýšlená k implementování do vícejádrového procesoru, přičemž takové CPU by se skládalo ze čtyřjádrovcýh klastrů tvořících základní stavební kámen (něco jako čtyřjádrový CCX u AMD Zen neo čtyřjádrové klastry). Každé jádro má 32 nebo 64 KB L1 cache pro kód a 32 nebo 64KB L1 pro data. L2 cache s kapacitou až 8 MB už je sdílená na úrovni čtyřjádrového klastru. Toto je stejné jako u starších ARM Cortexů (A15, A57, A72), dnes už místo toho ARM používá jinou architekturu i s L3 cache. Klastrů může být až čtveřice, takže maximálně lze z Xuantie-910 vytvořit šestnáctijádro.

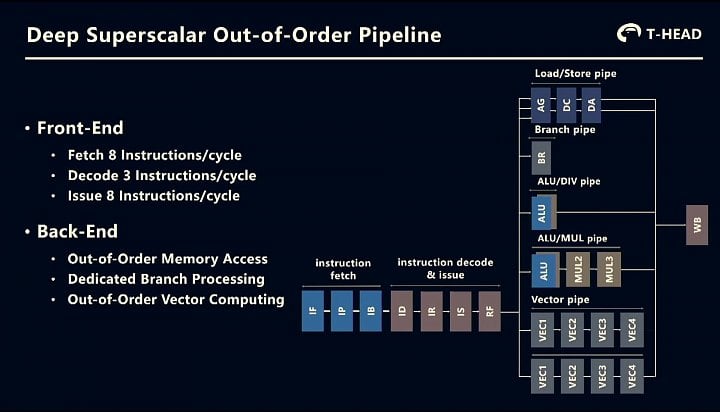

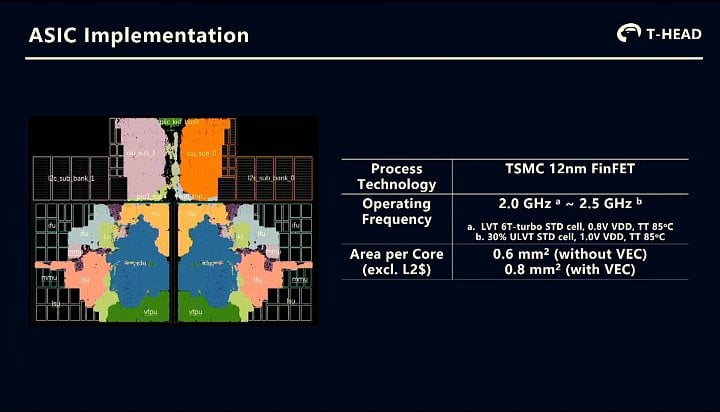

Jádro je 64bitové, superskalární a typu out-of-order (tedy provádějící instrukce v pořadí optimalizovaném pro maximální výkon a paralelismus, nikoliv v jejich původním pořadí). Má 12stupňovou pipeline, což je podobné Cortexu-A73. Respektive, hloubka pipeline je 9 (jednoduché operace ALU, větve) až 12 (FPU/SIMD) stupňů. U Cortexů jsou s takovouto pipeline teoreticky dosažitelné frekvence někde v pásmu nad 3,0 GHz (náš odhad), ale toto závisí i na jiných věcech. T-Head uvádí jako modelovou frekvenci jádra Xuantie-910 na 12nm procesu TSMC jen 2,0 až 2,5 GHz, což je blíže taktu, na kterém Cortexy-A73 fungovaly v mobilech.

Jádro je dual-issue, má v jádru dvě ALU (jedna z nich umí násobená), jednu jednotku pro větve, dvě load/store jednotky, FPU má dvě pipeline. Fáze issue dokáže odeslat do jednotek až osm operací za cyklus, dekódování instrukcí je všem stavěno jen na tři instrukce za takt. Fetch může z instrukční L1 na začátku celého procesu dodat až 8 instrukcí (zřejmě při použití komprimovaných, protože velikost fetche je 128 bitů).

Procesory RISC-V konečně dostávají SIMD

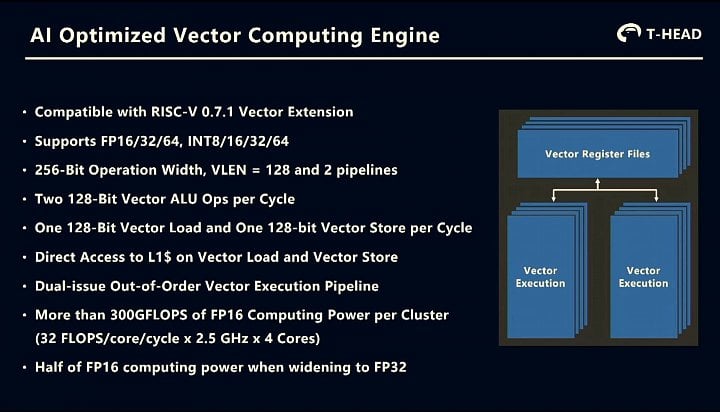

Speciální je Xuantie-910 tím, že podporuje instrukce SIMD (vektorové), jako jedno z prvních jader RISC-V. Jeho dvě FPU pipeline podporují rozšíření Vector Extension 0.7.1 (finální verze nebyla v době návrhu ještě hotová). To dokáže pracovat a hodnotami FP64, FP32 a FP16 a INT8, INT16, INT32 a INT64. Obě vektorové jednotky mají šířku 128 bitů, což by měla být i šířka vektoru – jde tedy o instrukce srovnatelné s rozšířeními SSEx u x86 a NEON u ARMu.

Celkově tedy CPU podporuje instrukční sadu RV64GCV. SIMD instrukce jsou prakticky nutná součást procesoru pro obecné využití, protože bez nich víceméně nelze provádět efektivně multimediální kód a jiné náročnější výpočty. V současnosti mezi to spadá také běh AI aplikací, které jsou také uváděné jako jedno z využití těchto instrukcí. Podporou SIMD rozšíření tedy toto jádro představuje určitý milník.

RISC-V Turbo

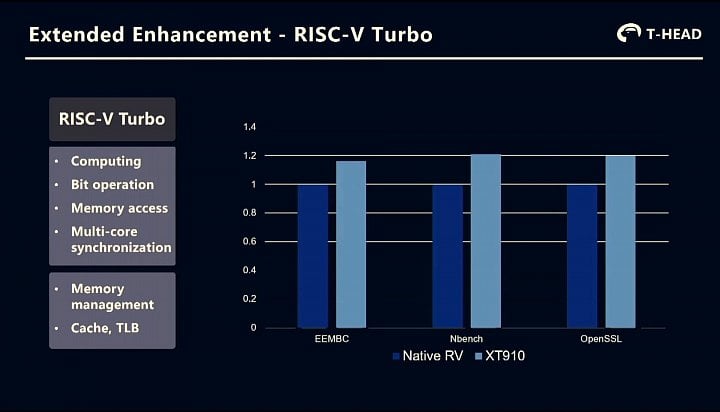

S tím se Alibaba ještě nespokojuje a protože instrukční sada RISC-V postrádá mnoho funkcí přítomných v dospělejších CPU, má jádro přidáno množství dalších rozšiřujících intrukcí. Ty mají označení „RISC-V Turbo“ a dají se v případě nutnosti vypnout pro striktní kompatibilitu s se standardní instrukční sadou. RISC-V Turbo obsahuje instrukce pro manipulace s bity, přístup do paměti a její správu, synchronizaci mezi více jádry a další. Obecně má použití těchto instrukcí navíc procesor zrychlit až o 20 %.

Implementace na 12nm procesu s FinFETy

Jádro má hybridní prediktor větvení s několika módy, pokročilý prefetch do L2 a L1 cache a load/store pipeline provádějí stejně jako zbytek jádra operace stylem out-of-order. Jádro na 12nm procesu TSMC údajně potřebuje jenom 0,6 mm² bez jednotek SIMD a 0,8 mm² s podporou SIMD (v tomto není zahrnuta plocha sdílené L2 cache).

12nm verze čipu má být zpátky z továrny příští měsíc, takže zatím ještě nejsou reálné výsledky, ale implementace na 28nm procesu TSMC (typu 28HPC) údajně dosáhla 1,6 GHz s napětím 1,0 V. Implementace v FPGA běží na 200 MHz.

Zatím nejvýkonnější RISC-V, výkon by měl překonávat ARM Kirin 970

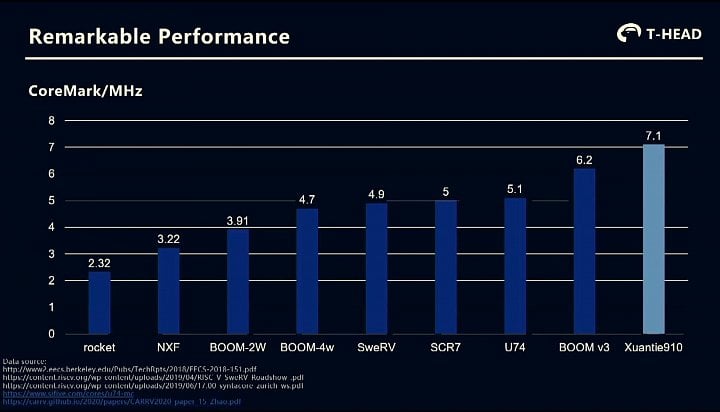

Podle autorů má jádro Xuantie-910 momentálně nejvyšší výkon s jader RISC-V dostupných na trhu, má dosahovat IPC asi 7,1 CoreMarů na 1 MHz, zatímco třeba SweRV od Western Digital dosahuje jen 4,9. Teoreticky by možná mohla být výkonnější architektura U84 od SiFive, ale ta je zatím ve vývoji a moc se o ní neví. Až jeho derivát U87 ale bude mít SIMD.

Tip: Konečně výkonné jádro RISC-V: SiFive U84 je out-of-order a lepší než ARM Cortex-A72

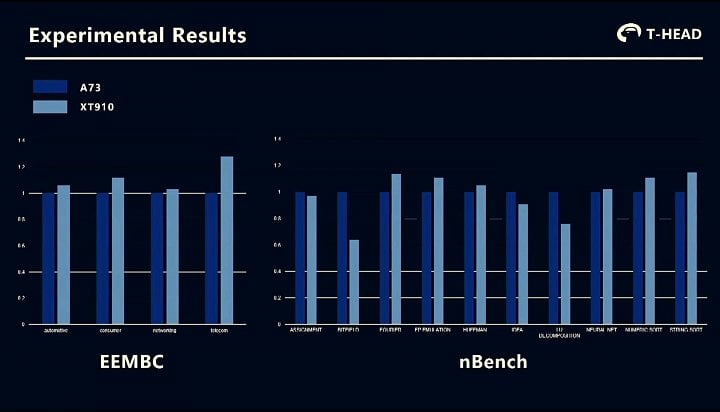

Alibaba srovnává jádro Xuantie-910 s Coretexem-A73, konkrétně s jeho verzí v čipu Kirin 970 od čínského HiSiliconu (Huawei). V předvedených benchmarcích je výkon zhruba srovnatelný, někde RISC-V procesor vede, ovšem jeho autoři upozorňují, že je pořád ještě mladý a mnohde by bylo co vylepšovat.

T-Head/Aliababa podle prezentace tuto architekturu zatím nemíří do mobilních aplikací nebo klientských počítačů, ale chce ji aplikovat jako embedded jádra pro různé produkty/SoC, edge servery, průmyslové aplikace a automobily. Je tedy nejisté, že se dostane do takových procesorů, které by se daly v nějaké formě a zařízení běžně koupit. Je nicméně možné, že dojde k určitému uvolnění pro další klienty, nebo dokonce ve formě open source, takže by pak jádro mohly mít procesory dalších firem, které se třeba o něco zasahujícího do spotřebitelské oblasti pokusí.

Galerie: Prezentace architektury RISC-V procesoru Alibaba/T-Head Xuantie-910 na HotChips 32

Zroje: AnandTech, NextPlatform