Total Compute Solution 23

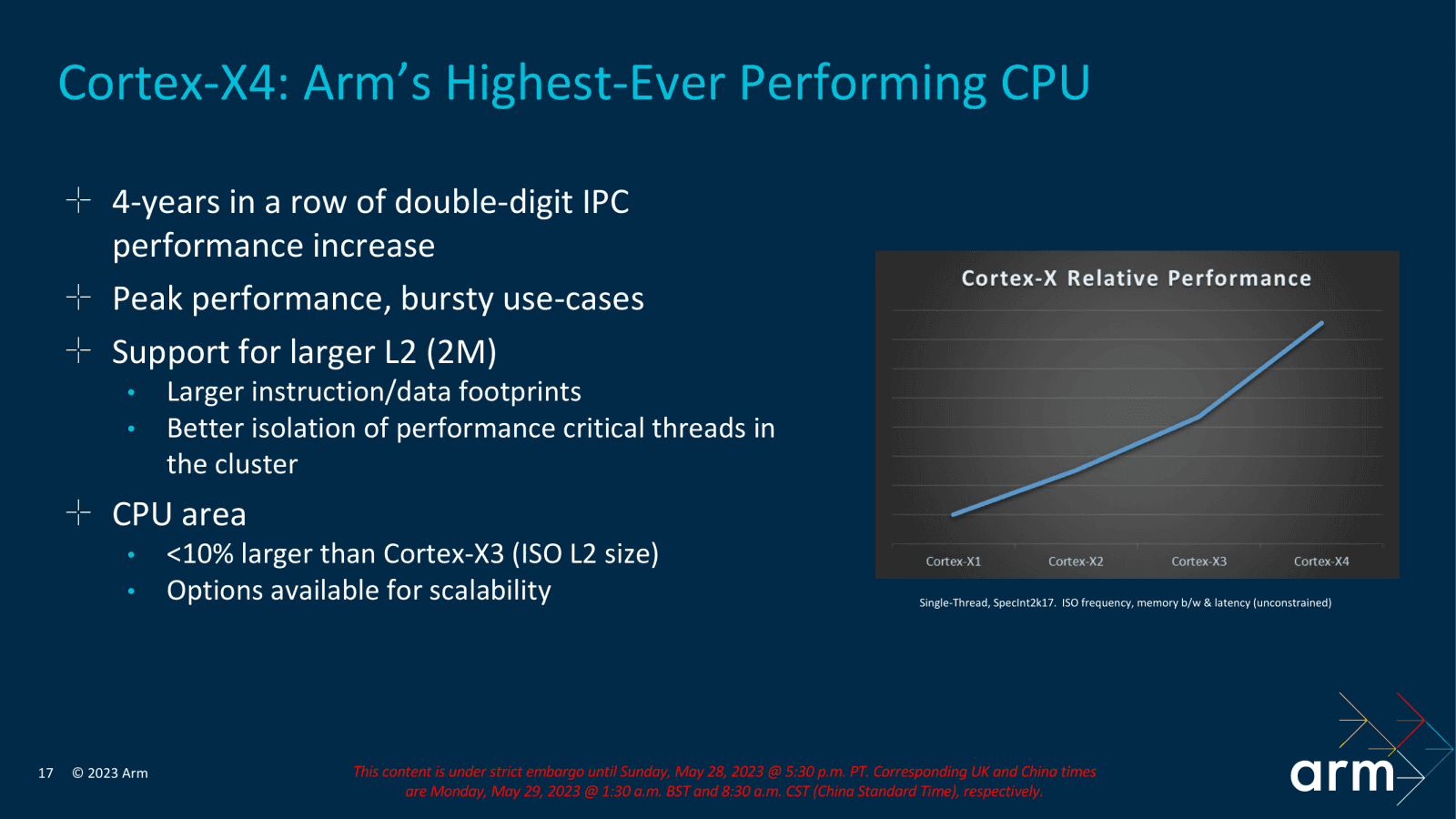

ARM poslední dobou uváděl každý rok novou generaci procesorových jader. A nejinak tomu bude letos, jen tentokrát tuto akci přesunul na veletrh Computex. ARM tam tento rok odhalil kompletní linii nových architektur: nové velké „prime“ jádro Cortex-X4 pro maximální jednovláknový výkon, nové prostřední jádro Cortex-A720, jehož rolí je generovat mnohovláknový výkon (jako E-Core Intelu), a konečně i nové malé úsporné jádro Cortex-A520.

ARM celému „ročníku“ CPU jader spolu s propojovací logikou a dalším IP pro ně (například GPU) říká „Total Compute Solution“ (TCS), ten letošní je „TCS23“. Tato série je první kompletně založená jen a pouze na architektuře ARMv9. Minule ještě ARM částečně zachoval zpětnou kompatibilitu u jádra Cortex-A510, nyní už jsou všechna jádra čistě 64bitová na bázi ARMv9.2 bez kompatibility s 32bitovým softwarem.

Cortex-X4 míří na vyšší výkon, zbylá jádra na lepší efektivitu

Architektura ARMv9.2 má zajímavé novinky zejména pro bezpečnost. Technologie Memory Tagging Extension z předchozích generací by měla mít zlepšený výkon díky použití funkce QARMA3, což je nový algoritmus provádějící autentifikaci ukazatelů (pointerů). Údajně snižuje výrazně negativní dopad této bezpečnostní funkce na výkon programů, zpomalení s ní má být až na úrovni nižší než 1 %.

Článek pokračuje na další straně.

Cortex-X4: Nejširší out-of-order jádro v historii ARMu

Nejvýkonnějším jádrem v generaci bude zase Cortex-X4, navazující na předchozí Cortex-X3. Toto jádro bude mít v mobilech za cíl poskytnout jednovláknový výkon, a často proto v SoC bude jen jednou (v čipech pro notebooky to může být jiné). Je to proto, že toto jádro není vyladěné na maximalizaci poměru výkon/plocha a poměru výkon/spotřeba.

Cortexy linie X jsou navržené tak, aby měly co nejvyšší jednovláknový výkon i za cenu toho, že se energetická efektivita a efektivita co do zabrané plochy na čipu zhorší. Zatímco tento přístup pomáhá jednovláknovým aplikacím, mnohovláknové aplikace by v určitém limitu spotřeby se samými jádry Cortex-X dopadly hůře, než pokud by se použilo několik (nejspíše víc) prostředních jader Cortex-A se stejnou spotřebou. Tato jádra jsou tedy specializována na odlišné scénáře a v hybridní architektuře se doplňují. Nebo taková je alespoň teorie.

ARM Cortex-X4

Cortex-X4 je dosud nejvýkonnějším jádrem, které ARM navrhl. Tak je tomu u těchto jader samozřejmě každoročně tím, jak výkon mezigeneračně pořád stoupá. Ale v tomto případě nejde jen o praktický výkon. Jádro je skutečně radikálně silnější (širší) co do architektonické koncepce, ve které jde výrazně dál než cokoliv před ním.

Víc ALU než Apple

Toto jádro má rovnou osm jednotek ALU pro celočíselné operace (proti šesti v Cortexu-X3 nebo v jádrech Applu a stále jen čtyřem v AMD Zenu 4). Šest ALU je pro běžné jednoduché instrukce s latencí jeden cyklus, dvě další jsou schopné provádět složitější vícecyklové instrukce a mají funkcionalitu celočíselné MAC (u Cortexu-X3 ji měla jen jedna jednotka ALU). Celočíselná dělička je stále jen v jedné z komplexních ALU. Současně byl navýšen i počet jednotek pro větvení, které jsou separátní – ze dvou na tři (zde je to také víc než u Applu a Zenu 4, kde jsou jen dvě).

ARM Cortex-X4

Také load-store část je rozšířená ze tří jednotek AGU na čtyři. Je možné zpracovat dvě čtení a dva zápisy do paměti za cyklus, nebo tři čtení a jeden zápis (jedna jednotka je univerzální load/store, dvě umí jen load operace a jedna, která je nová, pouze store).

ARM Cortex-X4

Naopak v FPU zřejmě jednotky nepřibyly, stále má jen čtyři pipeline, a zřejmě také SIMD pipeline pořád mají jen 128bitovou šířku vektorů (oproti 256– až 512bitovým šířkám jednotek u x86 procesorů). Výkon instrukcí Neon a SVE/SVE2 tedy asi moc nenaroste (pokud mu nepomohou zlepšení v jiných částech jádra). Větší změna proti Cortexu-X3 je, zdá se, jen v tom, že floating-point dělička bude nově pipelinovaná (dříve nebyla), což výkon těchto instrukcí o dost zvýší. Jejich použití ale není zas tak časté, protože z důvodu vysoké ceny těchto instrukcí se jim programátoři při optimalizaci obvykle snaží vyhýbat.

Jádro už má osm dekodérů, zcela upouští od uOP cache

Na rozšíření jádra ale ARM sází i v dalších fázích, zejména ve frontendu. Procesor má rovnou osm paralelních instrukčních dekodérů, což je také rekord (Apple má také osm dekodérů). Tyto dekodéry dokáží dodávat dalším fázím zpracování osm instrukcí za cyklus. Dispatch pak podporuje až 10 micro-opů za cyklus (ne všechny instrukce se dekódují na jeden micro-op).

Zdá se, že ARM také zkrátil pipeline procesoru, což jde trochu proti evolučnímu trendu ostatních architektur, kde bývají přidávány další stupně (což přesněji znamená, že se fáze zpracování, které v kratší pipeline udělají v jednom cyklu, rozloží do více cyklů). Cortex-X3 měl 11stupňovou pipeline (což bylo množství cyklů, které stálo špatně odhadnuté větvení – byť při získání mikroopů z uOP cache byl postih jen 9 cyklů). Oproti tomu Cortex-X4 má postih vždy jen 10 cyklů a 10stupňovou pipeline.

Více stupňů obvykle jádrům CPU umožní dosáhnout vyšší frekvence, ale roste postih za špatně odhadnutá větvení a s frekvencí také spotřeba. To, že ARM pipeline zkracuje, zřejmě přispívá k vyššímu IPC jádra při nízké spotřebě, bude to ale za cenu nízkého frekvenčního stropu.

ARM Cortex-X4

Zmíněnou micro-op (uOP) cache, která cachuje micro-opy (už dekódované instrukce), Cortex-X4 zrušil, což je poměrně zásadní změna. Naznačená ale byla už v Cortexu-X3, který ji redukoval. O co jde? Například u procesorů x86 jsou dekodéry kvůli komplikovanosti instrukční sady hodně komplexní a mají i vyšší spotřebu, kvůli proměnlivé délce instrukcí je také těžší jich mít více paralelních. Intel a AMD na to reagovaly tak, že zavedly novou cache (uOP, micro-op cache), která cachuje již dekódované instrukce. Využívá se toho, že procesor zpracovává stále se opakující smyčky, kdy je možné přeskočit dekódování a vzít dekódovanou instrukci z předchozího průchodu. Uvádí se, že hit rate těchto cache může být třeba až 80 %, takže ony problémy a limity x86 dekodérů reálně z 80 % výpočetního času neexistují.

Apple micro-op cache nikdy neměl, ale ARM ji u jader Cortex-A77 až X3 používal, protože zřejmě stále snižovala spotřebu přesto, že je instrukční sada ARM na dekódování snazší. Prý se to ale změnilo s tím, když byla odstraněna podpora 32bitové instrukční sady a jádro už je čistě ARMv8/ARMv9. To značně zmenšilo plochu dekodérů, a jádro Cortex-X3 jich proto použilo víc a micro-op cache se zmenšila. Teď to ARM vzal do důsledku a kompletně vyměnil tuto cache za další dekodéry.

Jak už bylo zmíněno, dekodérů je osm a dokáží zpracovat osm instrukcí za cyklus a dodat z nich až 10 operací do dalších fází zpracování (tzv. dispatch). Cortex-X3 měl maximální výstup šest operací za cyklus z dekodérů nebo osm operací z uOP cache. Předchozí fáze fetch, která bere instrukce z L1 instrukční cache a posílá je do fronty dekodérům, je také nově vylepšená a dodává až 10 instrukcí za cyklus.

Pokročilost out-of-order architektury není měřená jen touto „šířkou“ (počtem paralelních jednotek), ale také hloubkou bufferů či front procesoru. V těchto frontách procesor může řadit a přehazovat operace a zlepšovat tak výkon tím, že optimálně vytíží co nejvíce jednotek najednou. To jde tím lépe, s čím větším „oknem“ kódu může procesor pracovat. Toto okno se obvykle pojmenovává ReOrder Buffer (ROB), ARM mu u tohoto jádra říká Micro-op Commit Queue (MCQ). Cortex-X4 hloubku této fronty zvětšil o 20 % – z 320 na 384 instrukcí (respektive v této fázi micro-opů). Pokud jsou dva micro-opy spojené v předchozí fázi zpracování (fused), zabírají jen jednu položku, proto ARM uvádí, že kapacita MCQ je 384 × 2. Neznamená to ale, že „okno“ má 768 položek. Pro srovnání – v AMD Zen 4 má ROB jen 320 položek (AMD v tomto je hodně minimalistické, Zen 3 měl jen 256), naopak Intel Golden Cove / Raptor Cove už 512 položek a u jader Apple by zřejmě hloubka měla být přes 600 (to jsou neoficiální odhady, protože firma sama nic nezveřejňuje).

ARM Cortex-X4

Větší L2 cache bez vyšší latence

Procesor má také vylepšené prediktory větvení, u kterých bylo obzvlášť zapracováno na podmíněných větvích. Stejně tak byly vylepšené prefetchery. Obojí je oblast, ve které bývají inkrementální zlepšení u všech nových architektur, a toto jádro není výjimka. Cortex-X4 dostal nový temporální prefetcher do L1 cache a L1 cache by měla mít snížený výskyt konfliktů mezi banky. Byl také zvětšen L1 TLB pro data ze 48 na 96 položek.

Další zlepšení je podpora pro 2MB L2 cache, která byla ve fyzickém návrhu přiblížena více k vykonávacím jednotkám a zřejmě díky tomu jí byla zachována stejná latence přes vyšší kapacitu. Díky tomu by snad měla přinášet čisté zlepšení výkonu na 1 MHz bez regresí v některých algoritmech, které jsou na latenci závislé, ale neprofitují z vyšší kapacity. U L2 cache byla také upravena politika plnění a nahrazování dat.

Ačkoliv jádra Cortex-X3 nejsou, jak už bylo řečeno, optimalizována na co nejmenší plochu, toto kritérium je u designů ARMu (oproti třeba jádrům Apple) všude dost akcentované. To je asi dáno preferencemi výrobců mobilních SoC, kteří jsou pod cenovým tlakem a výrobní náklady čipu jsou pro ně na rozdíl od Applu důležité. Cortex-X4 je tedy pořád poměrně malý, podle ARMu bude potřebovat jen o asi 10 % větší plochu než předchozí Cortex-X3 (při použití stejného výrobního procesu a stejné kapacity L2 cache).

IPC a výkon

Výsledkem toho celého má být jádro, které má mít až o zhruba 15 % lepší „IPC“ neboli výkon na 1 MHz frekvence než Cortex-X3. Tento údaj je při stejném taktu CPU, stejné L3 cache a při stejné propustnosti a latenci použitých pamětí. Je třeba říci, že nejde o výsledky naměřené na reálném hardwaru, ale o simulaci.

Reálně bude nárůst v každé aplikaci samozřejmě jiný. Zdá se, že vyšší nárůsty IPC jsou v mnohovláknových aplikacích (Speedometer2: +24 %), ale v jednovláknových aplikacích naopak může zlepšení být nižší. Geekbench 5 a Geekbench 6 mají zřejmě nárůst IPC jen asi +7 % až +8 %. Nejblíže udávanému průměrnému zlepšení je z úloh, které ARM ukazuje ve slajdech, SPEC2017 (SPECRate2017_int_base), kde je zlepšení IPC o +14 %. Benchmarky SPEC vždy s procesory ARM vykazovaly dobré (a možná nadprůměrné proti jiným úlohám) nárůsty, ať už je důvod jakýkoli.

Projekce výkonu Cortexu-X4

Alternativně má jádro dosahovat stejného výkonu jako Cortex-X3 při až o 40 % nižší spotřebě (díky vyššímu IPC totiž může běžet na nižší frekvenci). V praxi si ale výrobci vyberou místo snížení spotřeby zvýšení výkonu, takže toto se asi nikde moc neprojeví.

Cortex-X4 by podle ARMu měl dosahovat frekvence až 3,4 GHz. Nebude tedy v tomto ohledu škálovat moc vysoko – jak už napovídá malý počet stupňů pipeline – což zase poněkud omezí absolutní výkon. Vysoké IPC je totiž jen jednou částí rovnice. Například jádra Applu už také dosahují vyšších taktů, nemluvě o procesorech Intelu a AMD, které se už pohybují v pásmu 5,5–6,0 GHz, což dává 60–75 % výkonu navíc.

DSU-120

Propojovat tato (a sourozenecká menší) jádra v čipech bude logika DSU-120. Ta bude podporovat celkově až 14 jader a až 32MB L3 cache, kterou budou sdílet. Zřejmě by tedy mohly být dostupné konfigurace jako 4 velká jádra + 8 prostředních jader + 2 malá jádra. Explicitně je podle ARMu podporovaná i kombinace 10 jader Cortex-X4 a čtyř Cortexů-A720, což by mohly používat výkonné notebookové procesory.

Možnosti konfigurace procesorů s jádry Cortex-X4, A720 a A520

Článek pokračuje na další straně.

Cortex-A720: nové prostřední jádro proti E-Core u Intelu

Také Cortex-A715 dostal novou náhradu, pojmenovanou A720. Tato třída jader dříve představovala velká jádra, ale nebyla optimalizovaná až tak moc na jednovláknový výkon, jako spíše na efektivitu a plochu. Poté, co úloha 1T výkonu přešla na Cortexy-X, jsou tato jádra linie Cortex-A specializována zejména na mnohovláknový výkon, jak už bylo řečeno. Takže je můžete vnímat jako obdobu E-Core (nyní architektury Gracemont) u Intelu. V levnějších mobilních SoC ale Cortex-X4 může chybět a Cortex-A720 pak v nich bude mít roli velkého jádra.

U Cortexu-A720 neudělal ARM tak velké změny proti předchozímu designu Cortexu-A715, jaké jste mohli vidět v předchozí kapitole, a jde spíše o evoluční vylepšení. Jádro má být zaměřené zejména na zlepšení efektivity (co do spotřeby, ale i do plochy a ceny). Také přidává podporu instrukční sady ARMv9.2.

ARM Cortex-A720

Cortex-A720 zřejmě stejně jako Cortex-X4 zredukoval délku pipeline, protože cena za chybně odhadnuté větvení byla zredukována ze 12 na 11 cyklů. Vylepšena byla opět i predikce větvení, ovšem asi ne co do výkonu, ale tak, aby zpracování větvení bylo efektivnější z hlediska spotřebované energie (údajně bez negativního dopadu na výkon). Stejně jako Cortex-X4 nemá jádro A720 žádnou micro-op cache, ale v tomto případě byla odstraněna již předchozím jádrem A715.

ARM Cortex-X4, A720 a A520

Cortex-A720 také stejně jako jádro X4 přešel na pipelinovanou floating-point děličku, takže i u tohoto jádra se zlepší výkon instrukcí FDIV. Pipelining byl přidán také pro floating-point výpočet druhé odmocniny (FSQRT). Výsledkem je zrychlení těchto operací (asi jak co do latence této instrukce, tak do propustnosti, čili kolik jich jednotka zvládne za určitý počet cyklů) a zároveň podle ARMu nedošlo k významnému zvětšení plochy děličky.

ARM Cortex-X4, A720 a A520

Jednotka FPU má také zrychlenou práci při převodu hodnot z floating-point a SIMD (Neon, SVE / SVE 2) registrů do obecných integerových registrů. Trvá tedy kratší dobu, než jsou výsledky z těchto instrukcí přístupné pro další zpracování mimo FPU. Předávání dat mezi částmi jádra (forwarding network) bylo zlepšeno také směrem do jednotek AGU provádějících zápis do paměti (cache) a také se zlepšila práce load/store front.

ARM Cortex-X4, A720 a A520

Cortex-A720 má také zrychlenou L2 cache, která má latenci jen 9 cyklů proti 10 u předchozího Cortexu-A715. Minimálně pro některé druhy operací byla vylepšená také její datová propustnost. Podle ARMu totiž operace MemSet v L2 cache probíhají až 2× rychleji.

Jádro má také opět vylepšené prefetechery, což je spolu s prediktory větvení oblast, která bývá kontinuálně vylepšována v prakticky každé nové generaci a má přímý vliv na zlepšení IPC. Jádro by nově mělo mít spatial prefetching do L2 cache, který byl předtím jen u jader Cortex-X.

O trošku lepší výkon, ale hlavně efektivita

Podle ARMu by jádro Cortex-A720 mělo mít výkon vyšší o 1–13 % proti Cortexu-A715, přičemž úlohu od úlohy se to bude lišit (v průměru bude asi zlepšení jen okolo 5 %). Toto by mělo být na stejném výrobním procesu. O něco více má stoupnout efektivita, ta má na stejném procesu být údajně v průměru o nějakých 6 % lepší (v praxi se to ale bude lišit aplikaci od aplikace). Tento rozptyl můžete vidět v grafu pro úlohy benchmarků SPEC.

Zlepšení výkonu a efektivity u Cortexu-A720

ARM u tohoto jádra nabízí několik možností konfigurace, vedle výkonnější možnosti má také existovat verze, která má při implementaci mít zhruba stejnou plochu jako Cortex-A78 (design z roku 2020). Tato konfigurace má nižší výkon, ale stále má být o 10 % rychlejší než toto starší jádro. Jejím smyslem je použití v SoC pro levné telefony, které používají stará jádra jako Cortex-A76 a právě A78. Tato osekaná verze Cortexu-A720 by mohla jejich výrobce přimět, aby konečně přešli na novější architekturu s instrukční sadou ARMv9.

Článek pokračuje na další straně.

Nové malé jádro: Cortex-A520

V minulé generaci nebylo nové malé jádro představeno a místo něho se jádra pořád párovala s předchozím Cortexem-A510. To teď ARM napravuje a vydává nové malé jádro Cortex-A520, u kterého zrovna jsou slibována zlepšení poměrně velká – ale v efektivitě místo v rychlosti. Tato jádra zůstanou stále na relativně nízké výkonnostní úrovni. Stále jde o in-order architekturu, ARM tedy nenásleduje Apple, který svá malá jádra koncipuje jako výkonnější out-of-order jádra netriviálního výkonu.

Cortex-A520 není ale totálně nový design, stále vychází jako ze základu z architektury Cortex-A510, zachovává také její sdílenou FPU. Podporuje instrukce ARMv9.2 a je již čistě 64bitový, nemá tedy již legacy kompatibilitu s 32bitovými aplikacemi. Stejně jako předchozí jádra podporuje Cortex-A520 onen nový algoritmus QARMA3 pro bezpečnostní funkci Pointer Autentification.

ARM Cortex-A520

Zatímco u Cortexu-X4 bylo jádro rozšířeno a u Cortexu-A720 se ARM soustředil na optimalizace efektivity bez rozšíření, Cortex-A520 byl ve jménu efektivity dokonce zúžen. Cortex-A510 zvedl proti Cortexu-A55 počet ALU na tři, ale Cortex-A520 toto revertuje a vrací se jen ke dvěma ALU. Toto zjednodušuje datovou komunikaci mezi jednotkami a issue logiku, takže je ušetřena energie (výkon zřejmě také klesne, ale méně než spotřeba). Část výkonnostního propadu ARM vykompenzoval jinými úpravami, které mají nižší cenu než třetí ALU.

Vedle dvou jednoduchých ALU má jádro jednu jednotku vyhrazenou pro celočíselné dělení a násobení a jednu jednotku pro větvení. Dále pak má jádro jednu load/store a jednu čistě load jednotku, podporuje tedy buď dvě čtení, nebo jedno čtení a jeden zápis do paměti za cyklus.

ARM Cortex-A520

O oněch dalších změnách toho ale ARM zas tak mnoho neříká. Vylepšena byla opět predikce větvení a prefetch, což jsou součásti, které u jakéhokoliv jádra zlepší jeho efektivitu a využití jeho výpočetních zdrojů (hodně se na ně soustředí také třeba AMD, u kterého zřejmě mohou za to, že Zen 4 s menším počtem ALU a dalších jednotek dosahuje cca stejného IPC jako jádra Intelu s výrazně silnějšími výpočetními prostředky i delšími out-of-order frontami).

Jádru zůstaly L1 cache pro data a instrukce s kapacitami volitelně 32, nebo 64 kB a zřejmě zůstala ve stejných rysech také sdílená FPU a SIMD jednotka připomínající řešení FlexFPU u architektur AMD Bulldozer, Piledriver, Steamroller a Excavator. U Cortexu-A510 a A520 je ale možné ji volitelně dát každému jádru vlastní.

Obecně AMR uvádí, že se zaměřil na změny, které zvyšují výkon jádra významně, ale stojí jen málo energie (přičemž třetí ALU zřejmě měla opačný efekt). Také prý byl vyladěn pro větší efektivitu paměťový subsystém (load/store jednotky, fronty a cache).

Křivka výkonu a spotřeby pro Cortex-A520

Podle ARMu má Cortex-A520 až o 22 % vyšší energetickou efektivitu proti jádru A510, pokud se vyrobí na stejném výrobním procesu – znamená to, že na určitý výkon toto jádro dosáhne při spotřebě o 22 % nižší než Cortex-A510. Nebo alternativně dokáže v určité limitované hodnotě spotřeby dosáhnout o 8 % vyššího výkonu.

Toto ovšem nemusí škálovat až na nejvyšší možné frekvence, je možné, že pokud byste chtěli přetaktováním vymáčknout maximum, zastaví se Cortex-A520 níž. To ale není scénář, ve kterém tato jádra budou používána. Tato jádra poběží na nízkých frekvencích v roli jader, kterým budou svěřovány úlohy na pozadí nebo na kterých poběží operační systém v okamžicích, kdy je systém nečinný, čeká na reakci uživatele, nebo běží v úsporném standby režimu.