Intelu se v poslední době moc nedaří s výrobními procesy – tedy ne co do kvality, ale pokud jde o dodržení termínů. Možná si vzpomenete na příchod dnešní 14nm technologie v letech 2014 až 2015. Tehdy nastala kuriózní situace: výrobní proces se natolik zpozdil, že se první generace 14nm čipů pro desktop (Broadwell) dostala na trh jen pár měsíců předtím, než měl Intel hotovou rovnou jejich druhou generaci s novou architekturou, Skylake. Něco podobného nás teď možná čeká na 10nm procesu.

Podle již nějakou dobu dostupných úniků se druhá generace 10nm čipů Intelu jmenuje Ice Lake. Tato CPU jsou pro nás docela zajímavá. Zatímco první 10nm generace Cannon Lake má být hlavně „dieshrinkem“ 14nm Skylake/Kaby Lake na nový proces a nelze čekat výrazné změny, Ice Lake přinese konečně (poprvé od roku 2015) kompletně novou architekturu. Lze od něj tudíž čekat zvýšení IPC a tedy potenciál pro skok v celkovém výkonu.

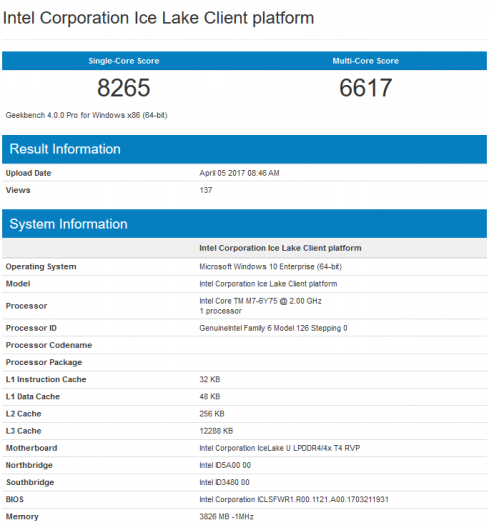

První 10nm generace Cannon Lake se má na trh dostat snad koncem letoška nebo těsně po něm na začátku roku 2018. Ice Lake by tedy za běžného stavu věcí mělo přijít až zhruba o rok později po ní. Teď se však objevil náznak, že by se mohla opakovat situace s Broadwellem a Skylake a čipy Ice Lake by zdaleka nebyly tak vzdálené. Na internetu se už totiž v databázi benchmarku Geekbench vynořil záznam z testování, jenž byl údajně pořízen na procesoru Ice Lake. Pokud nejde o falzum (což nelze vyloučit), pak by to znamenalo, že Intel už má v ruce nějaké vzorky tohoto křemíku. A to přesto, že ještě zbývá zhruba tři čtvrtě roku do uvedení čipů předchozí generace. Možná tedy došlo k tomu, že CPU Cannon Lake byla kvůli nezralosti 10nm procesu odložena o tak dlouhou dobu, že už se postup jejich příprav skoro dotýká s přípravami následujícího Ice Lake.

To, že by byl otestován vzorek čipu Ice Lake možná rok a půl (pokud ne dříve) před uvedením na trh, a ještě by data unikla, je pravda poněkud podezřelé. Na druhou stranu by mohlo jí i o únik cílený. Pokud bychom ale přijali předpoklad, že zde nemáme co do činění s falzem, říká nám Geekbench o Ice Lake některé zajímavé věci. Vzorek má údajně takt 2,0 GHz, neznáme ale počet jeho jader, případně je možné, že při testování bylo aktivní jen jedno. Asi nemá příliš smysl se dívat na rané výsledky jednotlivých benchmarků, zajímavé jsou hlavně údaje z detekce.

Zdá se například, že Ice Lake konečně přinese podporu pamětí LPDD4, které v mobilních zařízeních a ultraboocích čipu dodají velmi vysokou propustnost (dnešní tablety už používají efektivní frekvence třeba 3733MHz). Momentálně ultramobilní Intely podporují stále jen LPDDR3 a jsou tím pádem trošku pozadu – výkonově i technologicky, neboť LPDDR4 díky nižšímu napětí také může potenciálně být úspornější. Testovaná deska, patrně prototypová platforma pro notebooky, měla 4 GB osazené paměti.

Změny v pamětech cache?

Čeho si všimněte, jsou velikosti pamětí cache. L2 cache zůstává na 256 KB. To znamená, že Intel u této architektury asi stále hodlá používat stejnou kapacitu, jakou v roce 2008 zavedl s jádry Nehalem, zatímco u serverového Skylake přešel na 1MB L2 cache. Patrně tedy nejde o trvalou změnu v architektuře a tato větší L2 zůstane jen v serverových procesorech. Verze pro běžné počítače naopak zůstanou na 256 KB, což asi platí i pro Coffee Lake, Cannon Lake a nejspíš Tiger Lake, které bude následovat po čipech Ice Lake coby třetí 10nm generace.

Naopak by se zřejmě mohla zvětšit L3 cache, která má podle Geekbench rovnou 12 MB. Dnešní dvoujádra jí přitom nesou 4 MB, čtyřjádra 8 MB. Že by tedy Intel zvětšil příděl na jedno jádro? Je ale také možné, že tento procesor už má fyzicky šest jader – ačkoliv má asi jít o mobilní verzi, nejspíš odpovídající notebookové řadě U.

Nejpozoruhodnější je ovšem L1 cache. Intel totiž podle těchto údajů (jsou-li pravé atd.) změnil po velmi dlouhé době kapacitu L1 cache. Instrukční část L1 by zůstala na původních 32 KB, což se nezměnilo už 14 let od prvních procesorů Pentium M. Ovšem datová L1 cache by se prý měla zvětšit z 32 KB o 50 % na 48 KB. Jde sice o poněkud nepravidelné číslo, ovšem ne bez precedentu – podobně asymetrická je L1 cache v „Atomových“ architekturách Silvermont/Airmont/Goldmont (32 KB instrukce, 24 KB data).

Zvýšení kapacity datové L1 cache zlepšuje šanci, že procesor najde v cache potřebná data, což by mělo podpořit výkon a také energetickou efektivitu jádra. Je sice možné, že na oplátku vzroste i latence, ale celkově by tato změna stále měla být k lepšímu. Jelikož 48KB cache by asi měla být složená z více banků, asi by proporcionálně mohla vzrůst i její asociativita – místo dnešní 8cestné by pak mohla být 12cestná. I toto by mohlo jádru Ice Lake pomoci k dosažení lepšího IPC (výkonu přepočteného na 1 MHz), což je dnes nejdůležitější faktor pro celkový výkon. Nová architektura Intelu by tak v roce 2018 – či kdy se objeví – mohla být hodně zajímavá.