Jde o dílo vytvořené kolektivem

vědců ze Švýcarského

federálního technologického institutu v Curychu (ETH

Zürich) a Boloňské Univerzity, nazvané PULPino (název je

odvozen od souvisejícího projektu PULP, Parallel ultra low power).

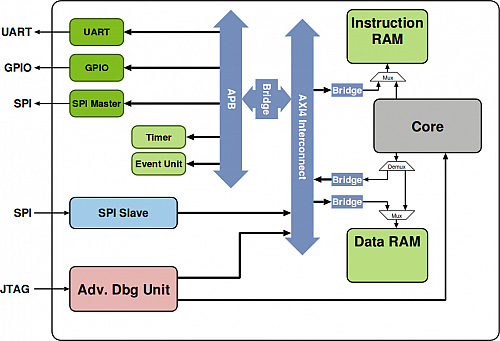

Jak již název naznačuje, PULPino je malý, nepříliš komplexní

procesor, který nebude konkurovat velkým CPU, ale zatím jen

mikrořadičům. Jeho autoři jeho možnosti vidí zejména

v segmentu „IoT“ (internet věcí, nositelná elektronika

jako hodinky a podobně) a různých podobných zařízení

vyžadujících co nejnižší spotřebu.

Zatímco projekt PULP počítá

s čtryřjádrovým SoC (ovšem tam je to nikoli s architekturou

RISC-V, ale OpenRISC, pokud se dobře dívám), PULPino se omezuje na

jedno jádro s označením RI5CY se zjednodušenou instrukční

sadou. Autoři jej srovnávají s Cortexem-M4. Implementována

je základní 32bitová sada RISC-V, komprimované instrukce RV32C

(obdoba instrukcí Thumb u ARMu) a částečná podpora

násobení (RV32M).

Kromě toho by jádro mělo mít také

nestandardní rozšíření pro roli mikrořadiče a částečnou

implementaci privilegované architektury, což umožňuje, aby na

procesorech PULPino běžel FreeRTOS. Procesor se také umí při

neaktivitě přepnout do úsporného režimu, kdy je většina částí

neaktivních pro snížení příkonu a čeká s probuzením

na vnější impulz.

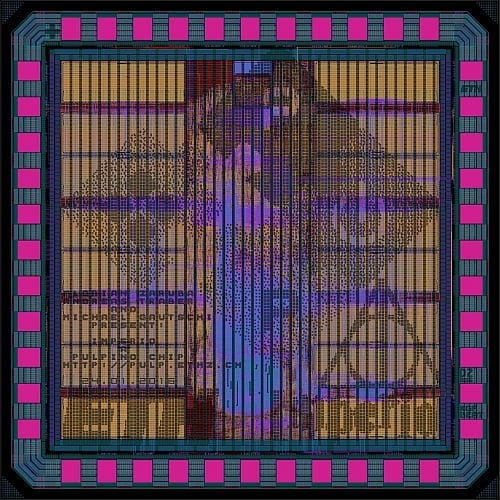

Toto by měl být čip Imperio, první implementace PULPina na 65 nm

PULPino má za sebou tape-out v továrně

UMC, který proběhl v lednu 2016 na 65nm procesu. Není jasné,

zda se počítá i s nějakou reálnou výrobou (a poté

prodejem těchto čipů), která by zřejmě nastala až v případě,

že by se našli nějací uživatelé. Tato první implementace

procesoru, nazvaná „Imperio“ má údajně dosahovat taktu až

650 MHz. Na typickém taktu 400 MHz při napájecím napětí

1,2 V má mít příkon jen 32,8 mW. Jádro RI5CY má měřit

0,050 mm² a údajně by na 65 nm mělo být o něco menší

a snad i úspornější než Cortex-M4. Imperio

implementuje pro komunikaci s okolím rozhraní jako UART, I2C, SPI

Master a GPIO.

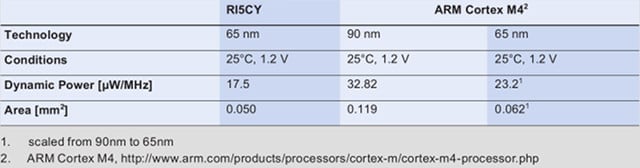

Jádro RI5CY ve srovnání s ARM Cortex-M4

Kromě této implementace lze čip

simulovat v RTL nebo naprogramovat do v FPGA (Xilinx

Zynq-7010). Zdrojové kódy samotného hardwaru i softwarových

nástrojů by měly být dostupné pod licencí Solderpad

Hardware License, podobné licencei Apache 2.0. Tím pádem je

také možná návrh využít ve vlastních čipech. Celý projekt má

své stránky

a repozitáře na GitHubu a v rámci Google Summer of

Code běží i softwarové projekty pro tuto platformu,

například přidání podpory do Arduina.

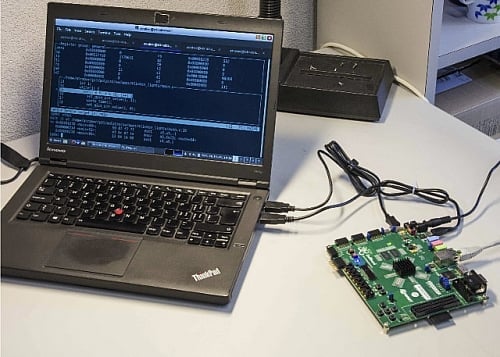

PULPino se dá implementovat v FPGA desce ZedBoard

Zajímavé je, že podle EE Times se

autorům podařil tape-out také většího procesoru PULP, a to

údajně už loni v listopadu (o čemž zřejmě informace

zapadly). V tomto případě už se jednalo o 28nm proces

a výrobním partnerem jsou GlobalFoundries. V obou

případech jde o univerzitní projekty, takže případné

uchycení těchto čipů v praxi je nejistá věc. Pro

architekturu RISC-V by však tyto pokusy mohly vydláždit cestu

a zároveň praktickým ověřením přispět k jejímu

rozvoji.

Zdroje: ETHZ (1,

2), EE

Times, CNX

Software