V současnosti je serverovým esem Oraclu procesor Sparc T4. Jde o osmijádrový čip vyráběný na 40nm linkách u TSMC a taktovaný až na 3 GHz. Na Hot Chips 2012 se Oracle pochlubil následníkem, nazvaným prostě Sparc T5. Novinka se přesune na 28nm proces (taktéž u TSMC) a Oracle ji tedy může vybavit o poznání silnější výpočetní výzbrojí. Monolitický čip bude obsahovat hned 16 jader, jejichž architektura je převzata z čipu T4. Údajně se ale také zvedne frekvence čipů, a to na 3,6 GHz (zrychlení o 20%). Nový Sparc by tedy měl být o poznání výkonnějším procesorem.

Jádro procesorů Sparc T4 a T5 je navrženo na zpracovávání dvou instrukcí za takt. SPARC je sice původně architektura typu RISC, dnešní zástupci však používají technologii provádění instrukcí „out-of-order“. Ve výsledku se až tak radikálně neliší od moderních procesorů architektury x86. Pipeline má 16 stupňů (tedy alespoň co se týče celočíselné části). Jádro disponuje poměrně rozsáhlým arzenálem jednotek akcelerujících šifrovací a hashovací algoritmy. Podporováno je leccos: šifrování přes RSA, D-H, DSA, ECC, AES, DES, Tripple DES či algoritmy Camellia a Kasumi, a hashování metodami CRC32, MD5, SHA-1, SHA-224, SHA-256, SHA-384 a SHA-512. Tyto úlohy tak nebudou užírat procesorový výkon a zřejmě také spotřebují méně energie.

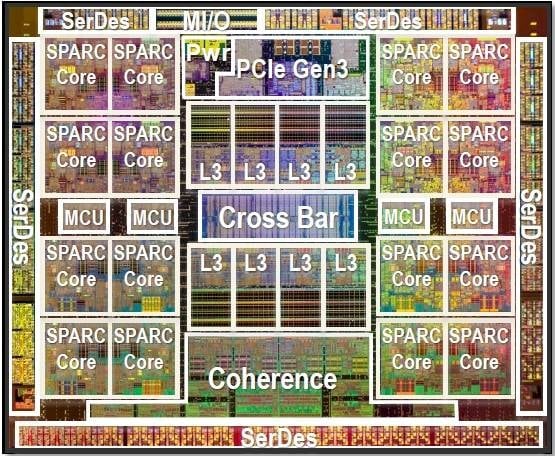

Mimochodem, každé z jader zpracovává zároveň 8 vláken, takže jeden Sparc T5 jich najednou obslouží 128. Šestnácka jader sdílí L3 cache o poměrně malé velikosti 8 MB. L1 a L2 jsou již vyhrazené pro každé jádro. L2 cache má 128 KB a datová a instrukční L1 cache pak po 16 KB. Paměťový řadič je dvoukanálový (údajně podporuje rychlosti do 1066 MHz) a vedle něj je procesor vybaven také dvěma rozhraními PCI Express ×8 standardu 3.0. To vše (a navíc propojovací logika pro vícesocketové systémy) komunikuje crossbarem o přenosové kapacitě až 1 TB/s.

Zmíněná propojovací logika byla u čipu T5 posílena. Zatímco Sparc T4 dokázal škálovat na čtyři sockety, novinka si poradí i s osmi, přičemž každý z procesorů bude mít přímý kontakt se všemi svými sedmi bratříčky. To má údajně osmiprocesorovým serverům přinést prakticky lineární růst výkonu ve srovnání s čtyřprocesorovou konfigurací. Na druhou stranu postrádá 28nm Sparc integrované řadiče sítě Ethernet (T4 měl na čipu dvě 10Gb síťová rozhraní).

Čipy jsou samozřejmě určeny pouze pro servery, a to ještě pro exempláře s značně drastickými cenovkami. Oracle má celkem pochopitelně zájem hlavně o lukrativní oblast nejkritičtějších serverů pro nejmovitější zákazníky. Speciální procesory půjdou ruku v ruce se speciálními podporou ze strany operačního systému Solaris a zejména databázového softwaru z produkce Oraclu.

Zdroj: The Register