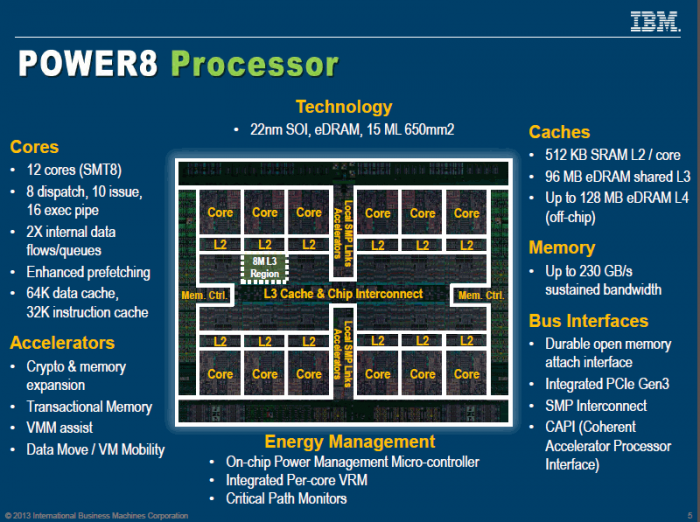

Minulý rok IBM na stejné akci přednášelo o procesorech Power7+, což bylo osmijádro vyráběné na 32nm procesu, které samo bylo následníkem 45nm architektury Power7. Novinka jménem Power8 bude opět velikým čipem pro highendové servery třídy enterprise: procesor má dvanáct jader a velké množství paměti cache. To vše je umožněno zejména přechodem na nový výrobní proces – Power8 se bude vyrábět na 22nm linkách IBM s použitím technologie SOI. Neznáme přesný počet tranzistorů v čipu, ale s výměrou 650 mm² půjde o slušného macka, a to i proti dosti rozměrnému Power7+ (567 mm²).

Procesor IBM Power8 pro highendové servery

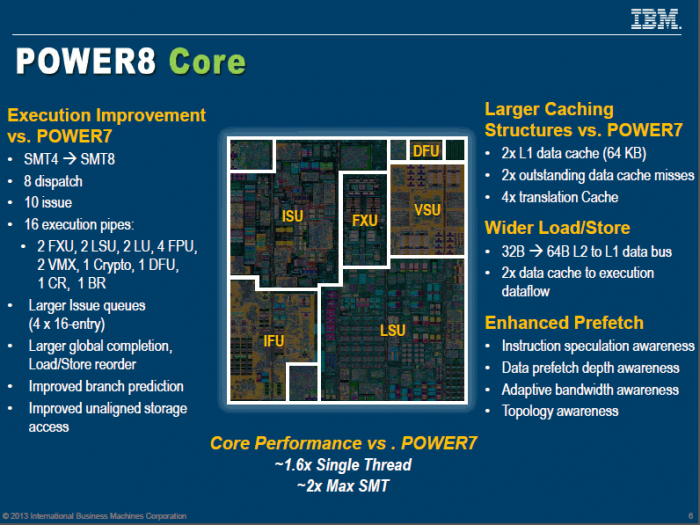

U architektury Power IBM hodně dbá na robustní systém mezipamětí, zejména s masivní L3 cache typu eDRAM. Také procesorová jádra jsou však značně silná, co se týče dostupných prostředků. V jednom se nachází rovnou šestnáct výpočetních jednotek: dvě logické jednotky, dvě aritmetické, čtyři FPU, dvě jednotky pro čtení a zápis do paměti, po jedné pro vykonávání podmínek a větvení a dvě vektorové jednotky.

Přítomen je i specializovaný blok pro kryptografii a FPU pro výpočty v desítkové soustavě, což je schopnost ve světě počítačů poměrně neobvyklá, IBM s ní ale boduje u klientů z finančního sektoru. Jádro by mělo být schopno zpracovávat osm instrukcí za takt, v jednom taktu jich může špičkově mezi jednotky rozdělit až deset. Dalších specializovaných akcelerátorů má mimochodem čip více, například i pro práci s transakční pamětí.

Procesor IBM Power8 pro highendové servery

IBM již u procesorových jader delší dobu používá obdobu technologie HT u Intelu, například u architektury Power7+ jedno jádro zpracovávalo čtyři vlákna naráz. U Power8+ je tento aspekt ještě posílen a každé z dvanácti jader nyní vykonává hned osm threadů. Osm vláken naráz prohání jádry také konkurenční Sparc T5 od Oraclu, IBM však vedle masivního paralelismu dbá také na výkon v jednom vlákně, který může technologie SMT negativně ovlivnit. Procesor by údajně sám měl detekovat, že po něm úloha požaduje vysoký výkon na vlákno, a snížit počet najednou zpracovávaných vláken (na čtyři nebo dvě), či jádro zcela vyhradit jednomu vláknu. Takové fungování však asi bude vyžadovat spolupráci od plánovače v operačním systému – což by ale IBM mělo u používaného Linuxu a systému AIX zajistit.

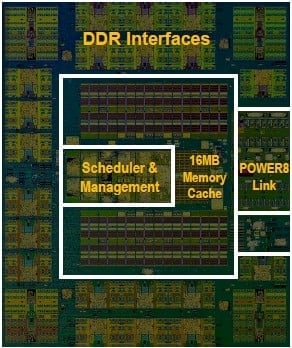

Procesor IBM Power8, snímek čipu

Každé jádro má nyní 64 KB L1 cache pro data (dvojnásobek oproti Power7+, zřejmě kvůli tomu, že čip nyní zpracovává osm vláken místo čtyř), instrukční cache zůstala na 32 KB. Sběrnice mezi L1 a L2 cache byly posíleny, nyní přenášejí 64 bytů místo 32. Vylepšení doznala přesnost predikce větvení, posíleno bylo přednačítání dat z paměti či zpracování výpadků dat v L1. L2 cache typu SRAM má velikost 512 KB na jádro, L3 cache je (u IBM již tradičně) typu eDRAM, díky čemuž má docela štědrou velikost 8 MB na jádro, celkově tedy 96 MB. Navíc bude mít procesor k ruce nově i externí L4 cache o velikosti až 128 MB.

Dle IBM by měl jednovláknový výkon jádra na stejném taktu vzrůst zhruba o 60 % oproti architektuře Power7, přičemž čipy se budou vyrábět se zhruba stejnou frekvencí – mají běžet na 4 GHz, tedy alespoň dle plánu. Celkový výkon, tedy při vytížení celého CPU vhodnými vícevláknovými úlohami, by měl dosahovat až dvouapůlnásobku toho, co dokáže Power7+.

Procesor IBM Power8 pro highendové servery

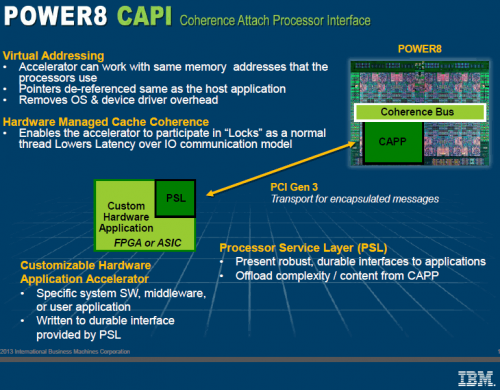

Vedle samotné výpočetní části CPU proběhnou změny také na ostatní infrastruktuře čipu, a jde o změny poměrně zásadní. Power8 bude mít integrován řadič PCI Express 3.0 (přenosová rychlost 48 GB/s, čili zřejmě 48 linek) a jak již bylo řečeno, také externí vyrovnávací paměť čtvrté úrovně. Její řešení je skutečně zajímavé a souvisí s paměťovým řadičem. Power8 přichází v době, kdy se čeká přechod na paměti DDR4, ty ale ještě nejsou přesvědčivě na trhu. Samotné CPU proto nemá podporu pro DDR3, ani DDR4 a místo toho používá jen obecné vysokorychlostní rozhraní, kterým komunikuje se speciálními externími čipy, které teprve implementují paměťový řadič, zatím pro paměti typu DDR3. Tyto čipy, označované „Centaur“ ale zároveň obsahují paměť tvořící L4.

IBM Power8 - přídavný čip Centaur s paměťovým řadičem a blokem L4 cache

Jeden Centaur obsahuje 16 MB paměti a jednokanálový řadič DDR3; k procesoru Power8 jich lze připojit až osm pomocí (ve formě paměťových „karet“, osazených 32, 34 nebo 128 GB RAM). Plně vyzbrojené CPU tedy má k dispozici celkem 128 MB L4 cache a osmikanálový paměťový řadič, s kterým má dosahovat propustnosti 230 GB/s. Centaur ale díky přítomnosti L4 cache zároveň funguje jako paměťový buffer. Výhodou řešení je i to, že paměť bude možno upgradovat na DDR4 výměnou příslušných modulů. Při použití 32GB modulů (tedy osmi 128GB paměťových karet) lze nainstalovat 1 TB paměti pro každý procesorový socket serveru.

Procesor IBM Power8 pro highendové servery

Procesory Power8 se mají objevit v plné šíři serverů, které má IBM v sortimentu; čipy budou mít pro různá určení také různé fyzické provedení. Cena serverů osazených těmito – troufám si říci – nekompromisními kusy hardwaru bude pochopitelně převysoká, IBM se s procesory Power orientuje jen na ty nejlukrativnější části serverového trhu (jinak by si ani takto masivní a na výrobu náročná CPU dovolit nemohlo). Podle představitelů společnosti by procesory Power8 měly být uvedeny přibližně v polovině příštího roku.

V tuto chvíli již má IBM údajně v rukou vzorky, běžící v laboratořích a jeden (otázka je samozřejmě, zda funkční) byl na Hot Chips 2013 i fyzicky k vidění. Zároveň prý IBM také pracuje na příští generaci, označené prostě Power9 – což však asi nepřekvapí, jelikož vývoj každého CPU trvá mnohem déle, než nějaké dva roky, které mezi jednotlivými generacemi uplynou.

Zdroje: The Register, WCCFtech