64vrstvá 3D NAND typu TLC je v masové výrobě

O startu výroby informuje tchajwanský web DigiTimes, ale už zdá se přišlo i oficiální potvrzení firmy. Firma rozjela masovou výrobu 256Gb 64vrstvých čipů 3D NAND se záznamem TLC, tedy pamětí, které by se měly dát široce použít ve spotřebitelských i dalších výrobcích od mobilů po karty, klíčenky a SSD pro počítače. YMTC údajně chystá vlastní UFS úložiště pro mobily i vlastní SSD, ale paměť by asi mohla být i ve výrobcích dalších firem.

YMTC by údajně během příštího roku mělo dosáhnout ve svých současných provozech ve Wu-chan měsíční objem výroby ve výšce asi 100 až 150 tisíc 300mm waferů s čipy NAND. Státní holding Tsinghua Unigroup, který YMTC vlastní, ale v Čcheng-tu (angl. transkripce Chengdu) staví další 300mm linku, která má přidat dalších asi 100 000 waferů měsíčně, snad s možností dalšího rozšiřování. Tato továrna má najet do výroby v letech 2021 nebo 2022. I s ní bude YMTC menším výrobcem proti Samsungu, Micronu a Toshibě, ale asi se dá čekat, že pokud bude jeho NAND komerčně úspěšná, bude vláda komunistické Číny podnik podporovat a tím pádem může jeho pozice časem posilovat. Další kapacita je prý plánována také v Nan-ťingu (Nankingu).

Také technologie se samozřejmě bude vyvíjet, příští generace pamětí má například už mít 96 vrstev. To už nyní Toshiba, Samsung nebo Hynix mají na trhu a nastupuje další generace (u Samsungu nedávno 136 vrstev), takže lze říct, že zde je Čína o pár let opožděná.

Unikátní technické řešení Xtacking

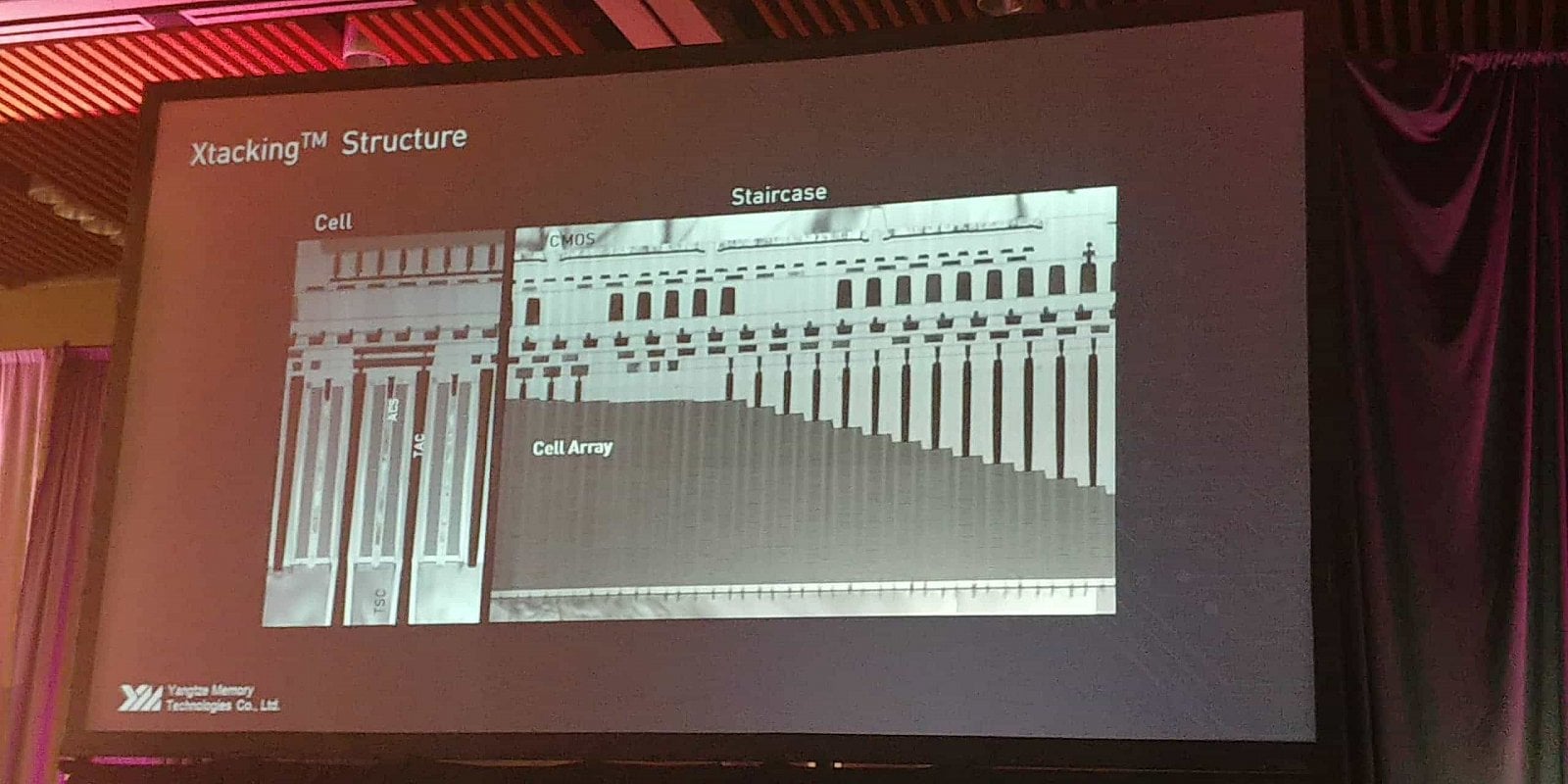

Zajímavé je výjimečné řešení oné 64vrstvé 3D NAND od YMTC. Týká se to logické části čipů, která se stará o čtení a zápis do buněk, komunikaci s řadičem a další věci. Zatímco samotné buňky se dnes zmnožují pomocí přidávání dalších a dalších vrstev, tato logická část zůstává klasicky v rovině a tímto způsobem neškáluje. Vyvstává tím problém, kdy tato infrastruktura může procentuálně zabírat čím dál víc místa na čipu. Firmy tento problém výhledově chtějí řešit přesunutím logiky pod buňky NAND (tzv. periphery under cell, například Hynix to označuje jako 4D NAND, Toshiba/WD zase jako CoA, čili Circuit under Array).

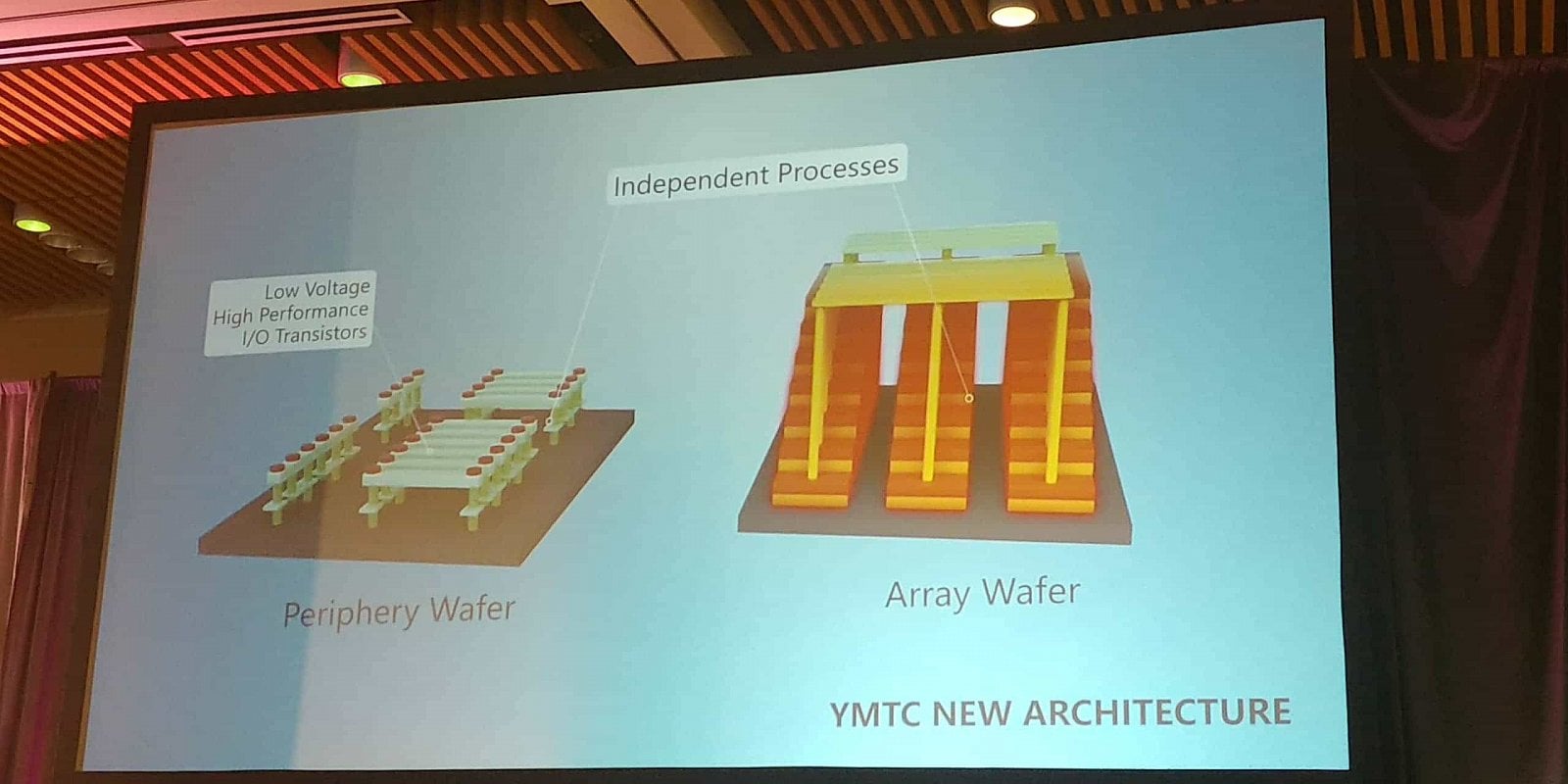

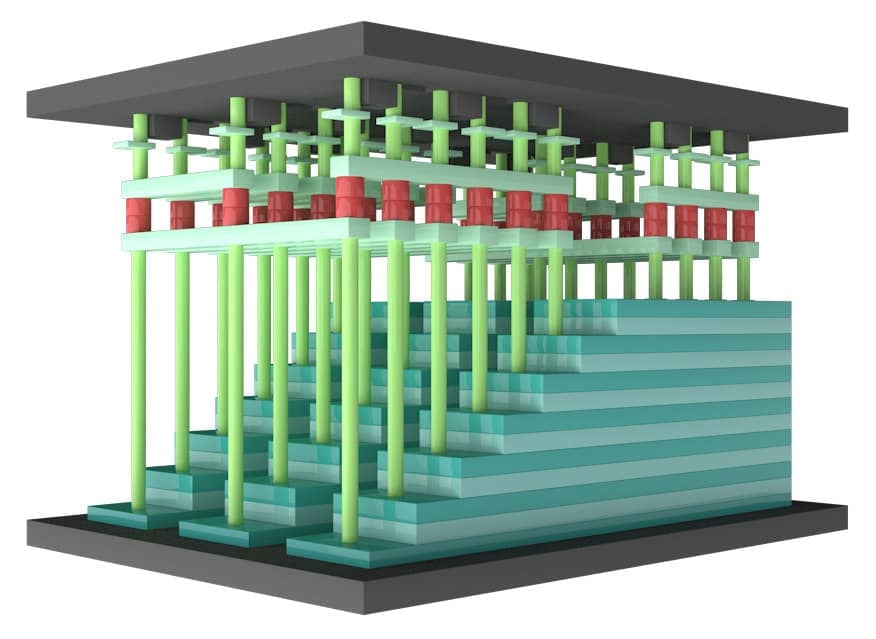

YMTC už zřejmě princip periférie pod buňkami používá, ale s tou obměnou, že logické obvody vyrábí zvlášť a poté tuto vrstvu pájí dohromady s čipem s vrstvami buněk (podle schémat ale ne pod něj, ale naopak nad něj). Výslední čip NAND je tak vlastně 3D čipletové řešení, které firma pojmenovala Xtacking. Při výrobě výsledku se tak kombinují dva různé wafery, a je nutné logickou a NAND vrstvu spojit kovovými kontakty. Toto by mělo zvyšovat výrobní náklady, takže jde o jistou nevýhodu. YMTC tvrdí, že Xtacking není příliš drahý, ale nic přesného neuvádí.

3D NAND YMTC a technologie Xtacking: ve výsledném výrobku je čip s logikou kontakty připájen na vrch čipu s vrstvami buněk NAND

3D NAND YMTC a technologie Xtacking: ve výsledném výrobku je čip s logikou kontakty připájen na vrch čipu s vrstvami buněk NANDOptimální proces pro obě části

Ovšem na oplátku může YMTC použít pro logiku a pro paměťové buňky různý proces, zatímco tradiční postup, kdy se vše vyrábí spolu, vyžaduje, aby se logika vyrobila na stejné technologii jako buňky. To však znamená, že pro logiku je proces neoptimální. Při přechodu z planární na vrstvenou NAND se totiž „velikost“ procesu vrátila z 15 nm na nějakých 30–40 nm (toto číslo se běžně neuvádí, takže přesný údaj pro současnou 3D NAND nemáme). Přístup YMTC ale dovoluje použít pro logickou vrstvu modernější proces, díky čemuž může dosahovat vyšší výkon. Je také možné, že tento postup usnadnil vývoj a implementaci a byl zvolen kvůli tomu, zatímco lepší výkon je spíše vedlejší efekt.

http://www.ymtc.com/Uploads/video/Xtacking.mp4

Zda se tento přístup vyplatí přes patrně vyšší výrobní cenu, to se teprve ukáže. Ale je zajímavé, že YMTC jde stejnou cestou, jako Intel (s procesory Lakefield a technologií heterogenních čipletů Foveros) a AMD (Ryzen 3000, Epyc 7002), tedy používání více různých procesů pro různé části čipu podle toho, která technologie je pro dané bloky optimální. Moderní výrobní procesy budou zdá se stále větší výzvou, a tak se tyto přístupy asi budou objevovat čím dál víc a hybridní kombinované vícečipy asi budeme vídat stále častěji.