Včera jsme tu měli zprávu o prosáknutí některých informací o serverových procesorech AMD s architekturou Zen 4, které také budou už vyráběné na 5nm procesu. Dostanou nový socket, 12kanálové paměti DDR5 a 96 jader, které budou v 12 čipletech. Krátce poté přicházejí další dokreslující informace k Zenu 4. Například příjemná věc, že AMD údajně konečně přidá podporu 512bitových SIMD instrukcí AVX-512.

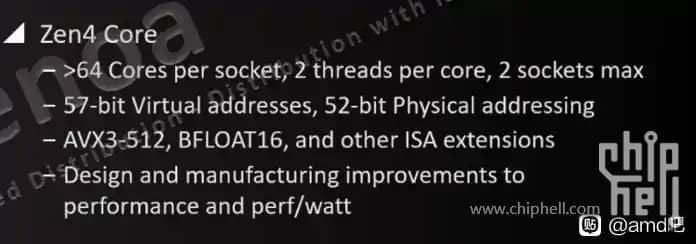

Tato informace se objevila na fóru Chiphell a je doložena výřezem z dokumentu, který má být slajdem od AMD – samozřejmě nemůžeme vědět jistě, že je to není „fake“. Informace o tom, že Zen 4 podporuje AVX-512, ale je prý pravdivá podle předchozího leakera ExecutableFix, což by mohlo podporovat i pravost ostatních informací na tomto útržku.

Co tam tedy je dále? Potvrzeno je „víc než 64“ jader, ale ne přímo číslo 96. Současně je zde jasně uvedeno, že jádro Zen 4 má pořád jenom dvě vlákna na jedno jádra (tedy SMT je jenom dvoucestné jako dosud). Také je řečeno, že procesory Epyc této čtvrté generace budou pořád podporovat maximálně jen dvousocketové (2S) servery a desky.

AMD na údajném slajdu uvádí, že jsou podporovány instrukce „AVX3-512“ (AVX3 bylo dříve se objevující předběžné označení pro AVX-512). Není řečeno, jaké subsety AVX-512 bude Zen 4 podporovat, což je dost důležité, ale aspoň se základy by tedy asi měl být kompatibilní. Zen 4 by tedy mohl dorovnat tuto dílčí výhodu, kterou má Intel od vydání architektury Skylake-X/Skylake-SP. Ovšem také nemusel. Bude záviset na tom, s jakým výkonem bude výpočet probíhat. Pokud by například byly pořád použité 256bitové jednotky SIMD a 512bitové operace probíhaly ve dvou průchodech, nemusí se výkon proti AVX/AVX2 téměř vůbec zlepšit a podpora by pak měla hlavně cenu kompatibility.

Kromě AVX-512 bude jádro také podporovat výpočty s hodnotami BFloat16, což je 16bitový formát čísel uzpůsobený pro trénování neuronových sítí. Obsažené ale mají být i další instrukční rozšíření. Není řečeno jaká, takže nemáme žádnou představu, zda se pod tímto skrývají jen drobnosti nebo něco významnějšího.

Zen 4 má podle těchto informací mít vylepšený výkon a energetickou efektivitu – a to jak samotným architektonickým návrhem, tak 5nm výrobním procesem. Ale nic jiného se asi ani nečekalo. Také je uvedeno, že CPU bude podporovat 52bitové fyzické adresování RAM zatímco virtuální adresy budou podporované 57bitové.

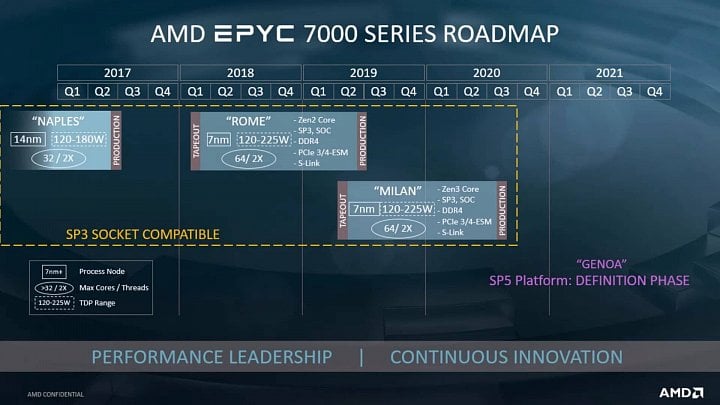

Velikosti čipletů: lepší proces pro IO křemík?

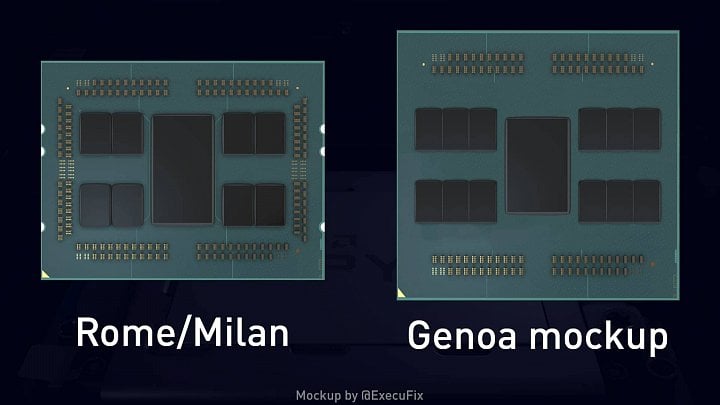

Kromě informací o nových instrukcí je tu také ještě něco k fyzické podobě procesoru. Včera jsme ukazovali „koncept“ toho, jak by měl procesor podle leakera vypadat. ExecutableFix pak potvrdil že ač jde o nepravou podobu (ručně „naphotoshopovanou“ z obrázku procesoru Epyc druhé generace), polohy a velikosti čipů na ní sedí s tím, jak vypadá reálné schéma.

Takto nějak by měl procesor Genoa vypadat. Jde jen o montáž ne reálnou podobu (Zdroj: ExecutableFix)

Takto nějak by měl procesor Genoa vypadat. Jde jen o montáž ne reálnou podobu (Zdroj: ExecutableFix)Současně s tím také zveřejnil reálné velikosti čipletů, z kterých vyplývá, že IO čiplet zřejmě dostane novější výrobní technologii, což by mohlo zlepšit efektivitu. U 7nm procesorů Epyc (Rome i Milan) má IO čiplet nějakých 416 mm²; u Epycu Genoa bude menší s 396,64 mm². Není to o moc – podle obrázku to vypadalo na větší rozdíl – ale procesor bude mít místo PCIe 4.0 už konektivitu PCIe 5.0, bude podporovat komunikaci s o 50 % vyšším počtem CPU čipletů a také o 50 % víc kanálů paměťového řadiče, navíc s podporou DDR5. Pravděpodobně je proto použitý lepší výrobní proces s vyšší hustotou a snad také lepší energetickou efektivitou.

U 5nm CPU čipletů lepší proces je už jasný, ale jak jsme zmínili minule, kvůli udržení počtu jader na osmi jsme měli trošku strach o jejich velikost. Při malé ploše by se totiž procesory s jedním nebo dvěma čiplety (tedy Ryzeny pro desktop) špatně chladily. Velikost těchto 5nm křemíků je nakonec skutečně menší, mají jen 72,225 mm². Není to ale už o moc méně, než měly 7nm čiplety s jádry Zen 2, pro ty se uvádí 74 mm². Snad se tedy teploty těchto procesorů nezhorší o moc.

Jinak je pravděpodobné, že stejný výrobní proces, jako bude použitý u IO čipletu Epycu Genoa, bude také využitý v IO čipletu procesorů Raphael pro desktopový socket AM5. A to kvůli ušetření nákladů na vývoj dvou těchto čipů.

Galerie: Uniklé či zveřejněné dokumenty k architektuře AMD Zen 4

Zdroje: Chiphell, ExecutableFix (1, 2), VideoCardz