Procesory IBM Power jdou se svou vlastní instrukční sadou už dlouho mimo svět PC (počítejme v to i původní Power počítače Apple). Ovšem tato linie z doby původních architektur RISC se pořád má k životu. A v poslední době nachází nové příznivce mezi běžnými uživateli díky tomu, že jde o poměrně otevřenou platformu – pracovní stanice Talos II a Blackbird mají většinou firmwaru svých komponent open source.

IBM teď současné Power9 navazuje novou generací. Představilo na konferenci HotChips 32 nové procesory Power10, které přinese výrazně výkonnější jádra a současně také výrazně lepší energetickou efektivitu, protože tyto čipy jsou už vyráběné na 7nm EUV procesu u Samsungu. Power10 vypadá hodně zajímavě, nicméně na trh přijde až příští rok.

Power10: nejnovější generace big iron architektury IBM na 7 nm

Procesor Power10 je 7nm čip s 18 miliardami tranzistorů a plochou 602 mm², což je plocha highendového GPU adekvátní velmi výkonnému serverovému CPU. IBM u něj použilo 18 vrstev kovových spojů, nicméně hustota je poměrně nízká (zvlášť na EUV proces). To je ale asi proto, že IBM cíleně nejde za vysokou hustotou a snaží se dosáhnout vysoké frekvence.

Procesor bude mít nezvyklý počet jader, a to patnáct. Je to ovšem proto, že IBM bude jedno jádro v návrhu vždy vypínat – díky tomu bude moci i defektní čipy používat do nejvyšší konfigurace produktu. Podobně se to dělá u herních konzolí, které fyzicky mají GPU jednotky navíc do rezervy a žádný čip nevyužívá všechny. Ve skutečnosti je tedy na čipu klasicky šestnáct jader.

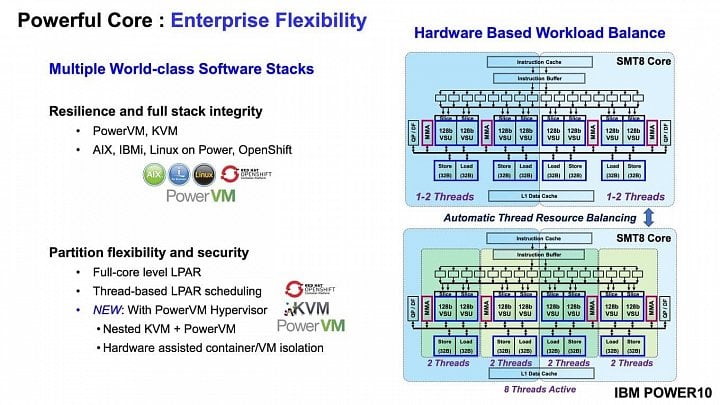

15/16 jader je počet pro konfiguraci procesoru s SMT8, tedy SMT, kdy každé jádro zpracovává 8 vláken naráz. IBM bude prodávat i verzi s SMT4 (jen čtyřmi vlákny na jádro), která bude mít jader dvojnásobek, tedy 30 (fyzicky 32). Toto vyplývá ze zvláštní architektury, která byla použitá už v Power9 a kdy se SMT8 jádro skládá ze dvou identických symetrických „slice“, které samostatně mohou fungovat jako SMT4 jádro.

Spřažením dvou těchto jader vzniká jednotka, která se pro software tváří jako jedno jádro (ale dvoujádrová interní povaha bude mít asi dopad na běh kódu). Tato zvláštní architektura má zřejmě za cíl jednu věc: snížení licenčních poplatků u softwaru s cenami stanovenými podle počtu jader.

Jednočipové a dvojčipové procesory, takt přes 4 GHz

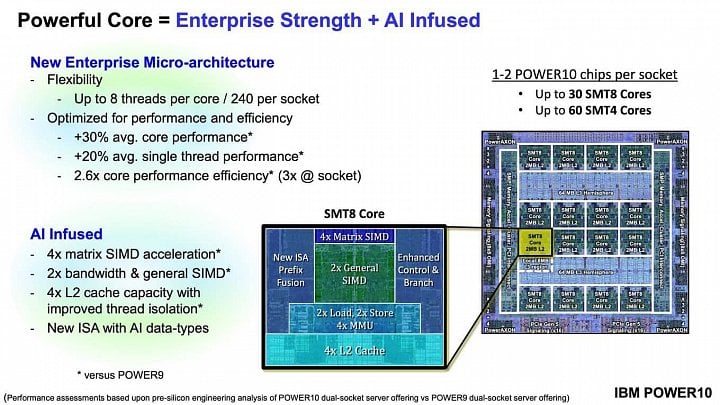

Na tomto základu IBM plánuje dvě verze procesoru – jednočipovou a dvojčipovou (firma mimochodem procesory skládala z více čipů už kdysi dávno, není to tedy nějaká inspirace Epycem). Jednočipový model bude obsahovat maximálně 15 jader SMT8/120 vláken (nebo 30 SMT4 samozřejmě…) na frekvencích přes 4 GHz – finální zatím nebyly sděleny. Tento typ je zamířen na maximální jednovláknový výkon.

Dvojčipový model bude mít maximálně 30 SMT8 jader, tedy celkem 240 vláken. Takty u něj bude nižší, IBM uvádí 3,5 GHz a víc. Tuto variantu IBM míří na „throughput“ úlohy potřebující co nejvyšší vícevláknový výkon. Obě verze budou mít stejnou konektivitu co do řadiče pamětí, ale dvojčipový model bude poskytovat dvakrát tolik linek PCI Express (celkem 64). Na druhou stranu má tato dvojčipová verze omezené škálování, maximálně bude podporovat 4S servery. Pro maximální velikost systému tedy bude nutno využít 16S zapojení jednočipových 15jader.

Architektura jádra: výrazně širší s vyšším IPC

Jádro Power10 je proti architektuře Power9 výrazně přepracováno. Podle předběžných projekcí je průměrný výkon na jedno jádro lepší o 30 % a jednovláknový výkon stoupnul až o 20 %. Pokud se porovnávají jen procesory, je údajně poměr výkonu a spotřeby až 3,0× lepší (bohužel neznáme TDP, ale je možné, že tu IBM srovnává výkon 30jádrového dvojčipového Power10 s 12jádrovým Power9).

Na úrovni celého serveru je podle IBM energetická efektivita 2,6× lepší – výkon připadající na jedno jádro je vyšší o 30 % (1,3×), ale spotřeba na jedno jádro vychází poloviční (0,5×), což poděleno dává 2,6× zlepšení. Ovšem pozor, toto jsou plánované hodnoty či projekce, nikoliv přímo výsledky naměřené u finálního křemíku.

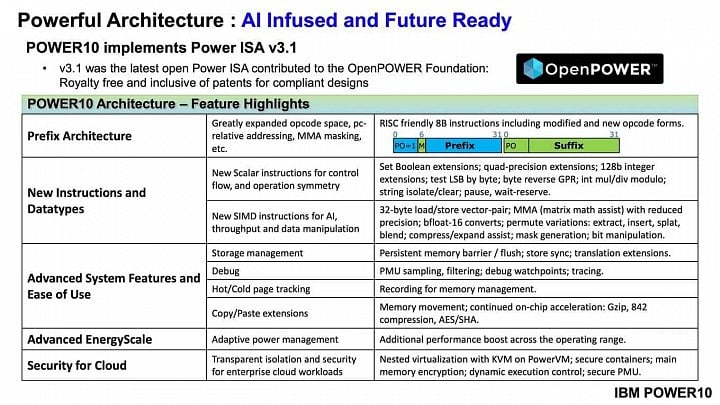

Jak už bylo řečeno, SMT8 jádro se skládá ze dvou polovin (které jsou vlastně jádry SMT4). U procesoru Power9 měla každá polovina dvě 128bitové výpočetní pipeline VSU (ty se ještě samy skládaly ze dvou 64bitových). U Power10 v podstatě IBM rozšířilo toto modulární uspořádání na dvojnásobek, v jedné polovině SMT8 jádra (= SMT4 jádru) je čtveřice 128bitových pipeline. Zdvojnásoba byla také propustnost do L1 cache pro data (2×32 bajtů za cyklus) a do L2 cache (čtení 64 bajtů za cyklus, zápis 32 bajtů za cyklus).

IBM dále posílilo prefetch, prediktory větvení a prohloubilo většinu z různých front/bufferů out-of-order vykonávání. Kapacita TLB bufferu byla zečtyřnásobena na 4K položek a L2 cache je také čtyřnásobná – 2MB na jedno SMT8 jádro (nebo pro dvě SMT4 jádra). L1 instrukční cache je o 50 % větší, má 48 KB místo 32 KB u Power9.

Tip: IBM Power9 detailně. 14nm vyzyvatel Intelu má dvě velikosti jader s SMT4/8

Mimochodem, jádro má snížené latence – u L2 cache z 15,5 na 13,5 cyklu, u L3 cache z 35,5 na 27,5 cyklů. L1 cache pro data má beze změny latenci 4 cykly, ale při store forwardingu dříve měla penalizaci další dva cykly, což teď už není. Přístup do TLB má latenci 8,5 cyklu (dříve 15,5).

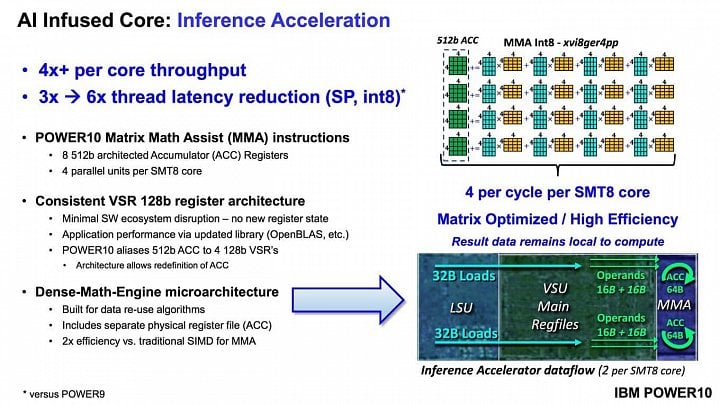

Speciální akcelerátory pro AI

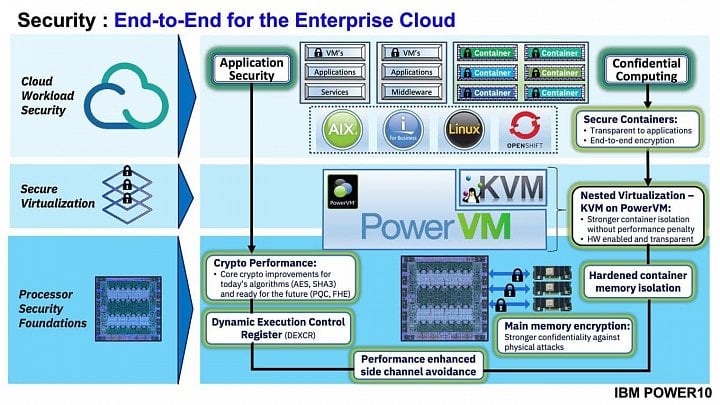

Další velkou změnou jádra je, že IBM v souladu s aktuálními trendy integrovalo akceleraci umělé inteligence (neuronových sítí s jejich maticovými operacemi). Tyto operace používají šířku vektoru 512 bitů (tedy jako AVX-512) a běží ve speciálním akcelerátoru MMA, ne tedy na standardních vektorových ALU.

Ty používají pořád stejné 128bitové SIMD, tedy vektory šířkou odpovídající SSEx u procesorů x86. Ovšem jejich výkon je také u Power10 zdvojnásoben díky zmíněnému zdvojnásobení počtu výpočetních pipeline VSU.

Řada změn byla v jádře učiněna pro vylepšení energetické efektivity, jádro používá vylepšený clock-gating pro odpojení nepoužívaných jendotek, fúzi instrukcí (opů) v pipeline a další optimalizace.

Paměťový subsystém a I/O: Open Memory

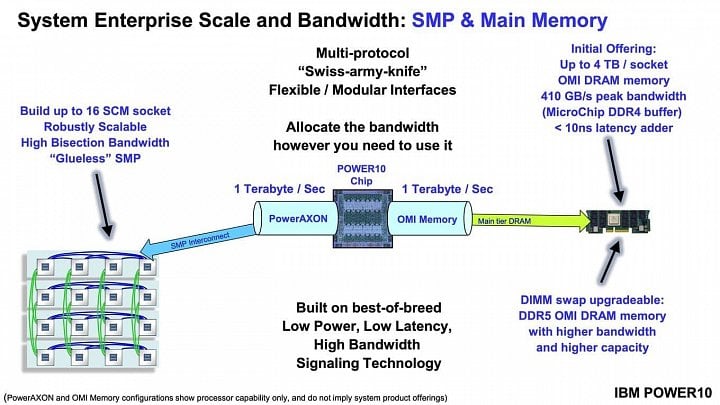

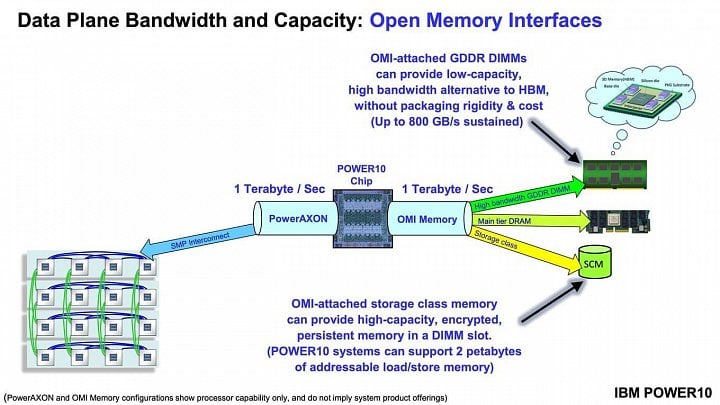

Procesor bude obsahovat až 120 MB L3 cache. Práce s operační pamětí bude docela specifická. IBM použije systém bufferových čipů, kterému říká Open Memory. Jde o šestnáctikanálové rozhraní s celkově až 1TB/s propustností, které je obecné a nepracuje s konkrétním paměťovým standardem. Až na toto rozhraní se napojí řadič zprostředkovávající kompatibilitu s reálnou pamětí. Výměnou těchto bufferových čipů se tedy dá upgradovat paměť třeba z DDR4 na DDR5 nebo na nevolatilní paměti. Dokonce má být možné použít paměť typu GDDR pro maximální propustnost (údajně až 800 GB/s, což je na CPU brutální číslo).

Je to asi podobné dřívější architektuře s tzv. čipy Centaur, ale asi se počítá s tím, že zprostředkovací čipy s řadiči může vyrábět i externí firma, takže je ekosystém Power10 otevřený pro nově příchozí. Nevýhoda je samozřejmě vyšší cena a horší latence (postih je ale podle IBM prý méně než 10 ns).

V systémech IBM to bude řešeno tak, že čip komunikující s rozhraním Open Memory bude osazen na paměťových modulech, které budou mít speciální konektor a provedení. Do jejich slotu proto bude možné nainstalovat i nové paměti s čipy DDR5, stačí, když budou mít na sobě patřičný nový řadič. Nevýhoda je jasná – tyto moduly bude nejspíš vyrábět jen IBM a nechá si je patřičně zaplatit, nebudete moci pořídit běžné moduly DIMM („otevřená paměť“ tak současně znamená proprietární paměť).

Zda IBM uvede levnější verzi Power10, která bude mít místo Open Memory přímo integrované řadiče DDR4 nebo DDR5, aby desky (a paměti) nebyly tak drahé, zatím nevíme. U Power9 to firma učinila a tato verze šla dokonce na trh jako první, uvidíme, zda IBM takové CPU vydá i teď na 7 nm. Pokud ne, byl by to trošku problém pro použití Power10 v pracovních stanicích a PC mimo drahé enterprise servery.

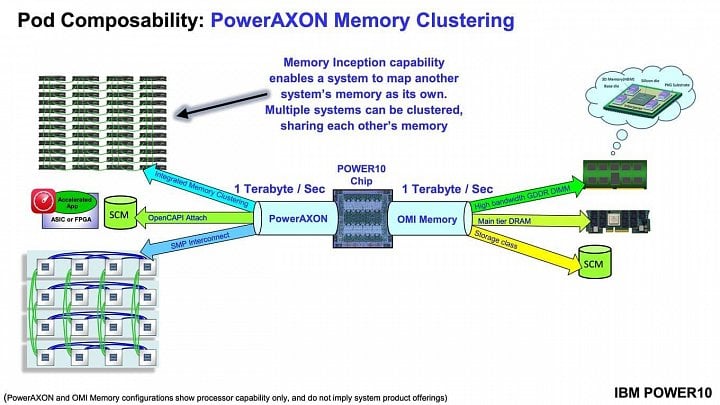

PowerAXON, PCI Express 5.0

Power10 má i velmi silné I/O. Integrovaný řadič PCI Expressu už bude umět PCI Express 5.0 a poskytuje 32 linek. Současně má procesor další konektivitu označenou jako PowerAXON. Tato PHY mají celkově propustnost 1 TB/s a dají se použít na různé věci – například pro periférie s koherentním připojením OpenCAPI, pro různé akcelerátory, dokonce i pro připojení další paměti.

Současně je tato konektivita použitá i pro komunikaci mezi CPU ve víceprocesorových systémech. Power10 podporuje až šestnáctiprocesorové (16S) servery.

Až 2PB RAM plně sdílená mezi servery

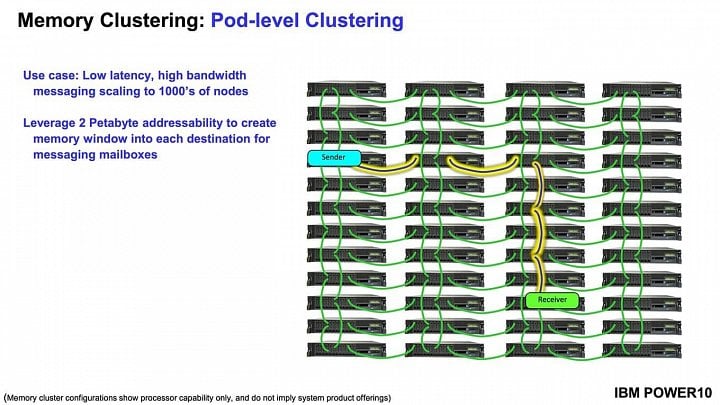

Konektivita PowerAxon má mít ještě jednu specialitu. Umožňuje budovat klastry serverů se sdílenou pamětí – procesorová jádra přes ni může na hardwarové úrovni normálně číst a zapisovat do paměti jiného serveru připojeného touto konektivitou. Latence je prý jen o 150 ns horší než při přístupu do RAM jiného CPU ve stejném serveru.

Takový klastr pak může sdílet obrovské množství RAM, která se logicky chová jako jediný unifikovaný prostor – maximální kapacita je až 2 PB, uzlů v takovém klastru může prý být v řádu tisíců.

Reálná dostupnost příští rok

Nynější prezentace na HotChips je pro procesory Power10 zatím poměrně předběžná, je ještě relativně hodně času do vydání. Podle IBM budou „systémy“ (tedy celé servery) k dodání do 12 měsíců, takže vypuštění by mohlo být dejme tomu někde v polovině roku 2021 nebo v Q2 2021. V tuto chvíli je zatím po tapeoutu procesoru v Samsungu, funkční křemík už údajně běží v laboratořích. Vydání produktů bývá typicky okolo roku po tapeoutu, což zhruba sedí.

Galerie: Odhalení procesorů IBM Power10, prezentace na HotChips 32

Open source pracovní stanice Talos s Power10 nejdřív v roce 2022

Pokud sledujete platformu Power kvůli jejím open source kvalitám, bude vás asi zajímat, zda firma Raptor Engineering chystá nové počítače s těmito procesory. Zde je asi odpověď ano, ale jejich příchod je dost vzdálený. Podle představitelů firmy údajně bude trvat delší dobu, než firma připraví nové desky pro Power10.

Tip: Talos II odhalen. Počítač s procesorem IBM Power9 můžete mít za něco přes 2000 dolarů

Je implikováno, že dosažení podobného standardu otevřenosti jako je nyní u Talosů s Power9, bude u Power10 těžší, ale nejspíš půjde i o čas potřebný na vyvinutí hardwaru (a je možné, že Raptor bude čekat na později vydané „scale-out“ modely procesorů bez bufferové paměti). Každopádně stanice a desky pro procesory Power10 má Raptor Engineering vydat až nejdřív v roce 2022.

Zdroje: IBM, HardwareLuxx, AnandTech, Phoronix