Před časem Intel přišel s patchi pro Linux, které odhalily budoucí plán: firma chystá systém, jaký má u enterprise serverů například IBM. Tedy možnost, že vám bude prodán křemík s různými vlastnostmi a funkcemi, které jsou v základním produktu vypnuté, ale pokud zaplatíte poplatek navíc, mohou být na dálku zapnuté. Vypadá to, že první případ, kdy se takto budou softwarově „upgradovat“ CPU, přijde už v příštích Xeonech Sapphire Rapids.

Na Twitteru vystupuje čínský leaker YuuKi_AnS, jenž už v minulosti ukázal vzorky procesorů Sapphire Rapids, které pak dokonce delidoval a rozebíral, takže dlouho před vydáním CPU publikoval snímek čipu. Nyní se už dostal přímo k testování funkčních vzorků, které odhalilo některá překvapení.

Sapphire Rapids je next-gen generace serverových procesorů s novou platformou s osmikanálovými pamětmi DDR5 a PCI Expressem 5.0. Čipletové procesory (přičemž jádra jsou transparentně propojená přes hranice čipletů, což vypadá hodně pokročile). Architektura jader CPU bude Golden Cove z procesorů Alder Lake, ale s 2MB L2 cache místo 1,25MB. Ale zejména také budou mít přidané instrukce AMX pro akceleraci maticových operací neuronových sítí a SIMD instrukce AVX-512. Ty nebudou na rozdíl od Alder Lake vypnuté a navíc budou mít jako v předchozích procesorech mít zvýšený výkon přidáním druhé 512bitové jednotky FMA.

Více: Rozbor CPU architektury Golden Cove: FPU a SIMD, AMX a AVX-512 v serverech

Respektive – že nebudou vypnuté, se očekávalo. YuuKi_AnS zjistil, že vzorky procesorů Sapphire Rapids, které má v rukou, zapnuté AVX-512 nemají. A také chybí instrukce AMX. Údajně to vypadá, že by tyto novinky mohly být ve výchozím stavu procesorů po koupi vypnuté. Nebude to ale tak, že je zapnete v BIOSu jako normálně, ale budou schované za onou „DLC“ bariérou, softwarovou infrastrukturou, která umožní jejich zapnutí po koupi procesoru, patrně formou vložení nějakých upgradovacích kódů a certifikátů. V kódu, která tuto novinku zprovozňuje v Linuxu, se tomu říká Intel Software Defined Silicon (SDSi). Patche by měly zřejmě být začleněné do Linuxu 5.18 (repozitář můžete studovat zde).

Podle YuuKi_AnS tedy zřejmě právě instrukce AVX-512 a AMX budou něčím, na čemž tento systém segmentace různých funkcí procesorů bude vyzkoušen. Další takovou funkcí by údajně mohly být některé možnosti využití pamětí HBM2e, které budou v některých procesorech Sapphire Rapids integrované.

https://twitter.com/yuuki_ans/status/1492532868202909698

Placená „DLC“ funkce bude také podpora vyšších kapacit RAM

Vedle toho mají být zpoplatněné další funkce. Podle stejného zdroje půjde o NVMe RAID (funkce VROC, která byla zpoplatněná už dávno, ale pomocí hardwarového klíče), funkci Intel Speed Select a za poplatek také bude podpora vyšších kapacit pamětí – a to ve dvou stupních, připlatit si budete moci za „Medium Memory SDSi Upgrade“ a „Large Memory SDSi Upgrade“. Intel tyto schopnosti dříve zapínal jen u vybraných procesorů s příponou M a L v názvu. „L“ umožňující maximální fyzicky využitelnou kapacitu RAM nebo RAM+Optane Persistent Memory, byla Legrace za 3000 dolarů. Teď se tedy tato segmentace místo toho bude řešit pomocí těchto softwarových aktivací a model M nebo L si budete moci udělat z jakéhokoli Xeonu, pakliže tedy zaplatíte za aktivační kód.

https://twitter.com/yuuki_ans/status/1492737908096188417

Toto asi moc nepotěší uživatele, kteří by chtěli AVX-512 používat třeba pro vývoj aplikací, ovšem je asi třeba počkat na to, jak drahé „licence“ k těmto funkcím případně budou. Také asi je možné, že si to Intel ještě rozmyslí a zatím jen testuje, jak by případně tato koncepce fungovala a byla přijata.

Je docela otázka, jak toto Intel udělá u highendové desktopové verze Sapphire Rapids-X, která bude od serverové platformy odvozená. Tam by takto komplikovaná segmentace byla nová a z pohledu třeba těch vývojářů softwaru asi dost nepříjemná.

Galerie: Vzorek procesoru Intel Xeon Sapphire Rapids s čiplety a FPGA

Placené „DLC“ pro procesory v minulosti

Pokud sledujete hardware delší dobu (kde delší znamená víc jak deset let), možná si vzpomenete, že takovýto softwarový upgrade už kdysi Intel v méně sofistikované formě zkoušel. Bylo to pod jménem Intel Upgrade Service ještě před procesory Sandy Bridge, na platformě LGA 1156 u levnějších derivátů architektury Nehalem.

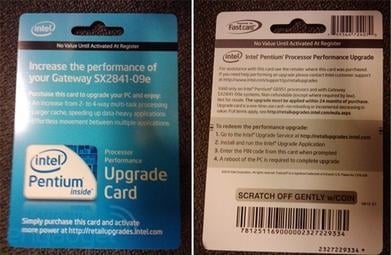

Kartička s odemykacím kódem Intel Upgrade Service (Zdroj: Wikimedia Commons)

Kartička s odemykacím kódem Intel Upgrade Service (Zdroj: Wikimedia Commons)Tehdy se dalo dvoujádrové Pentium G6952 upgradovat na ekvivalent Core i3 pomocí kódu, který jste si pořídili na papírové kartě. Přidalo to část předtím vypnuté kapacity L3 cache a Hyper Threading, ovšem cena byla asi 50 dolarů, koupit nejdřív levnou verzi a pak si to rozmyslet se hrubě nevyplácelo. A úspěch to asi nebyl ani u zákazníků, poté Intel tento nápad zase opustil až do dnešní doby, i když na chvilku ještě vydržel u lowendových procesorů následující generace Sandy Bridge.