V posledních letech narůstá konkurence pro procesorovou architekturu ARM v podobě otevřeného ekosystému kolem instrukční sady RISC-V, která má ambice stát se levnější a ne na jednom vlastníkovi závislou alternativou. RISC-V není zatím tak zralá a tyto architektury nemají srovnatelný výkon, ale postupně „rostou“. Firma SiFive, která je jedním z jejích tahounů, teď uvádí jádro SiFive P870, které by konečně mohlo laťku výkonu zvednout.

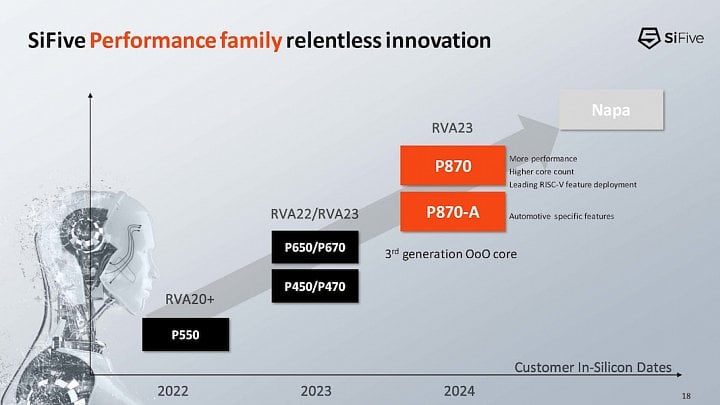

Jádra RISC-V, která je možné si licencovat pro použití v procesoru nebo embedded čipu, nabízí množství firem (dokonce je mezi nimi i česká společnost z Brna, Codasip). SiFive z nich je asi nejznámější mimo jiné díky navázání na autory instrukční sady, ale také tím, že o ni měl jednu dobu dokonce zájem Intel. Právě SiFive nyní představila architekturu nazvanou Performance P870, která by měla přinést výrazný výkonnostní skok. Vedle P870 bude existovat ještě verze P870-A pro automobilový průmysl, která má některé specifické vlastnosti navíc (registry chráněné paritou, cache s ECC), ale architektonicky by mělo jít o odvozený design.

Performance P870

Předchozí jádra SiFive Performance P650 a P670 (evoluce s přidanou podporou vektorových instrukcí RVV) sice tvořila nejvýkonnější stupeň v nabídce CPU architektur dostupných od SiFive, ale byla stále poměrně úzká. Měla pořád jen dvě celočíselné ALU v jádře, byť je firma považovala za konkurenci jader ARM Cortex-A77 a A78, která už jsou i na dnešní poměry relativně výkonná (byť už nemají na to, aby byla „prime jádrem“ pro jednovláknové aplikace). Nové jádro P870 by mělo být už dost silnější.

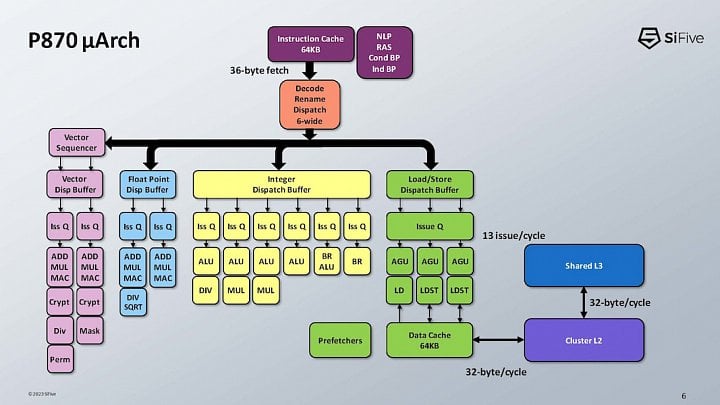

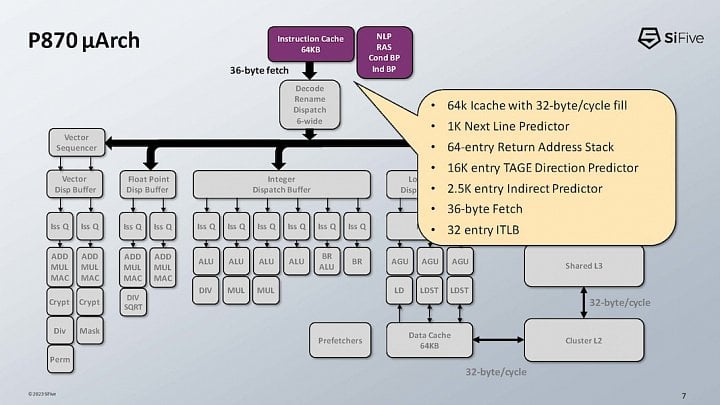

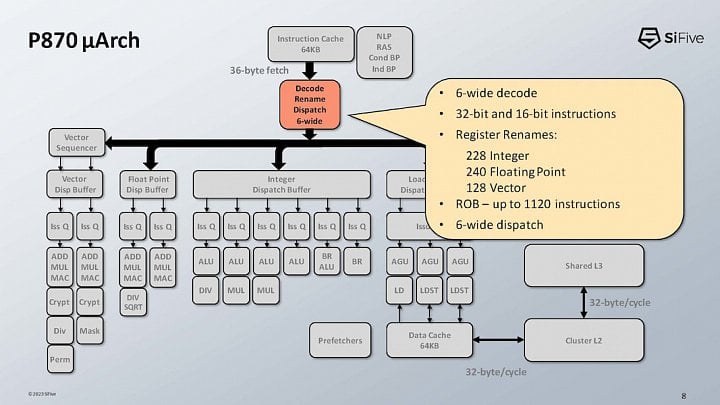

Performance P870 je out-of-order jádro se 6-wide dekódováním instrukcí (má tedy paralelně šest dekodérů, jako třeba současná jádra Applu). Také fáze dispatch a rename zvládají šest instrukcí za cyklus. Fetch pak z paměti načítá až 36 bajtů každý cyklus, což může být až devět 32bitových instrukcí.

13-wide issue, 5× ALU

Jádro má ale také výrazně silnější backend s jednotkami vykonávajícími instrukce. Celočíselná část má celkem pět ALU (jako nynější velké jádro Intelu Golden Cove) – z nich jedna podporuje celočíselné dělení, dvě násobení a jedna také větvení. Pro větvení je pak ještě v jádru šestá, vyhrazená jednotka.

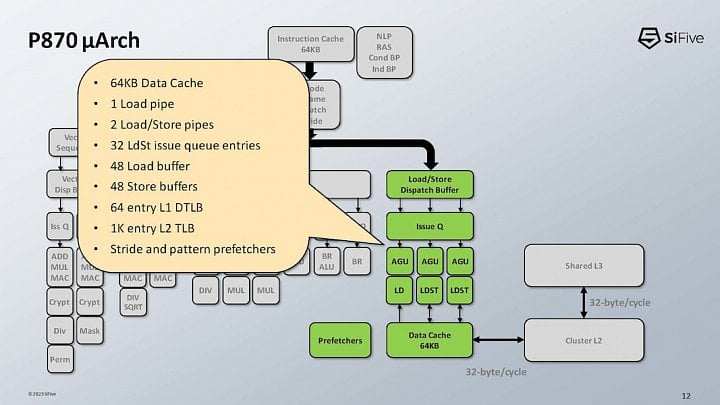

Load/store část má tři jednotky AGU, z nichž dvě pipeline podporují čtení i zápis do paměti a třetí jen čtení, store i load fronty mají každá hloubku 48 položek. Jádro má samozřejmě různé inteligentní prefetchery reagující na vzorce pozorované v přístupech k datům.

Vedle toho má jádro separátní FPU s dvěma jednotkami. Obě umí floating-point operace násobení, sčítání a MAC (multiply-accumulate), jen jedna z jednotek podporuje navíc ještě floating-point dělení a odmocňování.

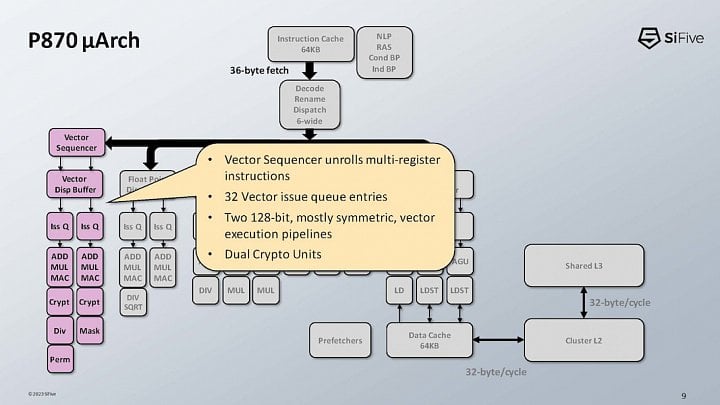

128bitové SIMD

Vedle FPU je v jádru ještě samostatná vektorová (SIMD) jednotka zpracovávající instrukce RVV, která má také dvě pipeline. Obě umí většinu hlavních operací (SIMD sčítání, násobení, MAC), a navíc ještě kryptografickou akceleraci. Další operace jsou možné jen v jedné z jednotek, takže jádro zvládne jen jednu za takt. První pipeline má SIMD děličku a shuffle jednotku provádějící velmi důležité permutace. Operace typu Mask jsou zpracovávané v druhé pipeline.

Šířka těchto vektorových jednotek je 128 bitů, což znamená, že mají teoretický výpočetní výkon („throughput“) zhruba odpovídající SIMD instrukcím SSEx u Intelu a AMD, instrukcím Neon u ARMu nebo nyní nejčastější základní implementaci SIMD instrukcí SVE/SVE2, u kterých firma ARM v aktuálních jádrech Cortex a Neoverse používá také jen 128bitovou šířku.

Instrukce RVV jsou navržené s flexibilní šířkou vektoru podobně jako ARM SVE. Teoreticky by měl tedy jednou napsaný kód fungovat i na budoucích CPU jádrech s jinou šířkou, ale přináší to zase určité jiné komplikace dané tím, že při psaní či ručním optimalizování kódu programátor neví jistě, jaké fyzické jednotky budou jeho kód zpracovávat.

Vektorové/SIMD rozšíření bylo u architektury RISC-V něco, na co se dlouho čekalo, a jádra SiFive ho dlouho postrádala. To byl deficit proti Cortexům od ARMu, kde je SIMD automatická součást. Je proto důležité, že generace P870 je už bude mít standardně, byť dvě 128bitové jednotky nejsou mnoho (Apple nebo třeba ARM Cortex-X4 například poskytuje čtyři). O generaci zpět bylo vektorové rozšíření poprvé implementováno v jádru P670, v jeho první verzi P650 ještě chybělo.

Celkově jádro může do těchto jednotek tedy za cyklus umístit (issue) až 13 operací za cyklus, ale předchozí fáze zpracování stavěné na šest instrukcí za cyklus toto samozřejmě nemohou udržet trvale. Všechny vykonávací jednotky mají před sebou vyhrazenou issue frontu s výjimkou load-store části, kde je pro všechny tři pipeline jedna společná issue queue, ale se schopností zpracovat tři operace za cyklus.

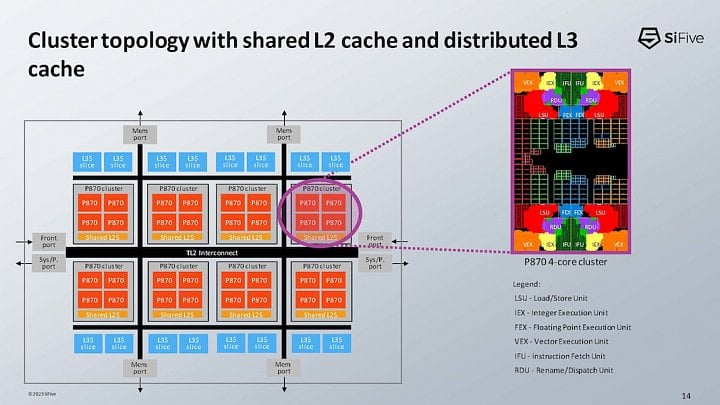

RoB na 280 instrukcí

Jádro bude mít 64kB L1 instrukční cache i 64kB L1 datovou cache, z níž lze poslat 32 bajtů za cyklus do L2 cache (nebo zpět). L2 cache bude sdílená více jádry na úrovni klastru (ten mohou tvořit až čtyři jádra), nebude tedy privátní. Dále pak procesory budou používat L3 cache sdílenou mezi všemi klastry. Tato L3 cache by byla distribuovaná, složená z bloků přidružených k jednotlivým klastrům.

SiFive prozradila i velikosti některých dalších struktur. TLB instrukční L1 má 32 položek, datové L1 pak 64 položek a L2 TLB má 1 tisíc položek. Return Adress Stack má 64 položek, Next Line Predictor má 1 tisíc položek. Prediktor větvení typu TAGE má paměť o 16 tisících položkách a prediktor nepřímého větvení má 2,5 tisíce položek.

Jádro má 228 fyzických obecných registrů, 240 floating-point registrů a 128 vektorových registrů. Reorder Buffer má hloubku 280 položek, což je někde mezi Zenem 3 a Zenem 4 od AMD, podobnou hloubku (288) má také ARM Cortex-X2. Ovšem při použití fúzovaných (bundled) instrukcí zabírá bundle jenom jednu položku, přičemž může být tvořen až čtyřmi operacemi. Při maximálním využití této schopnosti by se tedy teoreticky vešlo až 1120 instrukcí, což ale samozřejmě není ekvivalentní skutečnému ROB o 1120 položkách.

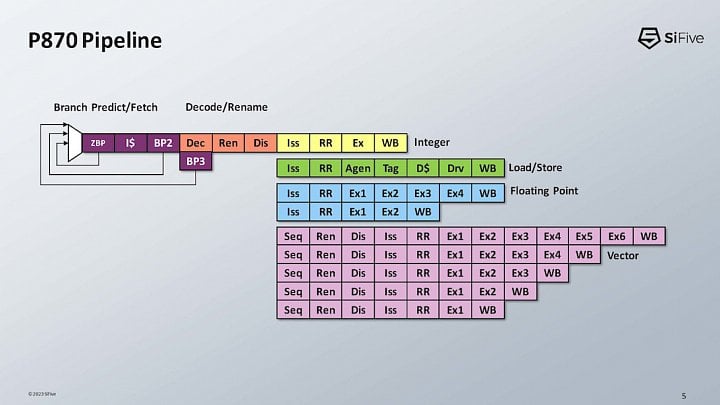

Ukázána byla i hloubka pipeline, která má od 10 (ALU instrukce) až 13 stupňů (floating-point, load-store) při skalárních operacích, ale až 18 stupňů v případě některých vektorových instrukcí.

29% skok v IPC

Podle SiFive by jádro P870 mohlo mít až o 29 % vyšší IPC než předchozí jádro P670 (což je velký skokový nárůst, ale i díky tomu, že se začíná z relativně nižšího výchozího stavu). Zatímco jádro P670 prý v benchmarku SpecINT2006 dosahuje 13,2 bodů na 1000 MHz frekvence, toto nové jádro P870 má dosahovat 17 bodů na 1000 MHz.

Frekvence by přitom snad mohly být až někde okolo 3 GHz. Podle prezentace bude tato architektura také opět podporovat tvorbu CPU s vyšším počtem jader než u předchozích generací. Ale to, kolik jader se v určitých SoC objeví, bude samozřejmě záležet na volbě a záměru implementátorů čipů, kteří si architekturu Performance P870 licencují.

Oficiální uvedení teprve přijde

Jádro SiFive Performance P870 ještě není úplně formálně odhaleno. Nynější informace pocházejí z prezentace architektury na Hot Chips 2023, kde firma o jádru přednášela. Oficiální produktové odhalení by prý mělo být během několika týdnů a mohly by po něm přibýt ještě nějaké další informace, které se ale budou asi spíš týkat obchodních aspektů, plánovaných termínů dostupnosti čipů a podobně, hlubší technické detaily než na Hot Chips asi už nebudou.

V reálných procesorech či embedded řešeních se tato jádra objeví až se značným zpožděním, dost možná i třeba až v roce 2025 spíše než v tom příštím, protože SiFive nové architektury oznamuje poměrně v předstihu.

Tip: Jim Keller chystá RISC-V procesor, který může zatočit s x86 i ARMy. Je u toho i Raja Koduri

Tip: Elitní veteráni z Apple, Intelu a AMD chystají výkonné procesory RISC-V. Je to další Nuvia?

Zdroj: ServeTheHome