AMD příští měsíc začne prodávat jak mobilní procesory Ryzen AI 300 „Strix Point“ s architekturou Zen 5, tak i desktopové Ryzeny 9000 s tímto novým jádrem. AMD o něm na Computexu řeklo jen některé vágní věci a zmínilo zvýšení IPC o 16 % (pro vybrané programy, ovšem), ale na internetu se teď objevil test už přímo konkrétního procesoru, který toho o architektuře Zen 5 odhalil víc. A jsou to hodně zajímavé věci.

Tento test je psaný čínsky a uveřejnil ho David Huang, který se dostal k notebooku s procesorem Ryzen AI 9 365, na svém blogu. Podle jeho upozornění nemusí procesor předvádět úplně odpovídající výkon, protože firmware nemusí být finální a také možná jde o vzorek procesoru. Nicméně podstatné architektonické rysy se z něj dají zjistit.

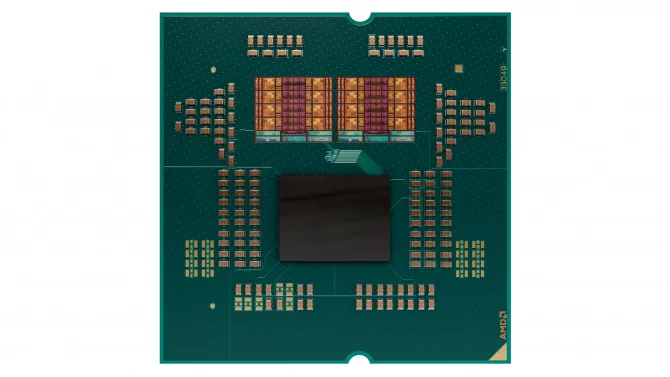

Ryzen 9 AI 365 je určený pro notebooky, je to tedy APU Strix Point, přičemž je druhým modelem v řadě. Nese čtyři jádra Zen 5 s maximální frekvencí 5,0 GHz (top model má boost 5,1 GHz), která jsou v jednom bloku CCX se sdílenou 16MB L3 cache.

APU Strix Point má dále osm jader Zen 5c, která jsou v druhém odděleném bloku CCX s 8MB L3 cache. Zdá se, že jejich maximální takt je 4,0 GHz (v modelu 365), v mnohovláknových úlohách možná poběží spíše někde okolo 3,7 GHz.

Bohužel tedy všech 12 jader nemá jednu společnou L3 cache, kterou by CPU dokázalo využít i v jednovláknové úloze. Ryzen AI 9 365, který byl testován, má počet jader Zen 5c osekaný na 6 z 8, jde tedy o desetijádro s 20 vlákny. Testovaný notebook byl vybavený 32 GB paměti LPDDR5X-7500 a TDP měl nastavené na 54 W.

Nárůsty výkonu na 1 MHz u vzorku mobilního Zenu 5

Nejdřív možná informace o naměřeném IPC (tedy výkonu na 1 MHz frekvence jádra), i když ty na tomto testu je třeba brát asi s největší rezervou – jak už bylo řečeno, výkon nemusí odpovídat finálnímu produktu. Jednovláknové zlepšení IPC měřil Huang v SPEC CPU 2017 (přesněji v celočíselné části, SPECint rate-1) a vyšlo mu pro Zen 5 zlepšení o +9,71 % proti Zenu 4. Podobně pro Zen 5c, kde je o trošku vyšší nárůst, ale patrně je to zkresleno nižší frekvencí. Největší zlepšení o 24 % je v subtestu 500.perlbench_r, který předchozím architekturám šel relativně hůře a Zenem 5 je to doháněno. Naopak 531.deep-sjeng_r má snížení IPC o 5 %.

Geekbench 6 ovšem už signalizuje zlepšení IPC o +15,28 % (15,13 % pro celočíselné, 15,54 % pro floating point subtesty). Geekbench 5 podobně ukazuje zlepšení IPC o +17,66 % (17,26 % pro celočíselné, 19,02 % pro floating point subtesty). Všechny tyto testy jsou pod Linuxem (Debian sid). Předběžné jednovláknové skóre pro tento vzorek Ryzenu AI 365 mimochodem vyšlo 2995 bodů v Geekbenchi 6 a 2286 pro Geekbench 5. Mnohovláknová skóre pak byla 14 530 a 13 926 bodů (připomeňme, že jde ořezaný 10jádrový model, také jednovláknový test bude u 12jádrového modelu HX 370 asi o pár desítek bodů lepší kvůli 100 MHz navíc).

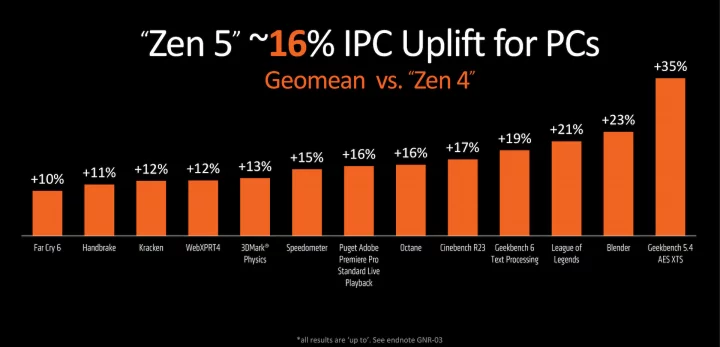

Podle prezentace na Computexu 2024 by Zen 5 měl mít nárůst výkonu na 1 MHz frekvence okolo +16 %, je to ale měřené i v mnohovláknových aplikacích

Architektonické rysy

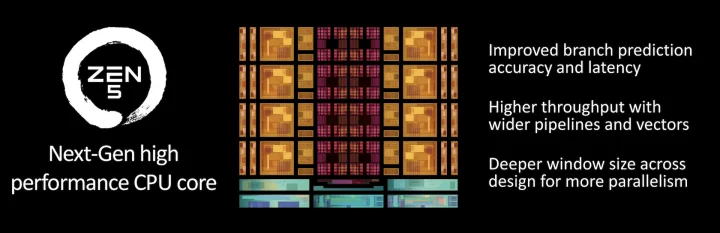

Co o jádru David Huang zjistil? Mikrobenchmarkování patrně potvrzuje, že přibyly ALU v jádru, nicméně Zen 5 má i některé regrese. Například celočíselné SIMD sčítání má latenci zvýšenou z jednoho cyklu na dva, to se týká jak instrukcí SSEx, tak AVX2 i AVX-512. Patrně to je učiněno s cílem dosáhnout lepších frekvencí, při častých datových závislostech se teoreticky ale může snížit výkon.

Jádro má podle měření zmenšenou uOP cache, což je cache ukládající již dekódované instrukce. Zatímco v Zenu 4 měla kapacitu 6750 položek, Zen 5 se patrně vrátil ke kapacitě 4096 položek, jakou měl Zen 2 a 3 (teoreticky by to mohlo být i proto, že jádro bylo částečně vyvíjeno paralelně se Zenem 4, ne přímo na jeho základu).

Místo toho má Zen 5 přidáno na instrukčních dekodérech, kterých je osm, ovšem ve dvou klastrech. Jádro také umí načítat („fetch“) sekvenci instrukcí programu ze dvou míst L1 instrukční cache současně, aby tyto dva klastry dekodérů mohly pracovat současně. A je schopné takto načítat dva separátní proudy instrukcí (operací) také z uOP cache.

Jádro Zen 5 lépe zpracovává větvení. U větvení, u nichž nedochází ke skoku na jiné místo kódu („non-taken branch“), dokáže za cyklus zpracovat místo dvou hned tři. Zejména ale dokáže za cyklus zpracovat dvě větvení, která ke skoku opravdu vedou („taken branch“), což je komplikovanější varianta. V této disciplíně jde o značné zlepšení, je to patrně umožněno oněmi zdvojenými dekodéry.

Zen 5 má 48kB L1 cache pro data s latencí 4 cykly, což je zvětšení kapacity o 50 % proti předchozím jádrům, při zachované latenci. Intel má u velkých jader stejnou kapacitu (u Sunny Cove a Golden Cove ale měla latenci 5 cyklů, Lion Cove, kde se označuje L0 cache, má také 48 kB s latencí 4 cykly). L2 cache má stejnou kapacitu 1 MB i latenci 14 cyklů jako Zen 4 (předchozí Zeny měly 512kB L2 cache s latencí 12 cyklů). L3 cache má snad zlepšenou latenci z 50 na 46 cyklů, ale zde je třeba dát pozor na to, že v desktopové verzi Zenu 5 s vyšší kapacitou může být latence vyšší.

Pozor, Zen 5 v notebooku a Zen 5 v desktopu asi budou o dost jinačí

Důležité zjištění je, že jádro Zen 5 použité v Ryzenech AI 300 se může lišit od desktopového a serverového Zenu 5. Zdá se, že mezi velkým Zenem 5 a „hustým“ Zenem 5c opět nebude rozdíl v IPC (tedy pokud si odmyslíme vliv menší L3 cache bloku s jádry Zen 5c) ani instrukční podpoře. I Zen 5c podporuje instrukce AVX-512 a má nativně 512bitové SIMD jednotky, jakož i podporu všech instrukcí.

Ale paradoxně může být rozdíl v tom, jak vypadá velké jádro v mobilním Ryzenu AI 300 (Strix Point) proti standardní verzi jádra v desktopu a serveru. AMD podle mikrobenchmarků Davida Huanga osekalo v čipu Strix Point jednotku SIMD (FPU) jak jádra Zen 5c, tak jádra Zen 5 zřejmě na poloviční počet pipeline. Toto snižuje teoretický výpočetní výkon ve 128bitových operacích SSEx a 256bitových operacích AVX/AVX2 na polovinu, jádro jich dokáže zpracovat polovinu za cyklus proti Zenu 4.

Ovšem tyto pipeline zůstávají 512bitové (i u malých jader Zen 5c). Existuje tedy jedna cesta, jak z takovéhoto jádra dostat stejný SIMD výkon jako ze Zenu 4 – použitím 512bitových vektorů AVX-512. Ty totiž jádro zpracovává v jednom průchodu, zatímco Zen 4 s 256bitovými jednotkami si je provádí ve dvou polovinách nadvakrát. Zen 5 i v této osekané verzi tedy může v optimálním AVX-512 kódu mít stejný výkon (teoreticky alespoň) jako Zen 4, zatímco při použití menších vektorových instrukcí výkon bude asi o nějaká procenta trpět.

Jde zřejmě o stejnou věc, jakou AMD udělalo u Zen 2 „Lite“ jader použitých v PlayStation 5 (a pravděpodobně také v APU Mendocino, Ryzenu 7020U). Podle benchmarků udělaných na PS5 zřejmě takto osekaná SIMD jednotka nemusí být až taková rána pro výkon ve velké části aplikací včetně her, jak ukazují testy webu Chips and Cheese. U Zenu 2 „Lite“ AMD totiž ponechalo fronty FPU stejně kapacitní jako u plnotučné verze, což při nižší úrovni využití SIMD operací rozdíly ve výkonu backendu z významné části zamaskovává. Doufejme, že stejně relativně úspěšné to bude u Zenu 5.

Plnotučná SIMD jednotka jen v desktopu?

Je ale dost pravděpodobné, že toto se týká právě jen mobilní verze. Zatím se asi dá očekávat, že desktopový Zen 5 v Ryzenech 9000 bude mít počet pipeline neredukovaný, takže bude mít stejný výkon v operacích SSEx a AVX/AVX2, ale naopak dvojnásobný v instrukcích AVX-512. Je to zatím domněnka, která ještě není potvrzená, ale jinak by to asi velký smysl nedávalo.

Vypadá to tedy, že AMD začne mezi mobilní a desktopově-serverovou verzí jádra dělat větší rozdíly. Doteď byla architektura stejná a lišil se paměťový řadič a kapacita L3 cache, což ve finále mohlo trošku ovlivňovat IPC mobilních Ryzenů směrem dolů. Od nynějška zřejmě změny budou hlubší. Je proto možné, že Zen 5 v Ryzenech AI 300 bude mít o něco nižší IPC než Zen 5 v Ryzenech 9000 (a Epycu 9005).

Tento architektonický rozdíl asi bude mít znatelné dopady na výkon softwarového enkódování a podobných multimediálních úloh na noteboocích. Ve většině aplikací ale bude propad výkonu o dost menší než těch teoretických −50 %. Největší problém by asi mohl být u kódu typu HPC a vědeckých výpočtů, pokud používají jen AVX a SSEx. Takový kód má nicméně asi největší šanci, že u něj bude aplikovatelné AVX-512. Pokud takové výpočty praktikujete, mohly by být řešením chystané výkonné mobilní procesory Strix Halo, které mají 16 jader Zen 5, ovšem pravděpodobně už půjde o jádra desktopové verze, tedy bez tohoto zredukování jednotky SIMD.

Jak přesně budou vypadat projevy této osekané jednotky SIMD/FPU a o kolik naopak bude lepší Zen 5 v desktopu, to uvidíme až po vydání recenzí, a zejména asi nějakých hlubších rozborech časem. Zatím je asi předčasné hodnotit, o jak velký kompromis půjde.

Duální dekodéry – ozvěna Bulldozeru (Steamrolleru)?

Mimo tento kontroverzní rys (doufejme jen u mobilní verze) je tu ještě jedna hodně zajímavá věc. Test Davida Huanga potvrdil, že Zen 5 má dekodéry rozdělené do dvou klastrů po čtyřech, jak už bylo zmíněno. Předchozí jádra AMD měla čtyři dekodéry, takže toto je i není zdvojnásobení. Architektonicky je to patrně dost podobné dvojitým dekodérům jader linie Intel Atom – Tremontu a Gracemontu, které mají dvakrát trojici dekodérů (nový Skymont má dokonce tři takové klastry). Toto ale není rovnocenné jádru, které by mělo osm dekodérů v jednom klastru (jako Intel Lion Cove) a je schopné zapřáhnout všech osm v jednom vláknu.

Zdá se, že Zen 5 toto nedokáže, nebo alespoň ne v úplně triviálním sekvenčním kódu bez větvení. Podle Davida Huanga při testování sérií NOPů vychází, že v lineárním kódu Zen 5 dokáže přes dekodéry prohánět čtyři x86 instrukce za cyklus v jednom vlákně, tedy umí zapřáhnout jen jeden klastr (je na tom tím pádem jako Zen 1 až 4). Více nicméně může jádro zpracovávat, pokud instrukce bere z uOP cache.

Ovšem pokud je v kódu větvení a program skočí na jinou adresu, pak druhý dekodér pravděpodobně může zasáhnout a přidat se, vzhledem k oné schopnosti fetche načítat instrukce ze dvou míst cache současně. V takovém případě první klastr dekóduje kód až včetně instrukce větvení a druhý klastr začne hned dekódovat tam, kam kód skočí, protože tato adresa je vždy začátkem instrukce. Tímto se tedy obejde problém architektury x86, že má proměnnou délku instrukcí, a nelze tedy předem triviálně vědět, kde instrukce začínají, jako u architektury ARM s konstantními délkami instrukcí (u které by toto schéma s klastry nebylo třeba a dekodéry se snáze paralelizují v jednom klastru).

Tudíž druhý klastr dekodérů pomáhá méně často, ale je možné, že stále přidává relativně dost IPC, protože větvení by v kódu mělo být často k dispozici. Uvádí se, že průměrně může připadat až jedno větvení na každých šest instrukcí kódu, ale to samozřejmě bude dost záviset na typu programu, který berete jako měřítko. Nicméně pokud by takto výrazně větvený kód byl častý, pak může Zen 5 ze dvou klastrů často profitovat, podobně jako malá jádra Intelu. Ta nicméně možná mají schopnost zapojit více klastrů dekodérů častěji, protože používají předdekódování instrukcí, které dopředu zjišťuje místa, kde instrukce začínají.

David Huang tipuje, že v budoucnu by AMD mohlo místo používání uOP cache také přejít na takový systém předdekódování a jeho jádra by mohla pracovat podobně jako „mont“ jádra od Intelu. To je ovšem jen hypotéza, těžko vědět určitě. To, jak často dokáže Zen 5 v současné podobě druhý klastr dekodérů uplatnit, bude třeba ještě hlouběji zanalyzovat.

Toto vše ale platí pro běh jednovláknového kódu na jádru. Situace se ale hodně mění, pokud jádro Zen 5 zapojí SMT a zpracovává dvě vlákna. David Huang ověřil, že v takovém případě skutečně dekóduje až osm instrukcí za cyklus. Stane se totiž to, že každé z vláken dostane vyhrazený jeden z klastrů, takže zatímco zbytek prostředků v jádru sdílí, dekodéry má vlákno dedikované. Toto by mělo pomáhat mnohovláknového výkonu procesoru (v situaci, kdy se na jádrech zatěžují obě vlákna). Zen 5 by tedy mohl přinášet větší procentuální zlepšení výkonu na 1 MHz v mnohovláknových aplikacích než v těch jednovláknových.

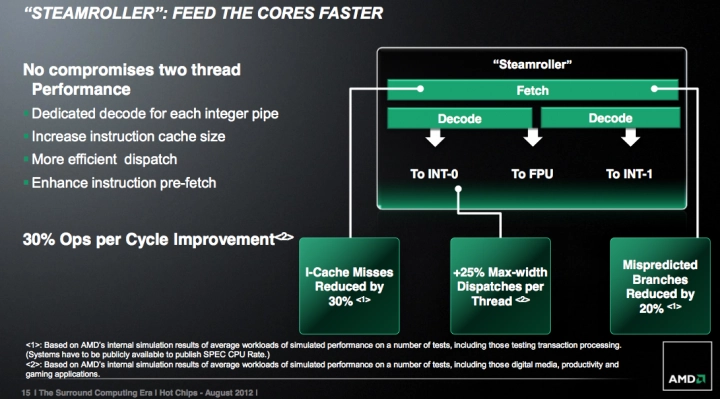

Je zde zajímavá historická paralela s vývojem předchozí a ne úplně úspěšné rodiny CPU architektur AMD, jádry linie Bulldozer – zejména ale s jejími pozdějšími deriváty. AMD používalo u Bulldozeru modul tvořený dvěma jádry s velkou mírou vzájemné integrace a některými částmi sdílenými. Například FPU byla sdílená kompletně a chovala se už tehdy jako jedno jádro s SMT. Jádra měla samostatné celočíselné a AGU jednotky, ale zrovna klastr dekodérů (také čtyř) měla sdílený.

Po prvních dvou architekturách Bulldozer a Piledriver ale AMD udělalo kompromis a v architektuře Steamroller dalo separátní vyhrazený dekodér oběma jádrům. Zen 5 tak v jistém omezeném smyslu (a v tomto dílčím detailu) opakuje přístup ze Steamrolleru. Nicméně, ve Steamrolleru nemohlo jedno jádro v jednovláknové úloze profitovat z druhého klastru dekodérů, což u Zenu 5 snad v oné situaci s větvením půjde.

Pěkná synergie s SMT

Tato koncepce vypadá jako potenciálně zdařilý prvek. Je zajímavé, že zatímco Intel teď na SMT sází méně a pro mobilní a desktopové procesory si raději zjednoduší jádro s nadějí, že to umožní snáze zlepšovat jednovláknový výkon, AMD u Zenu 5 podle všeho na SMT klade důraz větší než dřív. Tak si alespoň na první pohled lze vykládat to, že jádro má zdvojené dekodéry, jejichž plný výkon dokáže využít až v momentě, kdy je použitý SMT a běží na něm dvě vlákna.

Nicméně elegantní na tom je právě to, že to na rozdíl od Steamrolleru vlastně není přidání prostředků čistě jen pro dobro SMT. Intel zase používá stejné zdvojené, nebo dokonce ztrojené klastry dekodérů v jádrech E-Core čistě jako prostředek ke zlepšení jednovláknového výkonu, kdežto potenciální zlepšení pro mnohovláknové zátěže využito není.

Technika SMT je koncepčně zajímavá proto, že v jistém ohledu nenutí architekty CPU vybrat si mezi jednovláknovým a mnohovláknovým výkonem, protože stejné prostředky v jednom jádru mohou přispívat v obou disciplínách. Jádra s vysokým IPC a jednovláknovým výkonem dosaženým skrze velký počet výpočetních jednotek také obvykle málokdy zaměstnají všechny své prostředky najednou kvůli limitům v možnostech paralelního out-of-order zpracování instrukcí. SMT při zpracování dvou vláken dovolí „rekuperovat“ část takto nevyužitého výpočetního výkonu. Výkonu při použití SMT zde ale přímo prospívá právě přidávání těch prostředků provedené za cílem zvýšení jednovláknového výkonu, oba cíle jsou tedy v symbióze a s trochou štěstí to architekt může úspěšně hrát na obě strany.

Pokud by AMD chtělo zlepšit mnohovláknový výkon tím, že zdvojí některé struktury tak, že každé vlákno bude mít vlastní, jde to proti tomuto duchu, protože tyto prostředky navíc nebude možné použít, když bude běžet jednovláknová úloha. Ovšem zde u zdvojených dekodérů se snad podařilo tyto zdvojené zdroje zároveň využít v jednovláknovém režimu (což je rozdíl proti Steamrolleru) i v SMT režimu (rozdíl proti E-Core od Intelu), což působí na papíře jako velmi elegantní a efektivní nápad, přesně v souladu s tou koncepcí SMT, kdy nově přidávané a zlepšované prostředky jádra slouží zároveň ke zlepšení jednovláknového, i ke zlepšení mnohovláknového výkonu.

Nevíme ovšem, zda za tuto koncepci AMD třeba neplatí nějakou vysokou cenu ve spotřebě, ploše čipu nebo komplexitě, takže nemůžeme vědět jistě, zda toto řešení opravdu funguje dobře i v praxi. Na první pohled elegantní nápad někdy musí být kvůli podobným věcem opuštěn, protože primitivnější a méně chytré postupy nakonec mohou přinášet efektivnější výsledky.

Tyto testy dodaly dost zajímavé poznatky, ale jak už bylo řečeno, je třeba je chápat jako předběžné, zejména tedy ještě neberte jako definitivní ty údaje o procentuálních zlepšeních IPC, jakkoli je to lákavé. V momentě, kdy vyjde větší množství recenzí (a budou k dispozici i testy desktopové verze), snad bude lépe možné zhodnotit, jak velký pokrok je Zen 5 proti Zenu 4 a jak výhodné, nebo nevýhodné jsou kompromisy, které podle těchto předběžných testů byly učiněné v mobilní verzi jádra.

Zdroj: David Huang