Názor k článku Z recenzí Ryzenu: přetaktování, SMT a herní výkon, potřeba optimalizací a podpora ECC od Maudit - K SMT - jadra v Ryzenu vyuzivaji spolecnou...

-

Maudit (neregistrovaný)

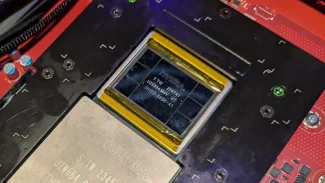

K SMT - jadra v Ryzenu vyuzivaji spolecnou cache se SMT i bez ni, ale vzhledem k tomu, ze dve logicka jadra jsou soucasti jednoho fyzickeho, tak pridelovani vypoctu temto dvema znamena, ze se navzajem ovlivnuji. A jde prave hlavne o cache - kdyz mas na jednom fyzickem jadre dve ruzne ulohy, museji vyuzivat stejnou cache. De facto se tak musi do jednoho prostoru vejit data pro dve ruzne veci (oproti tomu, kdyby tam byly data jen pro jednu). A vzhledem k pomale cachi na Ryzenu je ten efekt mnohem silnejsi u AMD, nez u Intelu (i kdyz ani ten se tomu logicky nemuze vyhnout).