Velký upgrade jádra bez změny plochy čip(let)u?

Rozbor architektury AMD Zen 5 jsme původně vydali již 18. 7. Ale AMD tentokrát netypicky odhalilo detaily architektury ve dvou vlnách, nejprve omezeně na tzv. Tech Day a poté důkladněji na dalším brífinku minulý týden, kterého jsme měli možnost se zúčastnit. Nyní jsme článek o Zenu 5 proto doplnili o všechny nové informace. Závěr se tím nemění, ale ukazuje se, že změn a novinek je v jádru oproti Zenu 3 a 4 provedeno ještě víc.

Jsou to zhruba dva týdny do vydání procesorů AMD s novou architekturou Zen 5. Tento týden jsme se k těmto CPU dozvěděli konečně pořádné podrobnosti o jejich samotné architektuře, které AMD zveřejnilo na akci Tech Day. Už tedy můžeme rozebrat změny, které firma udělala v jádru oproti Zenu 4 – a že jsou hodně rozsáhlé, asi více, než se v červnu zdálo. A firma také zopakovala příslib 16% zvýšení IPC u těchto procesorů.

AMD potvrdilo, že Zen 5 používá 4nm proces N4P od TSMC jak pro desktopový Ryzen 9000 (přesněji pro jeho CPU čiplety), tak pro mobilní Ryzen AI 300 neboli APU „Strix Point“. Strix Point je poměrně velký čip s plochou 232,5 mm² (předchůdci Phoenix a Hawk Point s architekturou Zen 4 mají plochu 178 mm²), což implikuje zvýšené výrobní náklady.

Toto ale překvapivě neplatí pro desktopovou verzi: CPU čiplet s osmi jádry Zen 5 pro Ryzeny 9000 se nezvětšil proti čipletu Ryzenů 7000. Má údajně plochu 70,6 mm², zatímco u 5nm čipletu Zenu 4 se uvádí 71 mm². IO čiplet je stále stejný, tedy 6nm čip s plochou 122 mm². Zdá se tedy, že jádro Zen 5 samo se o moc nezvětšilo, nebo ho AMD nechalo ztloustnout jen o tolik, kolik se podařilo optimalizací designu a použitím mírně lepšího 4nm procesu ušetřit jinde. Patrně se tak ještě víc rozevřou nůžky mezi velikostí jader od AMD a od Intelu, jehož P-Core (výkonná jádra) mají o dost větší plochu než jádra linie AMD Zen.

Jeden z hlavních inženýrů (či nyní manažerů inženýrských týmů) Mike Clark potvrdil v rozhovorech na Tech Day, že Zen 5 je v linii architektur Zen nové jádro, které z velké části staví nový základ. To byl i Zen 3, ale v tomto případě se asi jedná o hlubší změnu, protože byl opuštěn dlouho udržovaný základ postavený kolem jádra se čtyřmi dekodéry a ALU, který se držel od Zenu 1 až po Zen 4. Zen 5 místo toho přináší nový širší základ, na kterém se bude do budoucna zase dál stavět (i když to tentokrát nemusí nutně být na tak dlouho).

Některé investice do této reorganizace jádra se dost možná budou vracet až v dalších generacích. V některých ohledech asi Zen 5 může hlavně připravovat půdu, protože prostředky firmy se soustředily na to vytvořit úspěšně tento základ a první funkční generaci, ne na to, aby hned obsahovala všechna potenciální vylepšení, která by se dala přidat. Mike Clark jako příklad prozradil, že Zen 5 nemá aktuálně schopnost fúzování instrukcí NOP, kterou předchozí jádra obsahují (až čtyři NOPy v pipeline procesoru a v RoB zabíraly jen jedno „místo“) – proto, že by měla o něco menší přínos než ve starších užších jádrech, a proto bylo rozhodnuto nechat její znovuzačlenění na později.

Článek pokračuje na další straně.

Frontend: Největší novinka jádra

Dopředu se o Zenu 5 vědělo to, že přinese výrazné posílení SIMD jednotek na dvojnásobnou 512bitovou šířku a také rozšíří jádro (jak už bylo zmíněno). Nakonec však jsou stejně velké změny ve frontendu, který se stará o to, aby samotné vykonávací jednotky měly co na práci, jádro je tedy výrazně upgradováno prakticky všude.

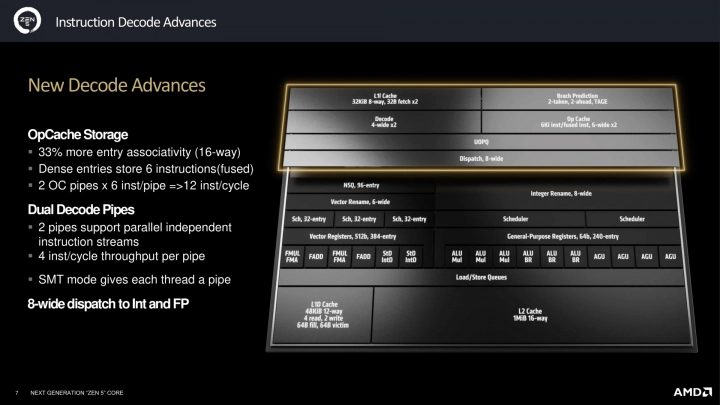

Nejzásadnější změna ve frontendu je, že jádro má zdvojené bloky provádějící fetch a dekódování instrukcí, a to ne ve smyslu prostého zdvojnásobení propustnosti, ale to, že jádro má tyto části dvakrát. Instrukční L1 cache podporuje načítání instrukcí programu ze dvou míst současně (fetch je 2× 32 bajtů za cyklus), tedy dvou proudů instrukcí. Stejně tak je současně možné brát instrukce ze dvou míst také z uOP cache, která ukládá již dekódované instrukce.

Ty jsou konzumovány dvěma klastry dekodérů. Zatímco předchozí čtyři generace jader Zen mají všechny čtyři dekodéry (tedy schopnost dekódovat čtyři instrukce za cyklus), Zen 5 má dva klastry těchto čtyř dekodérů, každý schopný zpracovávat jeden z oněch dvou proudů instrukcí.

Tato konfigurace se může chovat jedním ze dvou způsobů. Jádro Zen 5 nadále poskytuje SMT, může tedy zpracovávat dvě vlákna najednou. V takové situaci dostane každé vlákno jeden dekodér, a má tedy tolik dekódovacích prostředků, kolik měla předchozí jádra celkově. Mike Clark z AMD ale potvrdil, že oba dva klastry dekodérů může jádro použít i jen při běhu jediného vlákna (také řekl, že u jader Zen jsou typicky všechny prostředky jádra vždy k dispozici i jen jedinému běžícímu vláknu).

Asi to však má svá omezení a jádro není schopné oba klastry zapojit tak často jako jádra E-Core od Intelu jako Gracemont a Skymont, kde je podobná technologie také použitá. Pravděpodobně je to tak, že druhý klastr dekodérů se může zapojit tehdy, pokud v programu dochází k větvení a je detekován skok programu na jinou adresu (tedy větvení, pro které predikce říká, že skutečně bude provedeno). Druhý klastr dekodérů tak nemusí čekat, až dekodéry prvního klastru dokončí práci, protože zná místo, kde může začít dekódovat, jelikož na něm určitě začíná nová instrukce.

Občas se uvádí, že v kódu x86 programů bývá až jedno větvení na šest instrukcí, což by dovolovalo využívat oba klastry relativně často, a může to tedy o trošku zvyšovat celkové IPC. Ovšem asi to má ten efekt, že jádru Zen 5 vyhovuje takové kompilování kódu, aby častěji využívanou cestou bylo provedení skoku oproti neprovedení. Toto je něco, co může vyžadovat profilování a rekompilování softwaru, protože ve starších architekturách je většinou výhodnější, když větvení většinou provedená nejsou, protože dříve jádra zvládala méně provedených než neprovedených větvení.

Nicméně schopnost současného použití těchto dvou klastrů dekodérů bude pravděpodobně dále rozvíjena v budoucnosti, takže eventuálně asi jejich přínos pro IPC poroste. Jde o jednu z těch věcí, kde Zen 5 staví infrastrukturu pro Zen 6, 7 a tak dále.

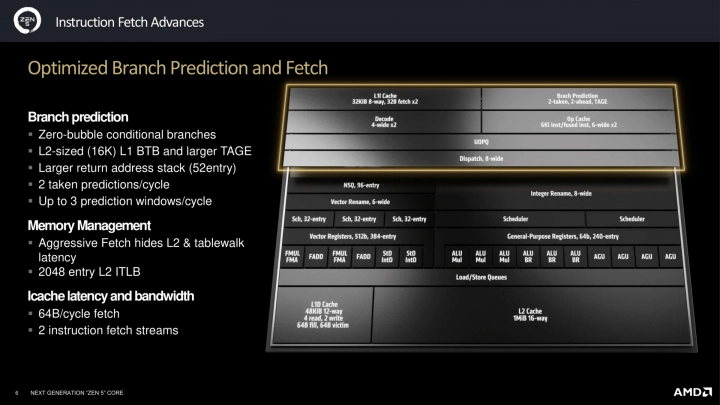

Jádro Zen 5 má vylepšenou predikci větvení pro větší úspěšnost předpovědí (což je něco, kde se dělávají zlepšení v každé generaci). Predikce má nejen mít nižší latence, ale také větší propustnost – tedy schopnost zpracovávat více větvení za cyklus.

2-ahead prediktor větvení

Prediktor větvení používá design nové generace založený na tzv. 2-ahead koncepci. Dokáže zpracovávat podmíněné skoky bez prodlevy a umí zpracovat dvě provedená větvení (taken branches) za cyklus, což je velký upgrade. Jádro díky této schopnosti dokáže při predikci dvou provedených skoků během jednoho cyklu pracovat až s třemi predikčními okny kódu. L1 BTB (Branch Target Buffer) byl rozšířen z 1,5K na masivních 16K entries, a TAGE je také větší. Jádro také dostalo větší return address stack o 52 položkách, pro lepší výkon při návratech z volaných funkcí.

Po fázi dekódování následují fáze rename a dispatch, které byly také rozšířené a místo šesti instrukcí (operací) za cyklus mají zvládat osm operací za cyklus, jde tedy o další část onoho celkového rozšíření jádra. 8 operací za cyklus zvládá i úplně finální fáze retire, AMD jí tedy nedává vyšší kapacitu, než má dispatch, jako to dělá Intel. Šířku dispatche a rename (přejmenování registrů) ale mají jádra AMD i Intelu stejnou.

uOP cache je zmenšená, ale vejde se toho do ní víc?

Dispatch může kromě oněch dvou klastrů dekodérů krmit také uOP cache. Ta by snad měla mít kapacitu 6000 položek, což je o polovinu více než u Zenu 2 a 3, ale o něco méně než u Zenu 4 (ten měl zřejmě 6750 položek). Z této uOp cache může proudit dál špičkově až 12 či 2× 6 (už dekódovaných) instrukcí za cyklus.

Ačkoliv uOP cache byla zmenšena, ve skutečnosti to nemusí znamenat regresi. Je tu totiž jedna důležitá změna. V předchozích generacích každá uOP zabíral jednu položku, kdežto v Zenu 5 je v jedné položce uložen ekvivalent jedné instrukce, která se skládá ze zfúzovaných uOPů. Ty jsou pak rozděleny až později při vykonávání. Tento způsob šetří kapacitu uOP cache a zřejmě také fáze dispatch. Toto dost možná je schopné vykompenzovat zmenšení nominální kapacity uOP cache.

U uOP cache byla také zvýšená asociativita z 12cestné na 16cestnou.

Stále konzervativní hloubka Reorder Bufferu

AMD zvětšilo Reorder Buffer (RoB), tedy hlavní frontu, v které probíhá princip Out-of-Order vykonávání instrukcí a které tvoří „okno instrukcí“, v jehož rámci procesor může optimalizovat vykonání faktickým přeházením pořadí instrukcí. AMD mělo RoB vždy poměrně malý v porovnání s Intelem, nemluvě o srovnání s jádry Apple. Zen 3 měl RoB o 256 položkách jako Skylake nebo E-Core Gracemont od Intelu, Zen 4 ho zvětšil na 320 položek, zatímco Intel Golden Cove už mělo 512. U Zenu 5 dojde k lehce odvážnějšímu zvětšení na 448 položek (+40 %), ale AMD je zde pořád konzervativnější než všichni jeho konkurenti (Apple, Intel i ARM).

Zen 5 je nyní někde mezi hloubkou RoB u jader Sunny Cove/Ice Lake (352) a Golden Cove od Intelu, ale evidentně s touto nižší hloubkou dokáže vyvinout jádro s výrazně větším výkonem na 1 MHz, než na ní založil Intel. Asi to ale zapadá do filozofie „rovnováhy“ mezi výkonem a efektivitou, která byla pro Zen na začátku uváděna jako vodítko.

Kolik stupňů má pipeline Zenu 5?

AMD přímo neprozrazuje, kolikastupňová je pipeline procesoru, což ale nebylo uváděno ani u předchozích jader linie Zen. Toto tedy bude nutné zjistit nepřímo pomocí mikrobenchmarků.

Pravděpodobně ale došlo k prodloužení pipeline o jeden stupeň, který byl někde přidán, protože AMD řeklo, že postih za špatně odhadnuté větvení, který je nepřímo indikátorem počtu stupňů v pipeline, by kvůli změnám v jádru měl obvykle být o jeden cyklus větší.

Článek pokračuje na další straně.

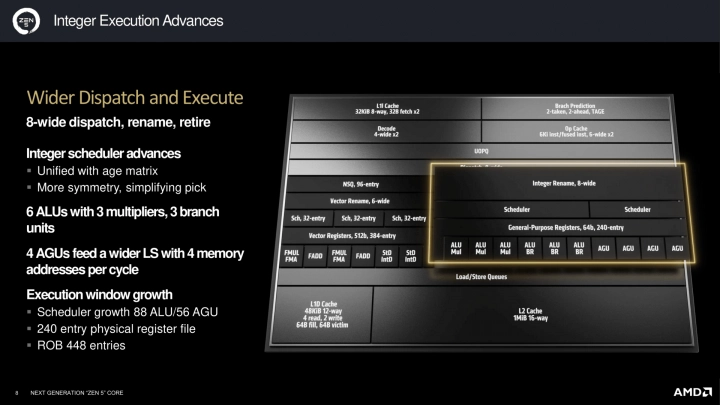

Víc ALU, silnější backend, spojený ALU scheduler

Jak už dříve uniklo, Zen 5 poprvé od prvního Zenu 4 přidává jednotky ALU, těch je nyní šest místo dosavadních jen čtyř. Stejných šest má nové jádro Intelu, Lion Cove, ale ARM nebo Apple už jsou na 9–10 (nicméně u stoupajícího množství jednotek platí zákon klesajícího užitku). Jádro Zen 5 tedy může v jednom cyklu zvládnout až šest běžných aritmeticko-logických instrukcí.

Pro některé operace ale může být nárůst prostředků ještě větší. V předchozích jádrech totiž tři ze čtyř jednotek ALU byly jednoduché, takže neuměly složitější operace jako násobení, které zvládala jen jedna „komplexní“ ALU. Obě nově přidané ALU v Zenu 5 jsou zřejmě komplexní, toto nové jádro totiž už umí provádět tři celočíselná násobení za takt. AMD také zvýšilo počet jednotek pro větvení, ty jsou tři místo dvou (přítomné patrně na portech jednoduchých jednotek ALU). Lze tedy zpracovat až tři skoky či větvení za cyklus.

AMD zvýšilo počet registrů ve fyzickém souboru obecných registrů (pro operace ALU) na 240, což je mírné zvětšení z 224 v Zenu 4. Větší zvýšení je u SIMD (FPU) registrů, kde měl Zen 4 jen 192 registrů, ale Zen 5 rovnou 384. Tyto registry se používají pro přejmenování architektonických registrů (které vidí běžící program) při out-of-order a paralelním zpracování instrukcí, kde víc registrů dává větší možnosti.

AMD také dělalo změny ve schedulerech, ze kterých jsou do jednotek sypány instrukce. Zatímco Zen 3 a 4 používal čtyři oddělené schedulery po 24 položkách – jeden pro každou ALU (a k těmto ALU přidružené jednotky AGU nebo jednotky pro větvení), Zen 5 má místo toho unifikovaný scheduler pro všech šest jednotek ALU (a jednotek pro větvení), jenž má hloubku 88 položek a druhý unifikovaný scheduler pro všechny jednotky AGU (unifikovaný scheduler pro AGU měl předtím Zen 2) o hloubce 56 položek. Toto má umožňovat pružnější přidělování operací jednotkám ALU, což při jejich zvýšeném počtu začalo být podle Mike Clarka už důležitější než v předchozích jádrech se čtyřmi ALU. Scheduler Zenu 5 by údajně měl být celkově efektivnější při daném počtu položek.

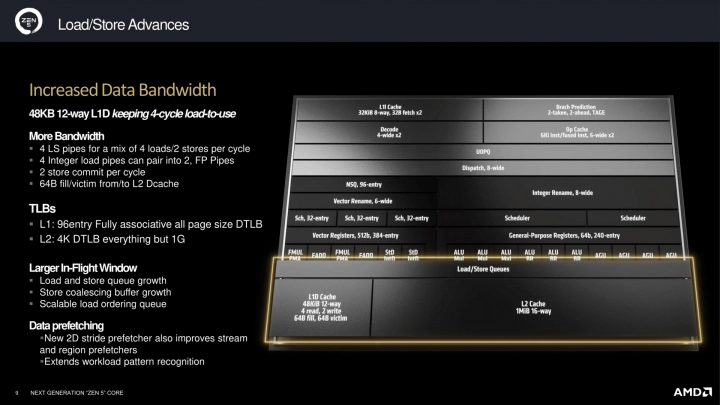

Jednotky AGU a tím load/store pipeline jsou čtyři oproti třem v Zenu 4. Jádro dokáže provést až čtyři čtení z paměti (respektive z L1 datové cache) do registrů za cyklus. Zápisy lze provést dva za cyklus a celkově u kombinace zápisů a čtení lze vždy provést maximálně čtyři.

Článek pokračuje na další straně.

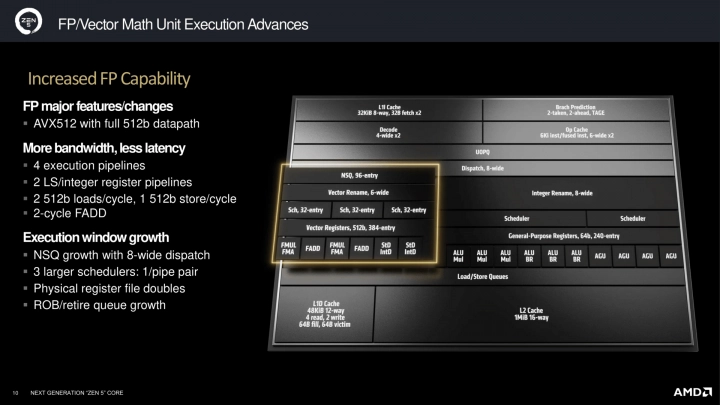

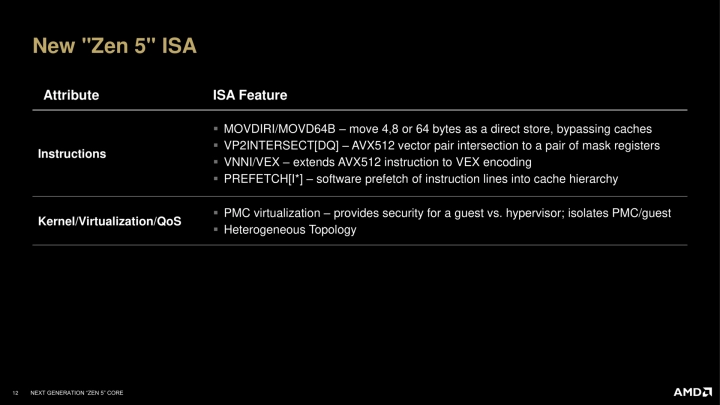

FPU: Nejsilnější SIMD na trhu a doteď nejlepší implementace AVX-512

Nicméně, toto platí pro čtení a zápisy do základní aritmeticko-logické části. Jednotka FPU a SIMD, která má své vlastní registry, je poněkud vydělená (toto „koprocesorové“ řešení teď už v novém jádru Lion Cove používá i Intel, který měl dlouho ALU a FPU unifikovanou) a má schopnost provádět jen dvě čtení či dva zápisy. U čtení jsou podporována až dvě 512bitová čtení (přičemž 512 bitů je šířka registru instrukcí AVX-512), protože datové šířky cest do L1 datové cache byly zdvojnásobené. Zápisy lze provést dva 256bitové nebo 128bitové za cyklus, nebo jeden 512bitový za cyklus.

Toto rozšíření a tím zdvojnásobení datové propustnosti mezi jádrem a L1 cache je samozřejmě uděláno proto, že AMD u Zenu 5 upgradovalo pipeline v jednotce SIMD/FPU. Ty byly od Zenu 2 až po Zen 4 s šířkou 256 bitů, takže uměly provést jednu instrukci AVX nebo AVX2 jedním průchodem, ale Zen 4, který už uměl i AVX-512 s 512bitovou šířkou, je musel počítat dvěma průchody. Zen 5 rozšířil jednotky na dvojnásobnou 512bitovou šířku. To znamená, že počet operací SSEx a AVX/AVX2 možných za cyklus se sice nezměnil, ale instrukcí AVX-512 může jádro provést dvojnásobek. Takže při využívání instrukcí AVX-512 v programech bude možné ze Zenu 5 dostat vyšší výkon.

Počet pipeline zřejmě zůstal stejný a je jich šest, nicméně ne všechny mají všechny schopnosti a část provádí instrukce jako load/store nebo konverze. Instrukcí FMA nebo floating-point násobení dokáže jádro provést dvě za cyklus (včetně 512bitových AVX-512), floating-point sčítání (FADD) lze udělat také dvě. Ovšem jednoduché celočíselné SIMD operace, jako je sčítání, jsou možné čtyři za cyklus. Změna k lepšímu je také, že instrukce FADD mají latenci dva cykly místo dřívějších tří.

Až šest operací za takt lze provést, pokud jde o kombinaci násobení/FMA, sčítání a load/store operací. Není to tedy tak, že by Zen 5 (a podobně Zen 4 před ním) měl šest pipeline, z nichž každá by byla „všehoschopná“.

Nicméně když se vezme v potaz to, že jádro u všech operací může zpracovávat 512bitový vektor, znamená to, že jádro Zen 5 by mělo mít nejvýkonnější SIMD ze všech konkurentů. Intel má (respektive bude mít) v jádru Lion Cove čtyři 256bitové pipeline (které tedy zvládnou jen polovinu výpočtů za cyklus), Apple má čtyři pipeline se 128bitovou šířkou (a tedy jen čtvrtinovým výpočetním výkonem) a ARM u jader Cortex-X925 sice má šest pipeline, které jsou univerzálnější, ale stále jen se 128bitovou šířkou.

Zen 5 by tedy měl být velmi atraktivní jádro pro úlohy silně využívající instrukce SIMD a také dost možná bude procesorem, který bude mít nejlepší schopnosti vykonávání instrukcí AVX-512 ze všech dosavad uvedených. Ovšem pozor: Toto bude patrně platit jen pro serverovou a pro desktopovou verzi, tedy Ryzeny 9000. AMD to sice oficiálně nepotvrdilo, ale zdá se, že mobilní procesory Ryzen AI 300 mají jádro upravené tak, že obsahuje v FPU menší počet SIMD pipeline – ty jsou sice stále 512bitové, ale v menším počtu, což výkon v takovém softwaru samozřejmě nějak omezí. Jak moc, to ukážou benchmarky po vydání.

Aktualizováno: Zdá se, že rozdíl mezi desktopovým (respektive serverovým) a mobilním jádrem Zen 5 nakonec nespočívá v počtu pipeline, ale v šířce jednotek. AMD uvádí, že jak jádro Zen 5, tak jádro Zen 5c implementované v APU Strix Point (Ryzenu AI 300) má fyzicky 256bitové jednotky AVX-512, tedy podobné Zenu 4, místo plně 512bitových, jaké mají jádra (Zen 5, ale i Zen 5c) pro desktop a servery.

Toto je umožněno tím, že Zen 5/Zen 5c ve skutečnosti podporuje konfigurovatelnou šířku SIMD jednotek. Šířka se dá zvolit při návrhu čipu. 512bitová šířka jednotek SIMD pro AVX-512 coby jedna z hlavních novinek Zenu 5 tedy platí jen pro některé procesory. I v 256-bitové implementaci je ale zůstává 512bitová šířka load-store datových cest do L1 cache, pouze samotné vykonávací jednotky mají poloviční šířku.

Ještě je třeba říct, že FPU/SIMD má vlastní scheduler, respektive schedulery. AMD u ní totiž dál používá tři rozdělené schedulery o 32 položkách (jeden pro dvojici pipeline), což je ale změna proti Zenu 4, kde byly schedulery jen dva (vždy pro trojici pipeline) také o 32 položkách, takže celková kapacita těchto front je o polovinu větší.

Zde tedy AMD šlo opačným směrem, údajně proto, že kód běžící na jednotce SIMD je mnohem více pravidelný, opakující se a předvídatelný proti chaotičtějšímu kódu, který musí chroustat aritmetickologická část, takže je snazší ho řešit v rozdělených schedulerech (ze stejného důvodu bylo také snazší zvětšit počet SIMD/FPU registrů o 100 %).

Před schedulery má jednotka FPU ale ještě předřazenou delší frontu NSQ (Non-Scheduling Queue). Ta se také prohloubila o 50 % z 64 na 96 položek. Tyto fronty, kterými instrukce prochází, pomáhají schovat latence instrukcí, a zejména latence, které by vznikaly čekáním na data, která mezitím mohou být přinesena do cache díky prefetchingu.

Článek pokračuje na další straně.

Paměťový subsystém a SMT

Výkonnější a konečně větší L1 cache

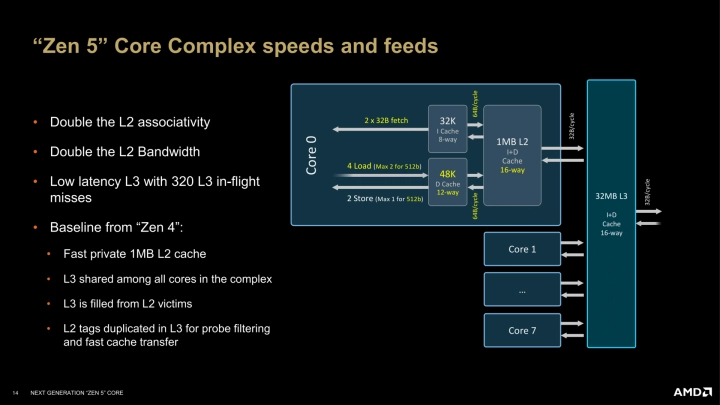

Další možná dost významné zlepšení je v L1 datové cache, což je kriticky důležitá mezipaměť, tvořící nejrychlejší a vykonávacím jednotkám nejblíže se nacházející prostor pro pracovní data programu (po registrech, jejichž kapacita je velmi omezená). Všechna dosavadní jádra linie Zen měla 32kB L1D cache, ale Zen 5 ji poprvé zvětšuje. A to na 48 kB, čímž se vyrovnává aktuálním velkým jádrům Intelu (ta mají 48kB L1 od Sunny Cove).

Není to sice tak velká kapacita jako 128kB L1 cache u procesorů Apple, ale zdá se, že u x86 procesorů používajících 4kB stránky je náročnější cache zvětšit (nebo to Intel a AMD z jiného důvodu nechtějí provádět). L1 cache je u Zenu 5 stále s latencí jen 4 cykly, což je velmi dobré vzhledem k dosahovaným frekvencím. Má 12cestnou asociativitu. Jak už bylo zmíněno dříve, datová šířka pro komunikaci je 512 bitů, a data lze tedy do cache ukládat (nebo z ní číst) po 64 bajtech. Tato datová šířka znamená, že datová propustnost mezi jádrem a jeho L1 cache se zdvojnásobila. Pokud někde uvidíte informaci o „dvakrát větší rychlosti“, je řeč právě o tomto navýšení propustnosti/šířky, ne o nějakém dalším zlepšení navíc.

L1 Data TLB má 96 položek s plnou asociativitou pro všechny velikosti stránek pro L1 Data TLB, a L2 data TLB má 4K položek s plnou asociativitou pro všechny velikosti stránek kromě 1GB stránek. L2 instrukční TLB se zvětšil čtyřnásobně na 2048 položek.

L2 cache zůstává na kapacitě 1 MB, ale vzhledem k tomu, že prošla upgradem v předchozí architektuře, to asi není na závadu. Ovšem zvýšila se její asociativita z 8cestné na 16cestnou, takže změny zde jsou. AMD také zdvojnásobilo (64B/cyklus) propustnost mezi L2 cache a L1 cache v souladu s tím, jak byla zdvojnásobena propustnost mezi load-store jednotkami a L1 cache.

L2 cache je privátní pro každé jádro, měla by mít latenci 14 cyklů. Zpětně vzato možná dává smysl, proč AMD zvětšilo cache právě v Zenu 4, ač ten byl jen méně radikální „evolucí“ Zenu 3 – patrně bylo cílem tento úkol vydělit a zvládnout dřív, než přijde řada na všechny velké změny v Zenu 5, aby pak nebylo ukousnuto příslovečné příliš velké sousto.

AMD také uvádí, že u Zenu 5 je vylepšený prefetching, což je opět jako u predikce větvení komplexní oblast kontinuálních optimalizací, v níž se provádějí úpravy a ladění v každé nové generaci, takže by bylo zvláštní, kdyby jádro vylepšený prefetching nemělo. Jde o důležitou složku IPC procesorů.

Zen 5 má nový 2D stride prefetcher a je schopen lépe rozpoznávat vzorce v přístupech do pamětí a předem podle nich nahrávat data, která program pravděpodobně bude v budoucnosti vyžadovat.

L3 cache se bude lišit v jednotlivých procesorech. Podle AMD je jedním z jejích vylepšení, že podporuje až 320 současných cache missů, tedy souběžně lze poptávat až 320 různých dat z paměti.

Statické versus dynamické dělení prostředků mezi vlákna při SMT

Mimochodem, zmiňovali jsme dříve SMT. Mike Clark v interview zmínil, jak jsou které části jádra dělené v případě, že jádro zapojí obě vlákna. Velká část má dynamické (competitive) dělení, kdy se alokace pro obě vlákna může měnit podle potřeby, byť obvykle část zdrojů je vždy vyhrazená, aby jedno vlákno nikdy nezkonzumovalo úplně všechny prostředky. Toto se týká cache, TLB a také samotných výpočetních jednotek (pipeline v SIMD jednotce nebo ALU).

Některé části jsou ale rozdělené staticky, tedy fixně půl na půl, pokud jádro zpracovává dvě vlákna. Platí to například pro RoB, kde je údajně extrémně těžké dynamické rozdělení implementovat, takže k tomu nebylo přikročeno. Další části se statickým rozpůlením zdrojů (tedy kapacity nebo například položek ve frontě) jsou store a retire fronty a také fronta micro-opů před fází dispatch. Nicméně v momentě, kdy druhé vlákno jádra přestane být používáno, jsou tyto prostředky opět plně přiřazené jedinému vláknu, SMT tedy nekazí výkon v jednovláknové zátěži.

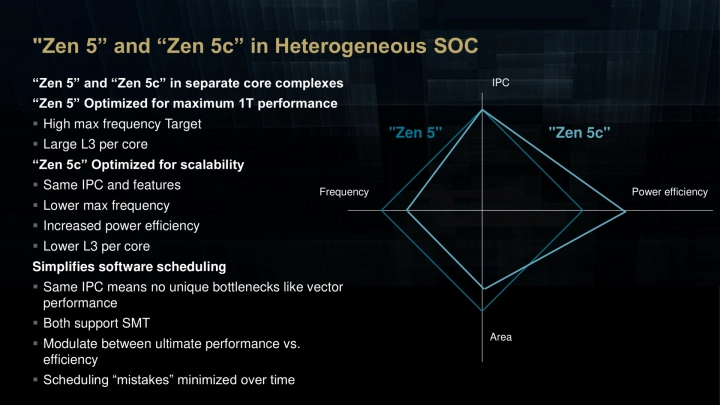

Zen 5 a Zen 5c

AMD opět od Zenu 5 vyvinulo také kompaktní verzi jádra označenou Zen 5c, jak už jsme zmiňovali, přičemž nyní byla uvedena současně se standardním jádrem v mobilních Ryzenech AI 300.

Stejně jako u Zenu 4c by efektivní jádra Zen 5c měla podle AMD mít stejné IPC (tedy stejný výkon na 1 MHz) jako velký Zen 5 a všechny instrukce a technologie velkých jader. Liší se jen optimalizacemi na menší zabranou plochu na čipu (například menším využitím speciálních logických maker, větším zhuštěním díky tomu, že je jádro rozdělené na méně bloků), které současně snižují jejich maximální takt.

Kompaktní jádro má mít zhruba o 25 % menší plochu, nicméně toto částečně vyplývá z návrhu čipu Strix Point a nemusí platit univerzálně. Zen 5c je obecně optimalizovaný pro škálovatelnost (zatímco velký či klasický zen 5 je optimalizován na maximální výkon v jednovláknové úloze) a nejde u něj jenom o zabranou plochu na čipu, ale i o energetickou efektivitu, která je u něj údajně vyšší než u velkého zenu 5 (jedním z faktorů, které k tomu přispívají, má být i samotná menší plocha, kdy jsou cesty signálu mezi bloky kratší).

Článek pokračuje na další straně.

Závěr: Veliký upgrade, možná podceňovaný?

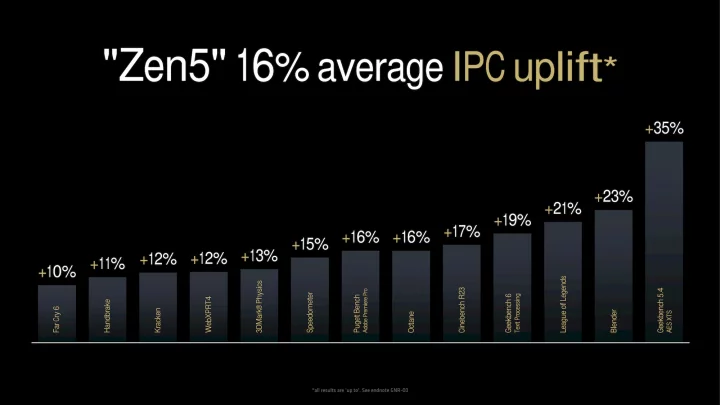

IPC zvýšené o 16 %

AMD již na Computexu v červnu uvádělo rámcový údaj o tom, jak moc se zlepšil výkon v přepočtu na jednotku frekvence, tedy tzv. IPC. Má to být o +16 %, což je hodnota zprůměrovaná z určitého výběru aplikací. Je třeba upozornit, že tato charakteristika se aplikaci od aplikace liší, takže „IPC“ nebo těchto „+16 %“ neberte jako nějakou pevnou vlastnost jádra Zen 5.

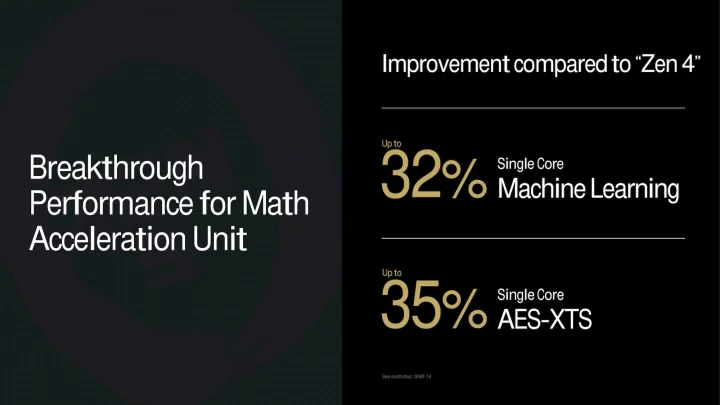

Nejvyšší zlepšení lze očekávat v úlohách, které dokážou využít onen 2× vyšší výpočetní výkon 512bitových instrukcí AVX-512, AMD uvádí jako příklad subtest AES-XTS v Geekbenchi 5.4 (+35 %) nebo nejmenované úlohy strojového učení (+32 %).

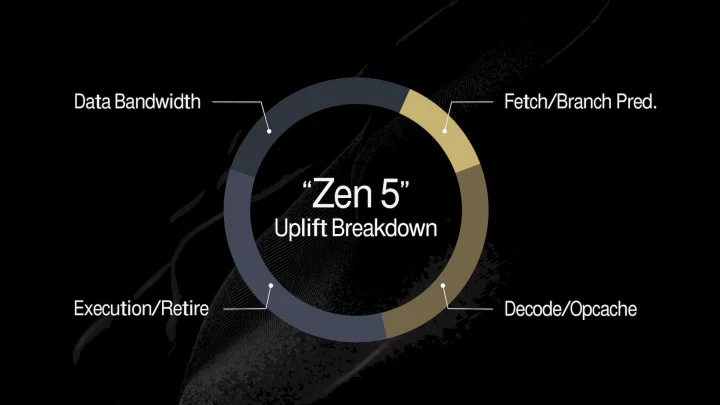

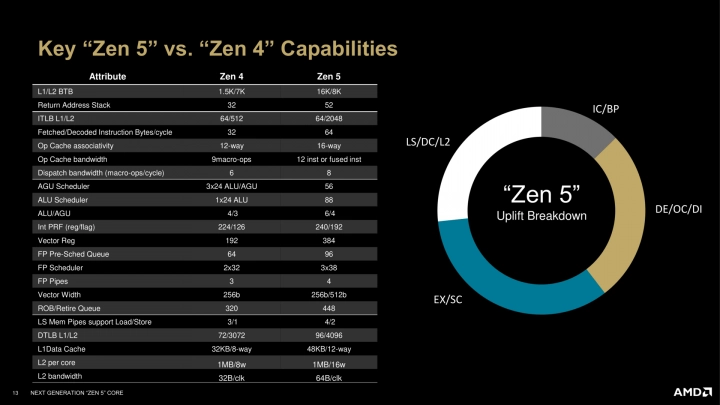

Odkud IPC fouká

AMD mimochodem ukázalo tento zajímavý graf, který reprezentuje, jakou měrou se zhruba na výsledném 16% zlepšení IPC podílejí různé popisované změny v jádru. Největší dopad mají podle všeho přidané jednotky ALU a ono rozšíření jednotek SIMD (které se pod toto patrně také počítá), což je v grafu světlejší šedá.

Hned v závěsu je pak nové řešení dekodérů s dvěma klastry a související přepracování uOP cache (tmavší okrová). Ta má sice zmenšenou kapacitu, ale její schopnost dodávat až 12 instrukcí za cyklus (a také ze dvou míst v kódu současně pro potřeby dvou klastrů dekodérů) evidentně má slušný přínos pro výkon. Poznámka: Je možné, že toto ovšem reprezentuje mnohovláknové aplikace, nejen jednovláknové.

Hodně velkou (prakticky stejnou?) roli, zdá se, hraje ono zvýšení datové propustnosti L1 cache na dvojnásobek (tmavá šedá), což je trochu překvapivé. Z toho, jak velký je přínos, se zdá, že se zdaleka neprojevuje jen v kódu vytěžujícím operace AVX-512 na jednotce SIMD, což je hlavní věc, která by vás napadla. Až čtvrtý v řadě (světlý okr) je vliv vylepšené predikce větvení a fetche, nicméně je to stále vliv docela velký.

Opravdu největší změna v jádru od prvního Zenu? Rozhodně

Jak jste mohli vidět, rozsah změn v jádru jde opravdu daleko. Přičemž třeba ony šachy ve schedulerech ALU a FPU ukazují, že inženýři sahali i na věci, které nejsou tak zřejmé jako to, že se konečně navýšil počet ALU o 50 % nebo výpočetní výkon SIMD instrukcí (a datová propustnost cache) o 100 %.

Ono překopání frontendu (dekodérů a souvisejícího napojení na instrukční cache a fetch) je nakonec možná nejdalekosáhlejší věc v Zenu 5, protože vývoj v této části patrně bude pokračovat do dalších generací a jde asi o největší koncepční změnu v jádru, jakou jsme od Zenu 1 viděli (fanoušci Intelu mohou být hrdí, že poprvé se objevila v jeho jádru Tremont, nicméně nápad může být starší).

Rozhodně se nedá mluvit o tom, že je Zen 5 nějaký „refresh“ (i to se člověk na internetu dočte mezi nepřebernými názory…), technicky je to nejen nová, ale rozhodně i „hodně nová“ architektura.

Proč je tedy nárůst IPC jenom takový, jaký je, ptáte se možná. Je ale otázka, jestli je udávané číslo opravdu málo, což se patrně hodně lidem zdá. Jak jsme psali na začátku, někdy možná byla priorita hlavně dosáhnout oněch „milníků“, jako jsou širší datové cesty, víc ALU a přepracovaný frontend než vymáčknout z nich hned maximum. To se ostatně děje málokdy, stačí poukázat na to, jak relativně nízko začínalo IPC jádra Zen 1 a kam až se dostal Zen 4 stále s oním stejným základem o čtyřech ALU.

Také zde pravděpodobně budou další výkonnostní skoky pokračovat v následujících generacích a podle architekta Mika Clarka budou jich zlepšení částečně představovat něco, co bylo uděláno už teď v Zenu 5.

Nárůsty IPC se dost možná budou pořád snižovat

I mimo to je ale třeba poukázat na to, že zvyšování výkonu na 1 MHz není u jádra CPU něco, co jde dělat donekonečna stejným tempem, jako je třeba rozšiřování GPU na více a více bloků a shaderů – GPU zpracovávají vysoce paralelní úlohy, a tudíž stále mohou takto snadno škálovat. Zvyšování výkonu na 1 MHz frekvence je ale něco, kde se téměř určitě uplatňuje zákon klesajícího užitku, a pokud jste na špičce, je další pokrok čím dál těžší. Pravděpodobně totéž je důvod, proč konkurenční Intel u svého velkého upgradu jádra CPU také uvádí „jen“ podobné zlepšení IPC (architektura Lion Cove slibuje +14 %, nicméně nesrovnávejte toto číslo se Zenem 5, je měřeno jiným způsobem na jiných aplikacích, takže Lion Cove nemusí mít ve skutečnosti menší nárůst IPC než Zen 5).

Je pravda, že absolutní IPC jader Apple je stále o dost vyšší, ale ta zase stále dosahují výrazně nižších frekvencí a obě věci spolu souvisí. S návrhem mířícím na vyšší frekvenci by vývoj jader Apple dospěl k nižším IPC a s návrhem pro nižší frekvenci by jádra AMD měla IPC lepší. Budoucí vývoj bude pravděpodobně takový, že se jak frekvence, tak IPC u obou konkurentů přiblíží.

Zákon klesajícího užitku, respektive to, že další zvyšování IPC je čím dál těžší, je ostatně patrné i u Applu. Ač je tato firma považována právem za „krále“ v oboru procesorů s vysokým IPC, pokud se podíváte na jeho inkrementální nárůst v poslední době, také je zde výrazné zpomalení. Měření se mezi sebou různě liší, ale vypadá to, že od procesorů M1 z roku 2020 narostlo IPC jader Apple jen o cca desetinu, pokud srovnáváme s nyní aktuálním procesorem M4 (mnohem více výkonu bylo získáno zvyšováním taktů). A to přesto, že jak procesory M3, které se patrně opozdily o víc než rok proti původním plánům, tak procesor M4 mají novou architekturu jádra (což se u M4 ze začátku moc nezdálo). A tak ono 10% zlepšení IPC dělají tyto dvě nové architektury dohromady.

Zatím nevíme jistě, zda třeba nejde o dočasné zpomalení a nové techniky a přístupy třeba v budoucích architekturách zase nepřinesou (na čas…) větší generační pokroky. Ale je dost pravděpodobné, že význam těch 16 % u Zenu 5 (a totéž u Lion Cove od Intelu) teď možná trochu podceňujeme. Je tedy pravda, že zatím ještě čekáme na nezávislé testy, které toto číslo ověří nebo trochu přehodnotí, ale obecně vzato by nešlo o špatný pokrok.

Zdroje: Chips and Cheese, AnandTech, HardwareLuxx