Je to hrůza, jak rychle čas ubíhá, ale už jsou to dva roky, co jsme v květnu 2017 informovali o budoucích plánech Samsungu s tranzistory typu GAAFET či také MBCFET. Ty firma připravovala coby náhradu za nyní používané 3D tranzistory typu FinFET (ve své době samy o sobě celkem revoluční). Teď po dvou letech Samsung hlásí výsledky a svůj plán vývoje křemíkové technologie až po 3 nm proces.

Samsung nejprve oznámil, že v druhé polovině letošního roku začne masovou výrobu na 6nm procesu. Ve stejnou dobu bude dokončen návrh 5nm procesu, který se podle Samsungu dostane do masové výroby v první polovině roku 2020. Do konce letošního roku také má skončit vývoj připravující následný 4nm proces. Až po 4 nm ovšem nastoupí skutečně velká novinka, a to 3nm procesu, neboli 3GAE. Ten totiž nebude jen další číslo v řadě, ale přinese velkou změnu, která by mohla být minimálně trochu podobná revoluci při nasazení prvních 3D tranzistorů, FinFETů.

Od planárních tranzistorů přes FinFETy opět k potřebě nové generace tranzistoru

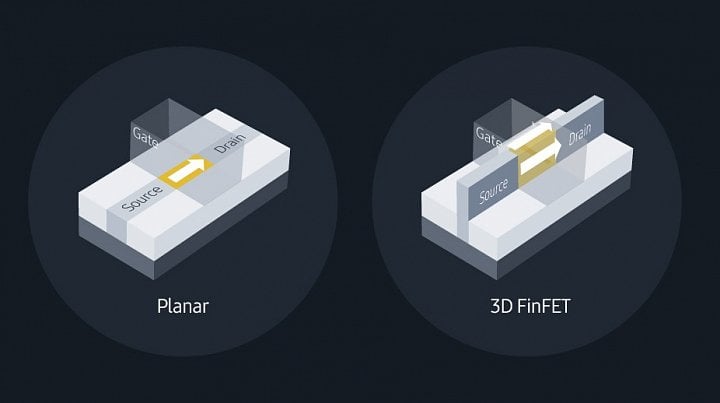

Pro kontext nejdřív malý exkurz. Klasický „planární tranzistor“ byl tvořený v rovině. V křemíku je se nachází cesta z polovodiče tvořící kanál (channel) a na něj je uložena brána (gate), jejíž úlohou je otevírat či zavírat kanál pro elektrický proud, čímž se rozlišuje zapnutý a vypnutý logický stav. Na starších výrobních procesech stačilo, aby brána takto seděla nad kanálem, aby její efekt kanál zavřel. Jenže její schopnost kanál uřídit se zhoršuje se zmenšováním tranzistoru. Po zkrácení kanálu pod určitou délku ztrácí planární tranzistor funkčnost, kanál je moc krátký na to, aby ho brána nad ním dokázala uzavřít.

Proto byly vyvinuty tranzistory FinFet (první je měl na 22nm procesu Intel, pod vlastním označením Tri-Gate). Jsou tvořené vertikálním (a poměrně vysokým) z plochy křemíku vystupujícím kanálem, jenž díky tomu je ze tří stran – ze stran a ještě zeshora – obklopen bránou, která ho zavírá nebo otevírá a přepíná tak logický stav. Díky tomu je tranzistor účinnější, výkonnější a úspornější než klasický planární tranzistor.

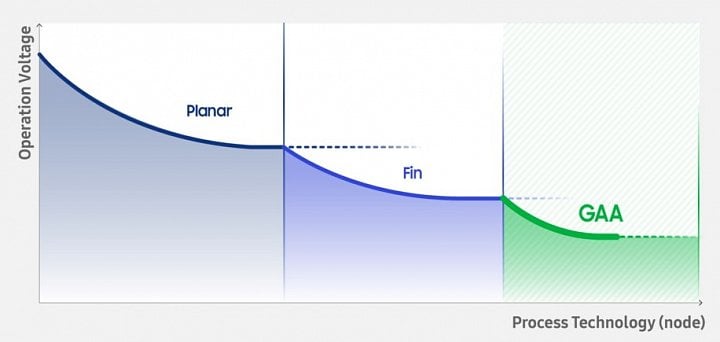

Zlepšení, která přinesl FinFET, ale umožnila zmenšit výrobní proces pod hranici 20 nm – na 14/16, pak 10 a nejnověji 7 nm. Ovšem jak se proces pořád zmenšuje, už i tato efektivnější struktura přestává stačit. Tranzistor se zmenšuje tolik, že ani brána ze tří stran ho obklopující kanál není schopná zajistit pořádné zavření kanálu. Tranzistor tak není schopen pořádně přepnout z jedničky na nulu.

GAAFET přijdou na 3nm procesu 3GAE

A proto je třeba, aby na místo FinFETu nastoupila zase o něco vylepšená struktura tranzistoru. Jak jsme psali už před dvěma lety, touto strukturou má být GAAFET. GAA znamená Gate All Around, tedy tranzistor, kde je kanál obklopený bránou ze všech stran. A díky tomu se zase o něco zvýší účinek, který je schopna na kanál vyvinout, a tím schopnost odlišit zapnutý a vypnutý logický stav. GAAFET díky tomu má být možné zmenšit na ještě drobnější rozměr než FinFET, aniž by ztratil schopnost fungovat.

GAAFETy mají škálovat na nižší výrobní procesy, větší efektivitu a vyšší výkon. Na nižších výrobních procesech už FinFETy přestávají stačit

GAAFETy mají škálovat na nižší výrobní procesy, větší efektivitu a vyšší výkon. Na nižších výrobních procesech už FinFETy přestávají stačitSamsung se nyní pochlubil tím, že opravdu úspěšně vyvinul verzi tranzistorů GAAFET nazvanou MBCFET (Multi-Bridge Channel FET), kterou avizoval před oněmi dvěma lety. A jako údajně jediná firma na světě má v tuto chvíli naplánováno jejich nasazení do výroby. Dříve firma říkala, že by tato novinka mohla být nasazena na 4nm procesu, nyní se ale zřejmě nástup plánuje na 3nm procesu Samsungu. Ten se podle toho bude jmenovat 3GAE a Samsung teď oznámil, že jeho vývoj momentálně jede podle plánu a je na cestě. Jen termín, kdy se dostane do výroby, ještě bohužel není ochoten říct (logicky to bude až po 4nm procesu, takže dejme tomu okolo roku 2022).

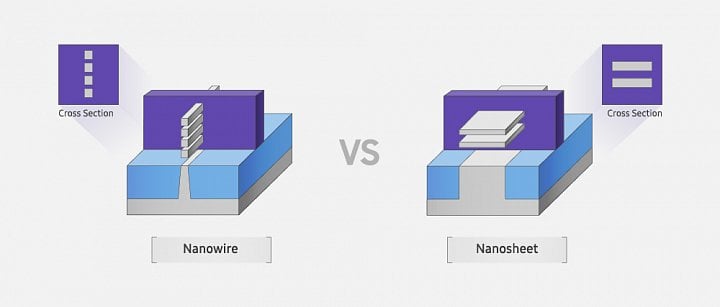

Tranzistory GAAFET jsou vlastně podobné FinFETům, můžete si je představit jako FinFET, kde brána obklopuje i zbývající stranu kanálu, které doteď „ležela na podlaze“. Dosaženo je to tak, že brána tvoří souvislý blok, skrze něž je vedený úzký kanál dírou. Tomuto útvaru se říká „nanodrátek“ a obvykle jich asi bude přes bránu proraženo víc, aby zvládly větší proud – každý ale bude obklopen ze všech stran bránou. Myslím, že na obrázcích výše je to vidět pěkně názorně.

Samsung ovšem proti této koncepci vyvinul vlastní zlepšení. To označuje MBCFET a spočívá v tom, že místo nanodrátků se používají nanodestičky, které jsou stále tenké, ale mají podlouhlý průřez. I zde by vedle sebe mohlo být destiček víc v mikroskopickém (nanoskopickém?) štůsku, mezi nimi ale vždy bude hmota brány, takže všechny kanály budou obklopené ze všech stran. Díky nanodestičkám by MBCFET měl zvládat vyšší proudy než GAAFETy s nanodrátky. Mají být také snazší na výrobu, zatímco nanodrátky jsou podle Samsungu tak obtížné, že u nich problémy s náročností převažují nad přínosy.

45% zmenšení a 35 % lepší výkon – než 7 nm

Firma nyní poprvé poodhalila, jaké by měly MBCFETy přinést pokroky. 3Nm proces 3GAE s nimi má dosáhnout až 45% redukce plochy čipu a o 50 % lepší spotřebu proti 7nm technologii (což mimochodem implikuje, že zisky z 5nm technologie budou nižší, vypadá to, že Samsung čeká u budoucích generací klesající užitek). Případně může proces 3GAE umožnit o 35 % vyšší výkon. A pozor, technologie má prý být aplikovatelná od úsporných čipů po ty nejvýkonnější.

Už existují testovací čipy

Samsung uvádí, že se mu nyní podařilo vyrobit první testovací čipy s tranzistory MBCFET na procesu 3GAE – zatím jen v laboratoři a ne v regulérní výrobě, samozřejmě. Jde ale o důležitý průlom, ukazující, že by technologie měla být realizovatelná. Teď firma bude pokračovat ve zlepšování efektivity a výkonu těchto tranzistorů.

Samsung ale už v dubnu dodal svým zákazníkům první verzi knihoven a specifikací pro vývoj na tomto 3nm procesu – Proces Design Kit 0.1. To znamená, že agresivní polovodičové firmy už mohou začít s vývojem fyzické implementace na 3nm/3GAE procesu teď. Jak už bylo řečeno, Samsung je teď jediný, kdo GAAFETy přislíbil, ovšem ostatní hráči (TSMC, Intel) na nich pravděpodobně pracují také. Je možné také, že je nakonec do praxe dotáhnou ještě dřív, ale zatím ještě tyto společnosti asi nejsou ochotné na rozdíl od Samsungu jejich nasazení na konkrétní generaci výrobního procesu přislíbit.