Coby jádra používá Tile-Mx100 64bitové Cortexy-A53. Na čipu má kromě nich být celkem přes 40 MB cache (tento údaj ale kombinuje všechny L1, L2 a L3) a jeho paměťové řadiče budou umět obsloužit až 1 TB RAM typu DDR4 s ECC. Kromě toho by na čipu měla být integrovány řadiče PCI Express 3.0 a zejména rozhraní Ethernet a Interlaken, údajně s celkovou propustností přes 200 Gb/s.

Schéma procesoru EZChip Tile-Mx100

Jméno výrobce EZChip vám asi nic neříká, nicméně firmu Tilera byste asi znát mohli. Vyráběla právě takovéto mnohojádrové procesory – než ji v loni na podzim EZChip koupil. Tile-Mx100 tak není vlastně ničím jiným, než pokračováním produkce Tilery pod novou značkou, i když součástí by měly být už i prvky vyvinuté EZChipem. Ostatně byl zachován i povědomý způsob značení. Procesor by měl tedy mít stejnou koncepci jako starší produkce Tilery, jen v něm byla jednoduchá jádra proprietární architektury, kterou si firma sama navrhla, nahrazeny standardními licencovanými ARMy. Čip by díky tomu mohl být výkonnější a efektivnější, ale také bude mít lepší softwarovou podporu. Výhodou může být také třeba přítomnost SIMD instrukcí Neon.

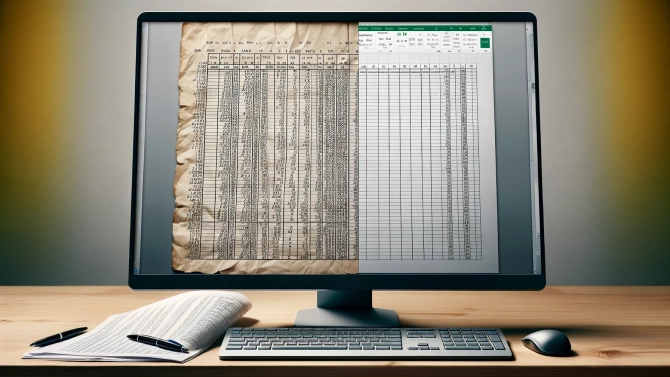

Procesorová jádra má čip Tile-Mx uspořádaná v síti typu mesh s koherentní propojovací logikou. Tato síť ovšem nepropojuje naráz všech sto jader. Ta jsou místo toho uspořádána v čtyřjádrových klastrech (v nichž se k tomu nacházejí ještě specializované akcelerátory) typických pro implementace vícejádrových Cortexů. Síť tím pádem propojuje jen dvacet pět uzlů v uspořádání 5 × 5. Vedle nejvyššího modely by jinak měly existovat ještě menší varianty s 64 a 36 jádry, u nichž bude zřejmě síť mít 4 × 4 či 3 × 3 uzly. TDP procesoru má dosahovat zhruba 70 W, což by pro stojádrový čip bylo docela dobré číslo, neboť v tomto případě bude mít značné energetické nároky i samotná propojovací logika a také IO.

Jednotlivé uzly jsou tvořené čtyřmi 64bitovými jádry Cortex-A53

Jediná skvrna na kráse je, že čipy Tile-Mx zatím ještě nejsou připravené k výrobě. Jejich příchod by měl nastat až někdy v roce 2017, během příštího roku by měly být k dispozici teprve vzorky. Čip má ještě být vyráběn na 28nm procesu TSMC (varianta HPM), zřejmě kvůli urychlení návrhu a startu výroby. Na menší výrobní procesy se Tile-Mx zřejmě přesune až poté, co se podaří dostat na trh tuto první verzi.

Až přijdou na trh, mají se procesory uplatnit hlavně v programovatelných síťových prvcích jako jsou switche, routery, ale i přímo síťové adaptéry. V těch mohou Tile-Mx sloužit k akceleraci nejrůznějších operací, například pro inspekci packetů. Částečně tedy tyto čipy nebudou přímo konkurencí konvenčních serverových CPU, ale jejich doplňkem.

Zdroje: EZChip, EE Times, CNX Software