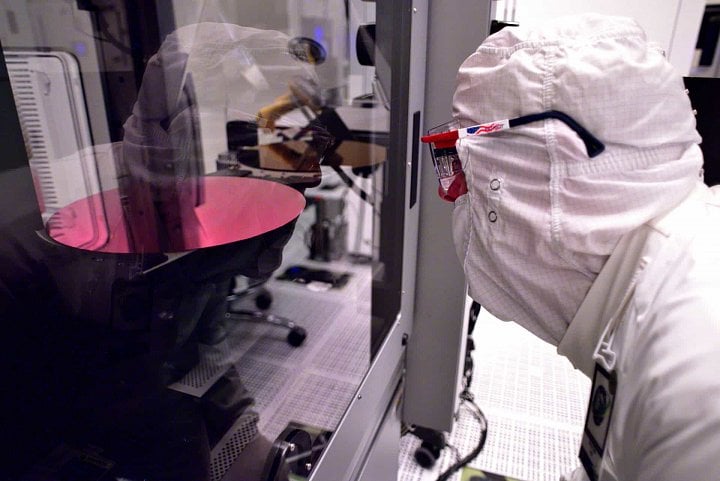

TSMC bylo už předtím jedničkou ve vývoji výrobních procesů i výrobě čipů pro firmy, které nemají jako Intelu své vlastní továrny a po odchodu GlobalFoundries ze scény bude ještě víc důležité. V jeho továrnách budou vedle GPU a čipů ARM ostatně od příští generace vyráběné i procesory AMD, přímo konkurující dominantnímu Intelu. Proto nás nutně hodně zajímá, jak se TSMC daří ve vývoji budoucích technologií jako například výrobě s EUV. A právě o tom nyní mámě nějaké nové informace. První se týká nasazení výroby s použitím EUV. Tato zkratka znamená extrémní ultrafialové záření vlnovou délkou okolo 13,5 nm. To je použito pro optické „kreslení“ struktur na křemík při optické litografii. Pro ni se dosud používá „hluboké UV záření“ o vlnové délce 193nm. To však dospívá na hranici svých možností. Pro vytvoření dostatečně malých struktur potřebuje přílišné množství opakovaných částečných expozic, což velmi prodražuje výrobu a také asi zhoršuje výtěžnost. Je možné, že i problémy Intelu s 10nm procesem jsou způsobené tím, že při něm ještě nepoužívá EUV.

První tapeout na EUV

TSMC na 7nm procesu také ještě EUV nepoužívá, tato technologie ale má být postupně zavedena ve druhé vylepšené generaci 7nm technologie nazvané CLN7FF+ či také N7+. EUV je problematická technologie a do praxe se teď (snad) blíží po mnoha a mnoha odkladech a zdrženích. Je proto dobrá zpráva, že se TSMC podařilo dosáhnout důležitého milníku na této cestě. Firma oznámila, že na procesu s EUV (tedy asi právě N7+) se podařilo jednomu ze zákazníků provést tape-out prvního čipu. Tape-out je fáze, kdy jde dokončen vývoj produktu a hotový návrh byl „odvezen do továrny“ k výrobě. Po této fázi začíná příprava jeho masové výroby, a typicky trvá asi 9–15 měsíců, než se čip dostane na trh.

Máme tu tedy signál, že za rok a něco (dejme tomu na přelomu let 2019 a 2020) by teoreticky mohly čipy s technologií EVU začít přicházet na trh. Ovšem v tomto případě to asi může trvat i déle. U EUV totiž mohou být ze začátku potíže s výtěžností nebo kapacitou výroby, takže komerční produkce může být pozdržena.

Zatím hlavně na průzkum bojem

TSMC nicméně EUV bude aplikovat hodně opatrně. V první generaci (tedy procesu N7+) se na něj ještě nebude plně spoléhat. EUV se použije jen pro maximálně čtyři méně důležité vrstvy (patrně je řeč o vrstvách kovových spojů). To je proto, aby případné problémy nezhatily nasazení celého procesu. Cílem je asi hlavně vše vyzkoušet v ostré výrobě a odladit. Pokud by se vyskytly problémy, asi by u těchto vrstev bylo proveditelné nahradit EUV starou technologií. Pro osvit zářením EUV se použijí dva stroje Twinscan NXE od firmy ASML.

Podle TSMC má proces N7+ přes to, že EUV v něm nebude ještě hrát podstatnou úlohu, přinést určitá zlepšení. Technologie má díky zhuštění kovových vrstev prý dosáhnout až 20% zvýšení hustoty tranzistorů proti první generaci 7 nm, jež je zcela bez EUV. Spotřeba čipu při stejné frekvenci a komplexitě prý může být až o 6–12 % lepší. Není ale uvedeno, že by tento proces měl také zvedat výkon (dosažitelnou frekvenci), takže v tomto ohledu možná zůstane na stejné úrovni jako první generace 7 nm.

5nm čipy za dva roky?

Serióznější nasazení EUV poté přijde na 5nm procesu („N5“). TSMC nyní plánuje, že by v jeho případě EUV mělo na starosti expozici až 14 vrstev. Tento proces by údajně mohl začít být používán k testovací výrobě (tzv. „risk production“) už od dubna příštího roku. Risk production začíná dlouho předtím, než se technologie může použít ke komerční výrobě čipů, které se také dostanou na trh. Ale opět jde o důležitý milník, takže je důležité, až se ho podaří dosáhnout.

Pro informaci, risk production na 7nm procesu také začala v dubnu 2017, což nám dává šikovnou paralelu. Teprve teď se začínají 7nm čipy dostávat do oběhu v prvních highendových mobilech. Takže pokud to s 5 nm půjde stejně dobře, mohly by se 5nm čipy vyskytnout v mobilních procesorech firem jako Qualcomm, HiSilicon (Huawei) a Apple snad za dva roky.

Podle TSMC by 5nm proces měl přinést zvýšení výkonu/frekvencí o 14,7 % až 17,7 % – mělo by to být srovnání s první ne-EUV generací 7nm procesu. Také hustota tranzistorů má narůst, TSMC slibuje že 1,8 až 1,86násobně. Tato zlepšení jsou uváděna pro implementaci CPU jádra ARM Cortex-A72, nejde tedy o nějaké úplně syntetické hodnoty. Design čipů pro 5nm proces N5 už podle firmy může nyní začít, i když potřebné knihovny dosáhnou verze 0.9 až v listopadu. A ne všechny bloky jsou pro ně také přichystané („polotovarové“ implementace PCI Expressu 4.0 nebo USB 3.1 nabízené vývojářům čipů například ještě chybí a mohou být přichystané pro integraci až v červnu).

Náklady na vývoj stoupají, malé ryby mohou zůstat na suchu

Bohužel také platí, že pro firmy vyvíjející procesory či jiné integrované obvody bude čím dál těžší 5nm proces použít. Celkové náklady na navržení jednoho takového čipu mají prý být až brutálních 200–250 milionů dolarů, kdežto u 7nm čipu vám teď „stačí“ 150 milionů. A to jde o jediný čip, při potřebě více variant například u CPU a GPU tedy vypláznete násobky (to se pak člověk nemůže divit, že třeba AMD navrhuje čím dál nižší počty GPU).

Aby si tedy nějaká firma mohla dovolit vůbec 5nm proces použít, bude potřebovat prodat o hodně větší počet čipů, aby se v něm tyto náklady rozprostřely. Nebo bude muset zdražit, pokud nemá produkt dostatečně masový/úspěšný. Laťka se tedy pro všechny firmy používající nejmodernější procesy bude dále zvyšovat a menší hráči už možná nebudou schopní vývoj 5nm čipů ufinancovat. To nebude moc dobré pro nás zákazníky, protože největší a nejbohatší firmy budou čím dál méně ohrožovány menšími konkurenty.