TSMC se trošku opozdil 3nm výrobní proces. Sice ne dramaticky, ale firma s hotovými čipy kvůli dlouhé době, kterou absolvování všech fází zpracování zabere, nestihne dodat první hotové čipy v roce 2022, ale až v roce 2023. Teď ovšem tchajwanský podnik, který má dnes zřejmě ze všech soutěžících nejpokročilejší výrobní technologie, představil vylepšený proces, který by mohl vakuum ve výrobních technologiích zmírnit: technologii N4P.

4nm proces 2. generace: lepší výkon/spotřeba, plocha i cena

Proces N4P je označovaný jako 4nm, přičemž půjde o druhou, vylepšenou generaci 4nm technologie po prvotní inkarnaci N4. Tento 4nm proces není ale svébytnou generací jako byl 7nm nebo 5nm proces a jakou bude proces 3nm. Jde ve skutečnosti spíše vylepšenou evoluci EUV 5nm technologie, která má zlepšit parametry výsledných čipů. Ale údajně by mohla přinášet i jisté finanční úspory, tyto čipy by mohly údajně být trošku levnější než velmi drahé 5nm čipy.

TSMC uvádí, že se má zlepšit dosažitelný výkon. Proti prvnímu 4nm procesu má N4P dosahovat až o 6 % lepší výkon, a pokud by se to dalo dohromady se zlepšeními, která přinese proces N4, mají čipy s technologií N4P mít potenciál k až o 11 % lepšímu výkonu (frekvenci) než čipy vyrobené první generací 5nm procesu (N5).

Alternativně by proces N4P mohl dosahovat až o 22 % lepší energetickou efektivitu proti technologii N5, pokud čip poběží na stejných taktech. Jako obvykle nebude možné si oba tyto benefity vybrat najednou a je pravděpodobné, že ona redukce spotřeby bude platit pro nějaké nižší takty, ne ty úplně maximální.

Co by se naopak mohlo kumulovat se zlepšením výkonu (nebo spotřeby), je zlepšení hustoty tranzistorů. Proces N4P má umožnit určité malé inkrementální zahuštění a tím zmenšení čipů, má být údajně možné vylepšit hustotu tranzistorů až o 6 % – proti hustotě tranzistorů dosažené procesem N5.

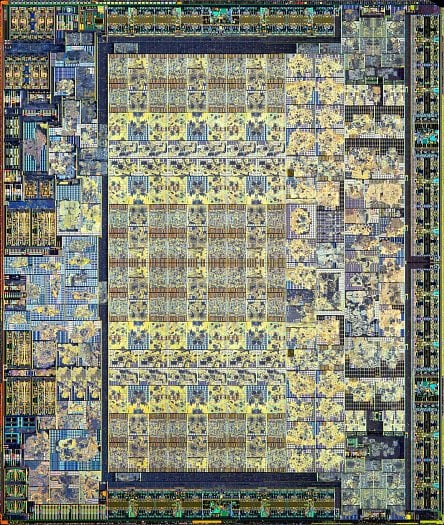

Galerie: 7nm čip vyráběný procesem TSMC, AMD Navi 14 (fotogalerie)

Zhuštění může přinést určité zlevnění výroby, pokud se inženýrům podaří navrhovaný čip díky tomu zmenšit. Technologie N4P má ale přinést úspory i mimo to, což budou zejména menší firmy s menšími maržemi potřebovat, protože finanční nároky na použití nejnovějších technologií pořád strmě rostou (jak se dramaticky zhoršují ceny za jeden wafer, jsme probírali zde). Proces N4P má přinášet určitou dílčí úlevu, protože proti procesu N5 má být o něco méně komplexní. Má totiž o něco méně masek, což znamená úsporu fixních jednorázových investic potřebných pro rozjezd výroby (ale tak třeba opravné revize) a asi také variabilních nákladů. Wafer bude vyžadovat méně výrobních kroků, stráví tak v továrně kratší čas, a TSMC by si tak asi mohlo účtovat o něco menší částku (nejspíš ale pořád vyšší, než za 7nm/6nm výrobu).

Migrace na tuto technologii má být relativně snadná u návrhů, která byly vytvořeny pro 5nm proces, pravidla by měla být poměrně podobná, takže přeportování nějakého návrhu by mělo být usnadněno.

Paralelní levnější technologie doplňující 3nm proces

Proces N4P nebude ovšem náplastí na opoždění procesu N3. TSMC totiž uvádí, že první tape-outy čipů, které zákazníci na této technologii budou vyrábět, očekává až v druhé polovině roku 2022 (a obecné pravidlo říká, že reálné uvedení čipu nastává nejdříve 9–15 měsíců po tape-outu). Křemík vyráběný tímto procesem tak bude dostupný na trhu asi až později, než křemík 3nm. Návrhy čipů pro tuto technologii také asi začaly relativně později.

Proces N4P je asi třeba vnímat jako určitou levnější a o něco horší náhražku za N4P pro takové klienty, kteří potřebují ekonomičtější řešení. Není to tedy technologie, která by měla za cíl dočasně zaplnit prázdné místo před tím, než bude hotový 3nm proces. Obě technologie budou v budoucnosti koexistovat a plnit odlišné role v portfoliu TSMC (a v arzenálu zbraní výrobců procesorů, GPU, mobilních SoC a dalších polovodičových produktů).

Například v mobilních telefonech lze čekat, že 3nm budou procesory pro vlajkové lodě a highendové modely, kdežto procesy N4 a N4P se objeví v telefonech střední třídy – ovšem třeba až o rok později, než kdy dostanou drahé mobily své 3nm čipy, protože highend naskakuje na nejnovější technologii hodně rychle, kdežto v levnějších sférách je postup pomalejší.

Zdroj: TSMC