Výrobci řadičů mají zatím jen stavební bloky

Na Computexu 2018 a krátce předtím se teď objevily demonstrace technologie USB 3.2, ale jsou v podstatně ranějším stádiu, něž se asi (naivně?) čekalo. Zatím totiž šlo jen o demonstraci prototypů nebo návrhů samotných PHY – tedy obvodů implementujících fyzickou/elektrickou I/O vrstvu rozhraní. Nedošlo na demonstrace nebo prototypy samotných řadičů, nebo dokonce jejich oznámení. PHY pro USB 3.2 ukazovala firma Synopsys, která různé obvody a IP licencuje výrobcům čipů, a nyní také ASMedia na Computexu 2018.

Právě ASMedia byla zdaleka prvním výrobcem, který měl na trhu řadič USB 3.1 – desky s čipem ASM1142 se objevily už začátkem roku 2015. Pro srovnání: do čipových sad AMD se USB 3.1 dostalo v roce 2016/2017 a v Intelech je až letos (čipsety B360, H370, Q370). Tudíž se asi trochu čekalo, že by právě tato tchajwanská firma mohla mít řadič USB 3.2 rychle. USB 3.2 by totiž mělo používat stejnou rychlost fyzické komunikace po kabelu, ale zdvojnásobit počet linek, kterými půjde. Teoreticky se tedy zdálo, že by nemělo být těžké zdvojit příslušné bloky v existujících návrzích pro USB 3.1 a uvést nové řadiče. V praxi se ale zdá, že tak snadné to nebude a příslušná PHY tvořící signál mají firmy teprv nyní.

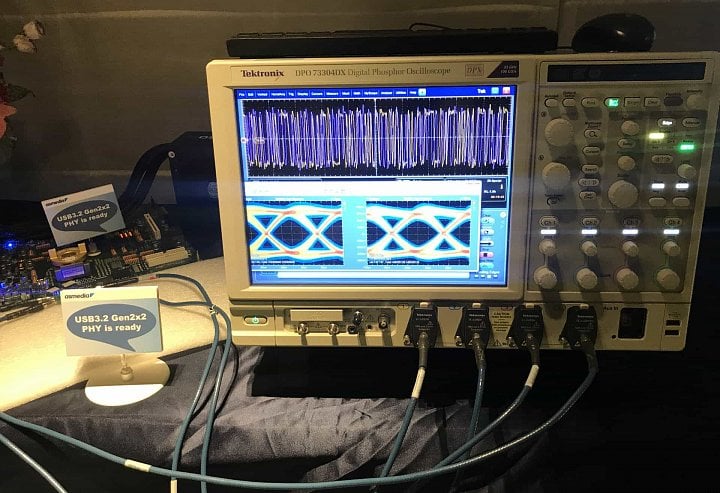

Demonstrace Synopsys byla ukázána už na konci května a už naznačovala, že je nástup technologie v raném stádiu. PHY s dvěma 10Gb/s linkami dávajícími dohromady 10Gb/s USB 3.2 bylo implementováno pomocí FPGA. Ovšem protože Synopsys vyvíjí IP pro druhé, není to nic zvláštního. Ani u ASMedia ale bohužel nebylo k vidění víc, než jen zvláštní prototypovací deska. A jak už bylo zmíněno, na stole zatím není konkrétní řadič, ale opět jen PHY, nad nimiž eventuálně bude postaven.

Podle osciloskopů připojených na port USB-C zřejmě předváděné PHY pracuje dobře a mohlo by tedy již být pro integrování do řadiče připraveno. Demo je označeno jako „USB 3.2 Gen 2x2“, což patrně označuje onu kombinaci dvou linek s rychlostí 10 Gb/s. Ty se totiž u USB 3.1 také označují jako „Gen 2“, zatímco původní 5Gb/s USB 3.0 bylo po uvedení portu typu C hodně zmatečně zpětně označeno jako „USB 3.1 Gen 1“.

V praxi se asi USB 3.2 objeví až v roce 2020

Co z toho tedy vyplývá pro horizont, v kterém by mohlo USB 3.2 reálně přijít na trh? Samotné řadiče budou pravděpodobně firmou ASMedia odhaleny až příští rok. To pravděpodobně znamená, že v roce 2019 se toto rozhraní nebude moci objevit v počítačích či noteboocích. Podle webu AnandTech, který stánek ASMedia s demonstrací na Computexu 2018 navštívil, se zřejmě na tuto technologii můžeme těšit spíš až v roce 2020. To se zdá jako realistický závěr. Pokud by se totiž řadiče objeví v roce 2019, bude jejich ověřování a integrace také chvíli trvat a desky s nimi se objeví až za několik dalších měsíců, což je pravděpodobně odsune až na ten rok 2020. Do té doby bude zřejmě muset 10 Gb/s USB 3.1 (případně Thunderbolt 3) pro potřeby náročných periférií stačit.