Tento procesor bude zřejmě na rozdíl od současného „lepeného“ čtyřjádra zvaného prostě Quadcore již nativním, monolitickým čtyřjádrem. Na trh by se údajně měl dopracovat někdy v polovině příštího roku. Vyrábět ho bude na 28nm procesu TSMC (současné procesory VIA pocházejí z 40nm linek). Uvidíme, co to udělá se spotřebou čipu, jelikož v tomto ohledu bude zřejmě příští rok docela horko (Haswell od Intelu zřejmě nasadí laťku v poměru výkonu a spotřeby hodně vysoko).

Relativně slibně ale vypadají frekvence, které by se údajně měly pohybovat mezi 1,2 a 2,0 GHz. To je na jednu stranu nárůst, na druhou stranu to však naznačuje, že architektura frekvenčním stropem zůstane někde na úrovni úsporných procesorů Bobcat a Atom. Nebude zřejmě s to škálovat na vyšší frekvence (a vyšší jednovláknový výkon). Novinkou v architekturách VIA bude vyrovnávací paměť třetí úrovně. L3 cache údajně měla mít až 4 MB, firma se však z ekonomických důvodů rozhodla pro omezení na 2 MB.

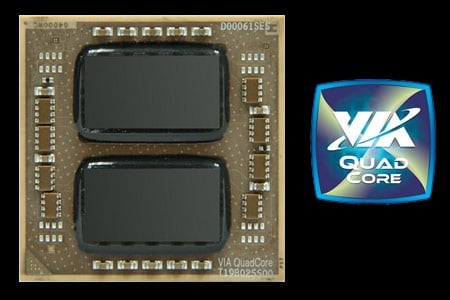

Snímek jádra Via Nano

Procesor si stále zachovává klasickou koncepci se sběrnicí FSB (kterou VIA nazývá V4 Bus) na efektivní frekvenci 133 MHz. Paměťový řadič tak bohužel stále zůstává v čipové sadě, pozitivem (alespoň pro firmu VIA) ale je, že čip tak stále zůstává kompatibilní s původní platformou. VIA údajně časem jak CPU, tak čipovou sadu integruje na jediný kus křemíku do čipu typu SoC. Eventuálně se tedy její procesor dočká integrovaného řadiče, byť tak trochu oklikou. Doufejme, že si na tom v Centauru dají práci a vyřeší komunikaci mezi součástmi skutečně moderně, aby bylo úzké hrdlo při práci s pamětí řádně eliminováno.

CN-R ale nese ještě jednu velmi překvapivou novotu. Údajně totiž bude podporovat instrukční rozšíření AVX2 (a potažmo zřejmě i předchozí AVX). Tím se VIA a Centaur dostávájí na technologickou špičku, zejména pokud čip nenabere zpoždění a skutečně vyjde jen pár měsíců po Haswellu. AVX2 bude mít do budoucna pravděpodobně stejně stěžejní význam jako dříve sada SSE2. Přinese totiž plnou podporu operací SIMD nad 256bitovými registry – jak pro práci s celočíselnými hodnotami, tak pro výpočty v plovoucí řádové čárce. Mimo jednotek SIMD se prý dočkají vylepšení i kryptografická rozšíření. Ta ostatně uvedla VIA do světa procesorů x86 jako první (VIA Padlock Security Engine).

Minimálně v multimediálním softwaru by se tak dal čekat nárůst výkonu na stejné frekvenci (uvidíme ale, zda ho CN-R neomezí tím, že bude instrukce AVX2 půlit a vykonávat postupně jako AMD). Jak naroste IPC procesoru v obecných úlohách, zatím nelze odhadnout. Nevíme, zda v Centauru přistoupili i k optimalizacím výpočetních jednotek, frontendu či logiky out-of-order zpracování. Vzhledem k časovému odstupu (Nano bylo odhaleno již v roce 2008), bychom však určité poštelování architektury myslím mohli čekat. Doufejme tedy, že nám VIA příští rok naservíruje zajímavou novinku.

Zdroj: The H