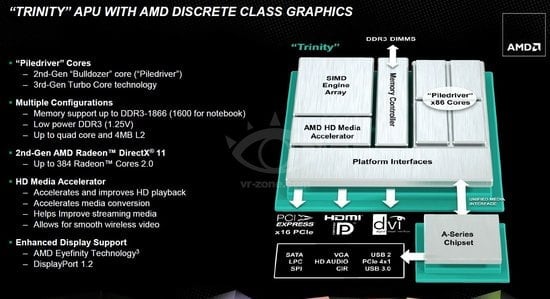

Již delší dobu je známo, že grafické jádro bude vycházet

z architektury VLIW4, známé z Radeonů řady 6900. Nejvyšší model bude

mít 384 stream procesorů v šesti blocích SIMD a 24 texturovacích jednotek.

Nová architektura mimo jiné zvýší výkon v teselaci. Frekvence grafické části se

má pohybovat mezi 424 a 800 MHz, není ovšem uvedeno, zda čísla počítají

s režimem Turbo. Frekvence pamětí, sdílených se zbytkem systému, nakonec

oficiálně nestoupne a zůstane na 1866 MHz. Notebooková verze ale nabídne

oficiálně jen 1600 MHz.

Potvrzuje se také přítomnost hardwarového enkodéru videa.

Byť toto označení v prezentaci nepadlo, pravděpodobně se jedná o jednotku

VCE, přítomnou i v 28nm Radeonech řady 7000. Zlepšení přijde pro

příznivce velkých pracovních ploch, neboť APU má zvládat DisplayPort 1.2.

Zároveň oproti Llanu přibyla podpora Eyefinity, takže bude možné naráz připojit

tři monitory.

Zatímco grafická část nepředstavuje architektonicky nic

nového, jádra CPU přinášejí zbrusu novou architekturu Piledriver. Ta

má oproti architektuře Bulldozer dosahovat lepšího IPC. Zároveň má však omezit

spotřebu energie a navíc umožnit vyšší taktovací frekvence. AMD bohužel neuvádí

žádné hodnoty rozdílu ve výkonu na stejné frekvenci. Dočkáváme se opět jen

srovnání s ne právě bleskurychlými jádry Husky v APU Llano. Oproti

nim prý bude desktopové Trinity o 26 % rychlejší, zatímco notebookové čipy

nabídnou o 29 % zvýšenou „produktivitu“. Slajd s podmínkami, za jakých byla

tato čísla naměřena, bohužel není k dispozici.

Asi nejzajímavější je stránka popisující oblasti,

ve kterých jsou jádra Piledriver přepracována oproti Bulldozeru. Co se týče

přímo exekučních jednotek procesoru, slibuje AMD vyšší výkon při dělení (jak

celočíselném, tak s použitím plovoucí řádové čárky). Rychlejší mají být

také instrukce SYSCALL a SYSRET pro zpracování systémových volání. To by mělo

zajistit rychlejší přepínání úloh a v důsledku lepší odezvu systému.

Většina vylepšení však nastala mimo samotné exekuční

jednotky. Návrh čipu se tak zaměřuje na efektivnější využití již dostupných

zdrojů. Lépe má pracovat vyrovnávací paměť L2 a také přednačítání

z paměti. Procesor by měl účinněji optimalizovat situace, kdy se čte

z adresy, do níž byla předtím zapsána data (tzv. Store-to-Load

Forwarding). V takovém případě je totiž možné rovnou použít hodnotu

z vyrovnávací paměti. V souladu se staršími informacemi byl zvětšen

TLB (Translation Lookaside Buffer) příslušející datové vyrovnávací paměti L1.

Dále se údajně zvedla efektivita schedulerů, které přiřazují instrukce

jednotlivým jednotkám. Vykonávání instrukcí Out-of-Order zároveň pracuje

s větším množstvím instrukcí naráz, takže by mělo dosahovat optimálnějších

výsledků. Vedle toho AMD zapracovalo i na logice pro předpověď výsledků

větvení.

Prezentace uvádí také novou instrukční výbavu jader CPU. Dle

očekávání k existujícímu FMA4 přibylo FMA3, tedy forma kompatibilní

s Haswellem. Nová je podpora výpočtů v pohyblivé řádové čárce

s 16bitovými hodnotami. AMD rovněž mluví o „AVX 1.1.“ Není tak docela

jasné, co tím myslí, teoreticky by mohlo jít například o instrukce

BMI a TBM. Jednotlivá APU by se měla prodávat s frekvencemi od 2 do 3,8

GHz, dost možná však čísla opět nezohledňují Turbo. Co se toho týče,

technologie Turbo Core 3.0 by měla být schopná zvýšit takty grafického jádra i

procesoru a navíc v případě nečinnosti jedné části přidělit její příděl

energie části druhé. Grafika se tedy bude moci přetaktovat na úkor procesoru a

naopak.

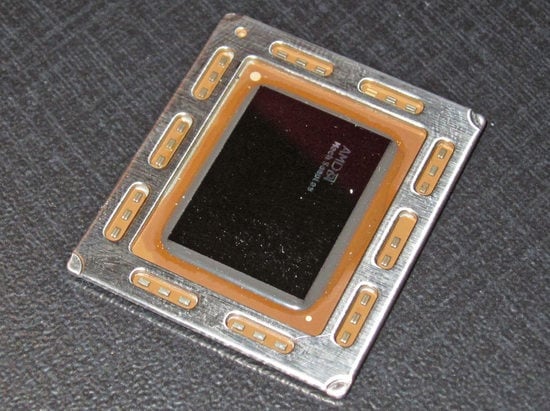

Na konec jsem si nechal několik čísel, o která se AMD rovněž

podělilo. V prezentaci uvádí, že čip Trinity (čtyřjádrová verze) narostl

na 246 mm² (Llano by mělo zabírat 228 mm²). Počet

tranzistorů dosáhl čísla

1 miliarda 303 milionů (Llano jich mělo údajně „kolem

miliardy“). Zdá se tedy, že se čip podařilo oproti předchůdci poněkud zahustit,

neboť výrobní proces zůstává týž – 32 nm na bázi SOI. Hodnoty TDP zůstanou na

desktopu beze změny, zatímco u notebooků zmizí 45W varianta (35W a 25W modely

zůstávají) a místo ní přibude 17W třída pro nejmobilnější notebooky.

Tolik tedy uniklé slajdy. Pokud jsou zprávy o květnovém

vydání pravdivé, měli bychom se již brzo dozvědět víc. Tedy jednak frekvence

prodejních čipů (nějaké spekulativní informace již

máme), ale zejména, jak na tom procesory budou s výkonem.

Zdroj: VR-zone