Výrobní procesy čipů jsou ve vztahu k hardwaru naprosto elementární a zároveň velmi složitou věcí; v posledních letech potíže s jejich evolucí vyvstaly docela silně v oblasti GPU i procesorů. Firma GlobalFoundries do tohoto boje nyní jde s novou zbraní – polovodičovou divizí IBM. S ní se do firmy dostal i bývalý viceprezident IBM Gary Patton, jenž je nyní v GlobalFoundries šéfem výzkumu a technologie (CTO). Na webu Semiconductor Engineering s ním nyní vyšel zajímavý rozhovor, v němž mluvil o technologiích chystaných či zkoušených pro připravované 10, 7 a 5nm procesy, budoucnosti FD-SOI a dalších pokročilých technikách.

Jednou z věcí, které z IBM přišly, by měly být zkušenosti s alternativními materiály, jako je například kombinace křemíku a germania (tzv. „SiGe“), na kterém byly založené i první pokusné 7nm čipy IBM. GlobalFoundries nyní podle Pattona na nových materiálech hodně pracuje, kromě tohoto základu i co se týče dopantů a pomocných materiálů užitých při výrobě. Hledána je také například alternativa mědi coby materiálu pro vodiče.

Gary Patton, CTO GlobalFoundries přicházející z IBM

S 5nm procesem možna FinFET nahradí nanodrátky

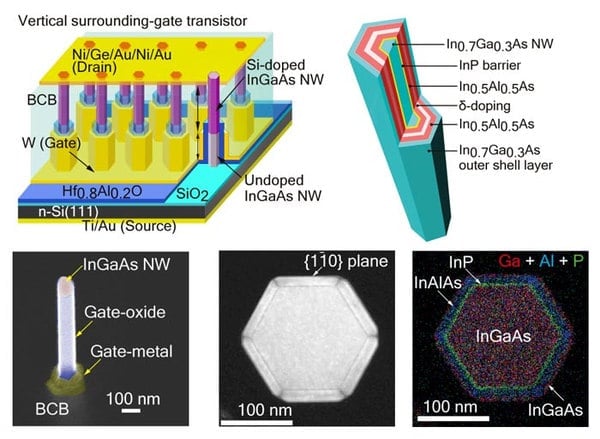

Výzkum běží i ohledně samotné struktury tranzistorů. U té jsme byly svědky přechodu od jednodušších planárních na „3D“ tranzistory FinFET. Poměrně brzy ale možná bude třeba opustit i FinFETy. Podle Pattona GlobalFoundries zkoumá plně vertikální tranzistory a také tzv. nanodrátky. Ty jsou údajně docela vážným kandidátem pro aplikaci na 5nm procesu, tedy v relativně blízkém horizontu (třetí generace po 14nm procesu). O jejich použití nicméně ještě není rozhodnuto, neboť výroba takových struktur je hodně velkou výzvou. Samotný 5nm proces je ale podle Pattona rozhodně realitou, o jeho realizovatelnosti nemá být pochyb.

Struktura vertikálních tranzistorů z nanodrátků (výzkum univerzity v Sapporu)

Sebeskladba

Pomoci s tvarováním struktur na extrémně miniaturní úrovni by mohla také řízená sebeskladba (directed self-assembly), tedy manipulace, díky níž se částice samy poskládají tak, jak je třeba, ideálně s precizností, kterou by se už konvenčním „obráběním“ docílit nepodařilo. Sebeskladbu chtělo pokud si vzpomente využít například i Hitachi pro výrobu diskových ploten, zásadní význam by ale mohla mít hlavně zde pro logické a jiné čipy. I touto „technologií budoucnosti“ se výzkum IBM a nyní GlobalFoundries zabývá a údajně se daří dosahovat jistého pokroku. Problémem je ale, že u takto vytvářených struktur se inženýři potýkají s vysokou kazovostí. Sebeskladba jednoduše na čipu kromě žádoucí práce vytváří i své vlastní chyby.

U čeho prý vůbec není jisté, zda se uplatnění dožijeme, jsou větší 450mm wafery (v současnosti jsou užívány 300mm, na starších provozech 200mm). O jejich nasazení jako možné cestě k zlevnění čipů na extrémně náročných procesích se již mluví řadu let, zdá se ale, že jsou stále odkládány proto, že půjde taktéž o velmi drahou věc. Podle toho, co v rozhovoru padlo, zatím na jejich nasazení konkrétní plán není. Podle Pattona není zřejmé, zda někdy vůbec přijde čas, kdy se vyplatí.

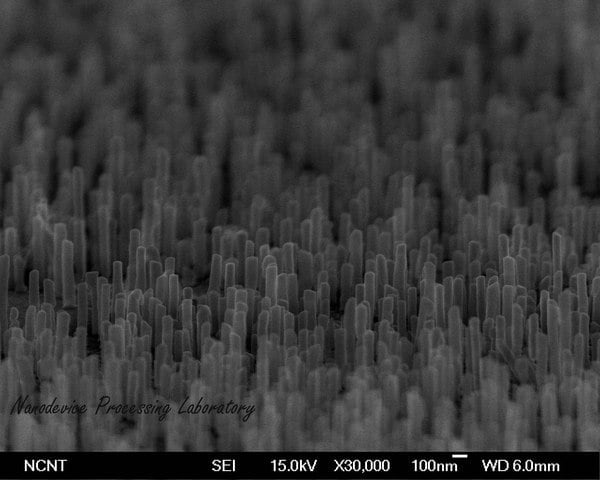

Nanodrátky na mikrofotografii

EUV: na 5nm

Vedle 450mm waferů se již dlouho mluví i o expozici extrémním ultrafialovým zářením, tzv. EUV. To je také permanentě „na dohled“, nicméně podle Pattona v jeho případě skutečně dochází k pokroku a začíná to vypadat, že EUV bude přes opakované zpoždění eventuálně využitelné. Pravděpodobně ale přijde až po 7nm procesu, tedy nejdříve s 5 nm. Jeho aplikací se ale hodně usnadní problémy s expozicí, mělo by poněkud zmírnit čím dál vyšší počty masek a osvitových fází, které jsou se zmenšováním rozměrů potřebné.

Podle Pattona se daří řešit primární problém, který EUV lasery měly – totiž jejich výkon. Ten stoupá a už to vypadá, že nakonec dosáhne potřebných parametrů pro to, aby s ním bylo možné zpracovat dostatečný objem waferů za jednotku času. Nyní již je prý větší otázkou problém sekundární, a to jejich spolehlivost. Bude třeba zajistit, aby měly dostatečně vysokou životnost a nízkou poruchovost, aby linky dokázaly běžet s minimálním podílem výpadků.

10nm na FD-SOI

Velmi zajímavá zpráva je, že GlobalFoundries hodlá dále rozvinout svůj program procesů s wafery FD-SOI, na nichž byl letos oznámen „22nm“ postup 22FDX. Ten sice nebude mít 14nm pokračovatele, jako další krok se ale prý rýsuje rovnou 10nm FD-SOI proces. Ten ale opět nebude hlavním 10nm postupem relevantním pro výkonné čipy, nýbrž alternativou pro specifická použití. Zajímavé je, že nebude založen na FinFETech ale na planárních tranzistorech. Kromě ceny i proto, že 3D tranzistory znemožňují použití některých důležitých technik, které zákazníci s FD-SOI využívají (back body biasing).

Planární povaha by také snad opět mohla vést k tomu, že bude proces levnější než FinFETy. Zřejmě však již bude na rozdíl od 22FDX vyžadovat vícenásobnou expozici, takže ke zvýšení nákladů dojde. 14nm varianta byla údajně přeskočena i z tohoto důvodu: ještě by nepřinášela takový pokrok, aby vykompenzovala nutnost vícenásobné expozice. 10nm postup bude ale asi uveden až za poměrně dlouhou dobu, neboť u 22nm se plánuje dlouhá životnost a start výroby teprve napřesrok.

V rozhovoru padla ještě jedna důležitá věc: všechny možné techniky mají pro svou eventuální využitelnost více kritérií. Nejde jen o to, dokázat vyrobit rychlejší a Menší obvody/tranzistory než na předchozím kroku. Nový proces musí nabízet hodnotu navíc proti starším, nesmí tedy být neúměrně drahý. Všechny tyto zázračné techniky tedy budou moci přiložit pomyslnou ruku k dílu jen tehdy, pokud se je podaří implementovat v masovém měřítku dostatečně levně. Některé z těchto zázraků tak nakonec mohou ostrouhat.

GlobalFoundries, cleanroom továrny Fab 1 (Zdroj: PC Games Hardware)

Zdroj: Semiconductor Engineering