Změny budou v samých jádrech

(o tom za chvíli), ale také v infrastruktuře okolo.

Power9 bude nadále stavěn jako highendový, „big iron“ čip

s robustním IO a bufferovanými pamětmi (pro což používá

čipy nazvané Centaur), tuto verzi IBM nazývá „scale-up“

a bude optimalizována pro vícesocketové systémy. Ovšem

zároveň poprvé přijde zjednodušená verze („scale-out“),

která bude mít jednodušší platformu i fyzické provedení

procesorů, bude podporovat přímé připojení pamětí DDR4 bez

drahých a komplikovaných bufferů. IBM doufá, že tato verze

bude moci konkurovat Intelu v segmentu serverů, kde jsou

největší prodeje – v jedno až dvousocketových

strojích, kde kralují Xeony E5-2600.

Tento rozdíl bude ovlivňovat

maximální velikost paměti. Paměťový řadič by měl být

osmikanálový. Bez bufferů má poskytovat propustnost 120 GB/s

a maximální kapacitu až 4 TB (což by však potřebovalo

256GB moduly, takže realisticky například s 64GB moduly bude

použitelná jen kapacita 1 TB). Varianta scale-up s Centaury

umožňuje na každý čip připojit čtyři moduly a celková

kapacita RAM v plné palbě s 256GB moduly může být až

8 TB (2 TB s 64GB moduly). Propustnost má pak údajně

být až 230 GB/s, navíc tato verze přináší RAS funkce navíc

jako deaktivaci čipu na modulu. Centaury také obsahují L4 cache,

kterou zřejmě čipy scale-out oželí.

Jak pro scale-out, tak pro scale-up verzi budou existovat varianty 12jádro SMT8 a 24jádro SMT4

Jádro Power9 ve dvou podobách

Architektonicky po stránce

procesorových jader budou ovšem oba typy stavět na tom samém.

Jádro Power9 bude proti Power8 zvláštní v jednom ohledu –

IBM doposud u čipů stavělo na osmicestném SMT (tedy jeden

čip zpracovává až osm vláken, přičemž škálující

vícevláknový výkon je pak celkově i více než dvojnásobný

proti situaci, kdy je zatíženo vlákno jediné). Generace Power9 to

ovšem zkomplikuje tím, že vytvoří dvě varianty jádra –

se čtyřcestným (SMT4) a osmicestným režimem (SMT8). Čipy

na bázi SMT8 budou nativně dvanáctijádrové, zatímco SMT4 budou

mít jader 24 (počty platí jak pro scale-out, tak pro scale-up

CPU), celkově tedy v obou případech bude k dispozici

stejný počet vláken.

Takto by mělo vypadat 24jádro Power9 typu SMT4

Jádra SMT4 a SMT8 však budou

značně odlišná, nepůjde prostě jen o schopnost přijmout

vlákna navíc. Jádro Power9 má IBM postaveno z opakujících

se základních bloků, tzv. „slice“, v nichž jsou spojeny

výpočetní jednotky (ALU, FPU a SIMD). Zdvojením těchto

bloků vzniká „128bitová super-slice“. A samotné

procesorové jádro je pak skládáno z těchto super-slice,

které tvoří fyzický stavební blok a inženýři je poté

mohou jednoduše replikovat. Vtip je v tom, že jádro SMT4

používá těchto super-slice dvojici, kdežto SMT8 čtveřici,

samozřejmě s frontendem, mezipamětmi, registry a tak

podobně.

Jádro je replikováno z fyzickyých bloků, SMT8 je tvořeno dvojnásobkem jednotek proti SMT4

Tím se tedy vysvětluje, proč má

verze SMT8 jen polovinu jader. Je ve skutečnosti vybavena stejným

množstvím výpočetních prostředků jako 24jádro typu SMT4, jen

je má rozděleny na větší podskupiny a jádra jsou tím

dvojnásobně široká. Jde o docela zajímavý přístup

k návrhu, kdy IBM z jedné architektury udělalo dvě, což

ale ve skutečnosti muselo být podstatně těžší, než to vypadá,

neboť měnit „šířku“ procesorového jádra normálně nelze

bez výrazného přepracovávání. Uvidíme, jak velkou svobodu

budou mít vlákna v přístupu k jednotkám v různých

slice a do jaké míry je omezena komunikace mezi nimi.

Podle IBM jsou tyto dva druhy jader

vhodné pro různé účely – některé aplikace budou

preferovat více vláken, mělo by jít například hypervizory

PowerVM od IBM, kdežto SMT4 bude údajně šikovnější pro stroje

běžící na Linuxu (tedy například ony levnější masové

servery s čipy scale-out, i u scale-out ale bude

existovat SMT8 verze). Je možné, že verze SMT8 by díky menšímu

„oficiálnímu počtu jader“ mohla být výhodná pro aplikace,

kde se platí licence za jádro, pokud tedy licencování

nezohledňuje počet vláken.

Co se týče počtu jednotek, jádro

SMT4 by mělo mít 4 ALU a 4 FPU, dvě permutační

jednotky, dvě děličky a po jedné jednotce pro kryptografii

a decimální aritmetiku (což je funkce zejména pro finanční

aplikace). Power9 také obsahuje podporu pro 128bitové výpočty jak

s fixní (dvě operace za takt), tak plovoucí řádovou čárkou

(jedna operace za takt). Jde o součást instrukční sady Power

3.0, kterou CPU jako první implementuje, a má odpovídat

standardu IEEE 754. Jádro má čtyři jednotky load/store, šest

dekodérů, fetch má šířku 8 operací za takt a frontend

umí zpracovat jedno větvení za takt.

Schéma pro jádro SMT4 (Hot Chips 28, Zdroj: The Next Platform)

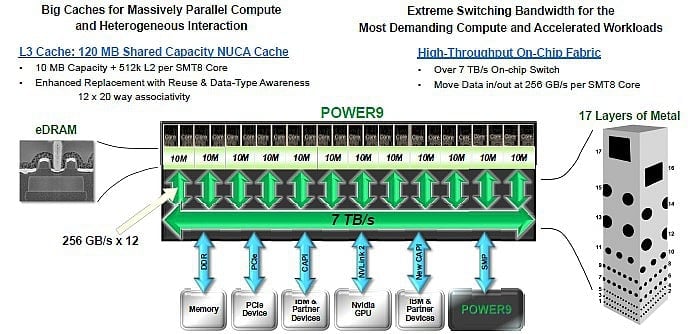

120 MB L3 cache

Paměti L1 cache mají 32 + 32 KB

(obojí osmicestně asociativní), L2 pak 512 KB a obě jsou

vyhrazené pro jedno jádro. L3 cache má u 24jádra celkem 120

MB tvořenou z eDRAM, je však tvořena z 10MB bloků,

které vždy sdílí dvojice jader a které jsou napojeny

(s propustností 256 GB/s) na interní propojovací logiku. Na

ní jsou pak připojené také paměti a další periférie.

24jádro Power9 typu SMT4, schéma

Čip

má řadič PCI Express 4.0 ×48, který také podporují koherentní

připojení CAPI 2.0 pro různé speciální akcelerátory dalších

výrobců, obvykle založené na FPGA. Dále je přítomná

konektivita Bluelink (25 Gb/s × 48), která slouží

k implementaci rozhraní NVLink 2.0 pro připojení GPU Nvidia,

nebo k propojení až šestnáctisocketových serverů

s scale-up čipy. Do čtyř socketů toto není třeba, stačí

primární 16Gb/s koherentní rozhraní SMP.

IBM Power9 (Hot Chips 28, Zdroj: The Next Platform)

O 50–125 % rychlejší než

Power8 při stejném taktu

Takty a výkon v tuto chvíli

ještě nejsou odhaleny, neboť čipy mají být dostupné až

v letech 2017 (to platí pro levnější scale-out variantu)

a 2018 (ona highendovější verze scale-up). IBM ve svých

slajdech srovnává čip Power8 s 12 jádry s rovněž

dvanáctijádrem Power9 s architekturou SMT8. Oba čipy mají

tedy stejný počet vláken, přičemž Power9 má dosahovat výkon

o 50–125 % vyšší. Obojí je při taktu 4,0 GHz, takže

finální frekvence Power9 by se zřejmě měly pohybovat nad touto

hodnotou.

Výkon 12jader Power8 a Power9 SMT8 na 4,0 GHz, dle IBM (Hot Chips 28, Zdroj: The Next Platform)

Nicméně mějme na paměti, že

dvanáctijádro SMT8 je do jisté míry převlečené 24jádro SMT4,

takže je otázka, do jaké míry zde srovnáváme stejné druhy

ovoce. Čip bude rozhodně velmi komplexní, a to asi i ve

scale-out verzi. IBM ještě neuvedlo nic o rozměru ani počtu

tranzistorů, při výrobě je ale ale údajně použito celých 17

vrstev kovových spojů. K výrobě je použit proces

GlobalFOundries označený 14HP. Ten by měl být velmi odlišný od

procesu 14LPP, použitého pro GPU a CPU AMD, neboť byl vyvíjen

ještě samostatnou polovodičovou divizí IBM, než ji

GlobalFoundries koupili. Je podle všeho orientován na vysoký

výkon, cenou ovšem může být horší spotřeba a zřejmě

také bude dražší.

Výrobní náklady těchto čipů –

jež nezapřou svůj „big iron“ původ – asi obecně budou

horší než u relativně málo komplexních Xeonů E5. To bude

v této konfrontaci výhoda pro Intel, který by příští rok

měl v tomto segmentu uvést procesory platformy Purley založené

na architektuře Skylake (serverová verze s AVX-512). Ovšem

také pro AMD, jež chystá serverový

MCM SoC na bázi Zenu s až 32 jádry a 8 paměťovými

kanály, a IBM bude zřejmě muset soupeřit zároveň

s oběma.

Zdroj: The

Next Platform