Tento týden probíhala v Americe – ovšem pouze virtuálně – konference HotChips 32. Už jsme z velmi zajímavého dění na této akci informovali o odhalení procesorů IBM Power10 a o prezentaci GPU architektury AMD RDNA 2. Ovšem novinky odhaloval také Intel, který poprvé promluvil o tom, jak budou vypadat 10nm Xeony Ice Lake, který přijdou na trh nyní na podzim.

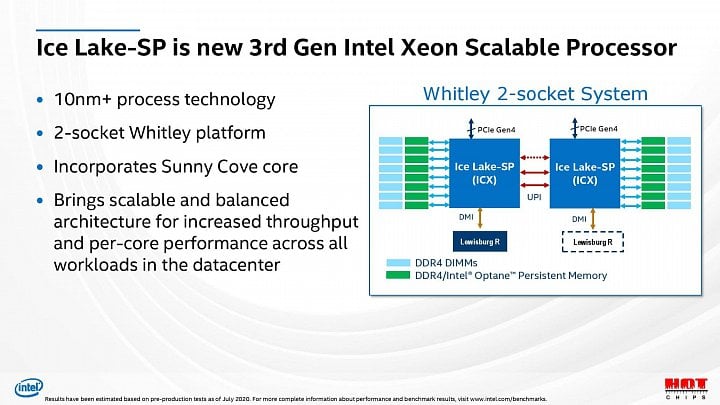

Xeony Ice Lake-SP (zkráceně také ICX) budou uvedené v 2S (až dvousocketové) platformě Whitley pro socket LGA 4189. Procesory jsou založené na architektuře Sunny Cove, kterou Intel uvedl na trh před rokem, nicméně verze v Xeonech je odlišná, podobně jako se liší Skylake a Skylake-SP. Podrobnosti o serverové verzi dosud nebyly známé, takže HotChips přináší vítané novinky.

Serverové jádro Sunny Cove přichází

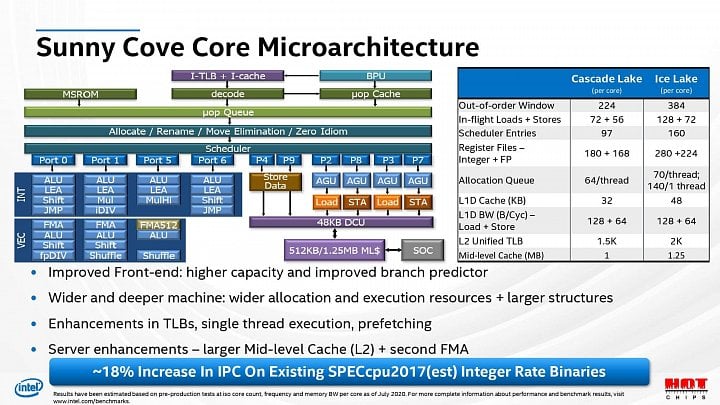

Intel publikoval schéma architektury, které můžete vidět na slajdu. Základní architektura je stejná jako u Ice Lake pro notebooky: výpočetní jednotky jsou rozdělené do deseti portů, procesor má čtyři ALU a čtyři AGU, floating point a SIMD instrukce jsou na třech portech sdílených s celočíselnými ALU. Nezměnily se ani hloubky out-of-order front (Intel sice uvádí vyšší out-of-order window čili reorder bufferu 384 operací, ale to je prý překlep, ve skutečnosti je to pořád 352).

V tomto základním schématu Intel nic neměnil a jádro je tedy velmi podobné až na dvě věci. Jednak je to větší L2 cache, podobně jako u také čerstvě představeného Tiger Lake. Klientská verze Ice Lake (respektive Sunny Cove) obsahuje 512KB L2 cache, ale zde Intel přidal dalších 768 KB a jádra tak mají k dispozici 1,25MB L2 cache. Bohužel neznáme latence, je možné, že o něco stouply. Asociativita by asi mohla být 20-way.

AVX-512 dvojnásobně rychlé

Druhá změna je zásadní: vyšší výkon ve vektorových výpočtech. Stejně jako Skylake-SP proti Skylake má serverové jádro Sunny Cove navíc dedikovanou 512bitovou FMA pro instrukce AVX-512. Běžné jádro je už také podporuje, ale používá pro ně výhradně spojení dvou 256bitových jednotek určených pro AVX/AVX2 na portu 0 a 1. To logicky může přinést jen omezené zrychlení proti 256bitovým vektorům.

Serverové Sunny Cove používá toto a navíc má samostatnou 512bitovou jednotku na portu 5. Díky tomu dokáže v AVX-512 dosáhnout dvojnásobného hrubého výkonu proti 256bitovým operacím AVX/AVX2.

Nové instrukce zvyšující výkon

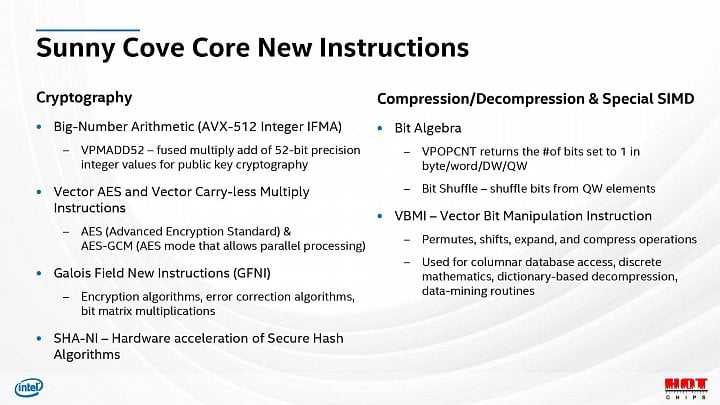

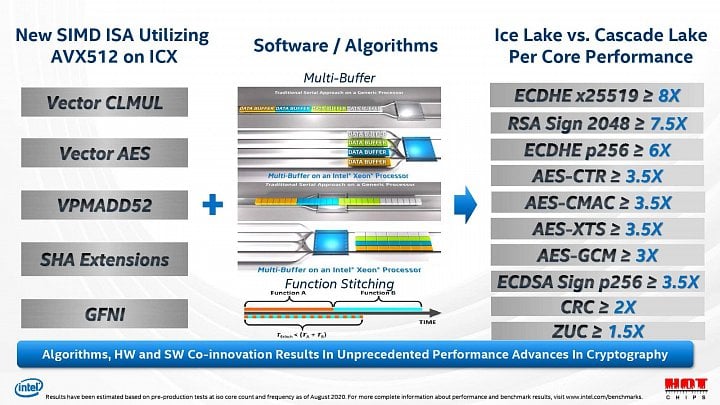

Kromě toho také jádro přidává v rámci množiny instrukcí AVX-512 nová rozšíření pro vektorové výpočty CLMUL a AES, vektorové BMI, vektorové POPCNT, VPMADD52, akceleraci SHA a instrukce pro algoritmy Galois Fields.

Tyto instrukce mají zvýšit výkon v různých kryptografických operacích 1,5× až 8× (modelová zrychlení pro různé algoritmy můžete vidět na slajdu). Programátoři optimalizující různý kritický kód v assembleru by tedy mohli Ice Lake-SP mít docela rádi.

AVX-512 teď přinese mnohem konzistentnější nárůst výkonu

Slabinou AVX-512 bylo u 14nm procesorů, že aktivace těchto instrukcí jednak snižuje takt, takže výkonnostní přínos nemůže být 2× (a programátor musí dávat pozor, aby optimalizace nebyla neúčinná kvůli tomu, že sice zvýší IPC kódu, ale zhorší takt CPU).

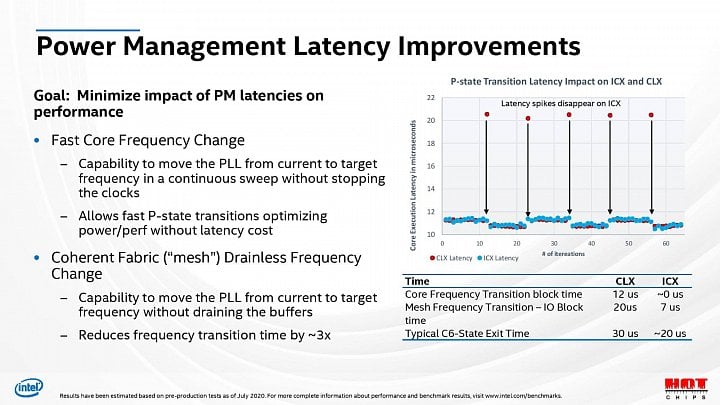

Současně jsou ale problematické také přechody mezi těmito stavy, protože se během nich CPU chová specificky, výrazně se při nich zhoršuje latence a je to dost komplikované (viz tento článek). Naštěstí by v tomto Ice Lake-SP mělo být o hodně lepší a sklízet ovoce AVX-512 bude snazší.

Přepínání mezi výkonnostními stavy (a mezi P a C stavy), tedy jako například mezi aktivitou AVX-512 a pouze AVX nebo SSE má mít na Ice Lake až 3× kratší latenci proti předchozím Xeonům Cascade Lake – tyto přechodové stavy stojí nějaký výkon, takže zlepšení zde CPU zrychlí. Měly by také zmizet přechodné nárůsty latence v těchto okamžicích.

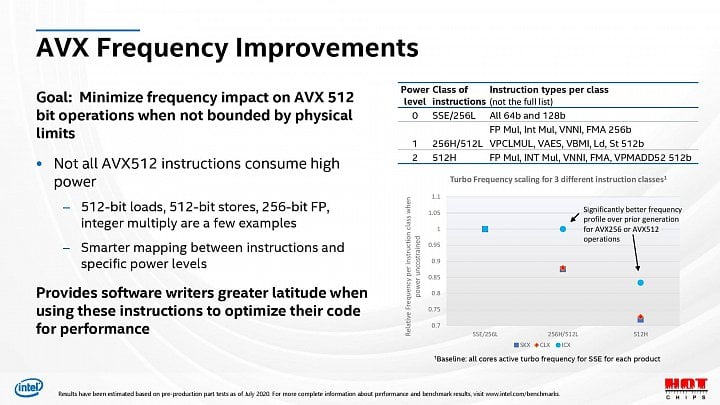

Výrazně eliminovány propady frekvencí kvůli 512bitovému SIMD

A současně nebude díky 10nm procesu už cena AVX-512 ve spotřebě tak vysoká, takže CPU nebude muset tolik snižovat takty, což přinese výrazné výkonnostní zlepšení. Na následujícím slajdu můžete vidět relativní frekvence Ice Lake (světle modré tečky), Skylake-SP (tmavě modré čtverečky) a Cascade Lake (červené kosočtverečky) při různých SIMD operacích.

SIMD operace mají různou náročnost, Intel je rozděluje do třech skupin. V první nejméně náročné jsou 128bitové instrukce SSE a některé méně náročné 256bitové operace AVX. Poté jsou v druhé skupině „těžší“ instrukce AVX2 a méně náročné 512bitové AVX-512. Nejhorší třetí skupina s nejvyšší spotřebou (nebo také třeba náročností na napětí) pak obsahuj těžké operace AVX-512 jako vektorové násobení, FMA. V Ice Lake se jinak řada operací přesunula z těžších skupin do lehčích proti Skylake/Cscade Lake.

U 14nm procesorů už druhá skupina vedla k poměrně výraznému snížení frekvencí a třetí kategorie pak znamenala ještě horší posun frekvencí dolů. U Ice Lake Intel uvádí, že se mu podařilo snížit náročnost druhé skupiny tak, že by v praxi obvykle měla běžet na stejných frekvencích jako ta první. Operace AVX a AVX2 by tedy už nemusely téměř vůbec shazovat frekvence. To by se mělo dít teď už jen u těžkého subsetu AVX-512. I u něj ale bude dopad zmírněn. Podle grafu by měla frekvence být snížena o něco více, než co dřív způsobovaly lehké AVX-512, ale ztráta bude o dost nižší, než pro těžké AVX-512 na 14nm čipu.

Díky těmto dvěma vylepšením by nyní mělo být výrazně snazší dostat z kódu používajícího AVX-512 výkonnostní zlepšení. AVX-512 je výhoda procesorů Intel proti konkurenčnímu AMD, které používá jen 256bitové SIMD. Při ideální optimalizaci může Intel výrazně zvýšit výkon na jedno jádro a kompenzovat náskok AMD v počtu jader.

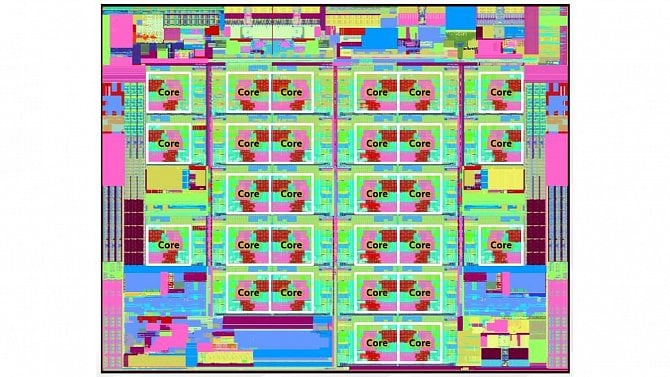

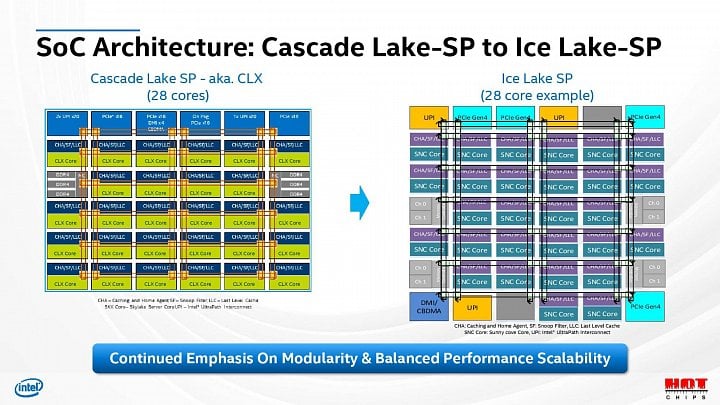

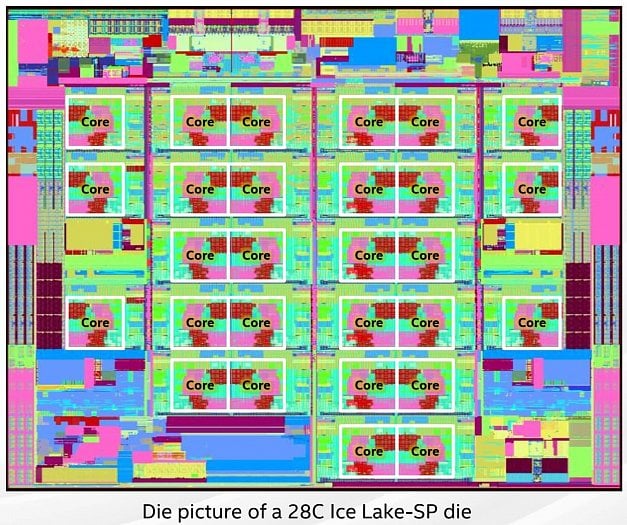

Zatím ukázáno jen 28jádro, schéma propojení a čipu

Intel zatím prezentuje 28jádrovou verzi Ice Lake (je uvedeno, že jde o příklad). Zda bude existovat i vyšší, prozatím nepotvrdil. Procesor používá stejně jako Skylake-SP a Cascade Lake-SP propojení mesh, takže jsou jádra jako na šachovnici spolu s dalšími bloky. Proti 14nm 28jádru má ale Ice Lake-SP více „polí“, mesh má místo 6×6 teď 6×7 polí.

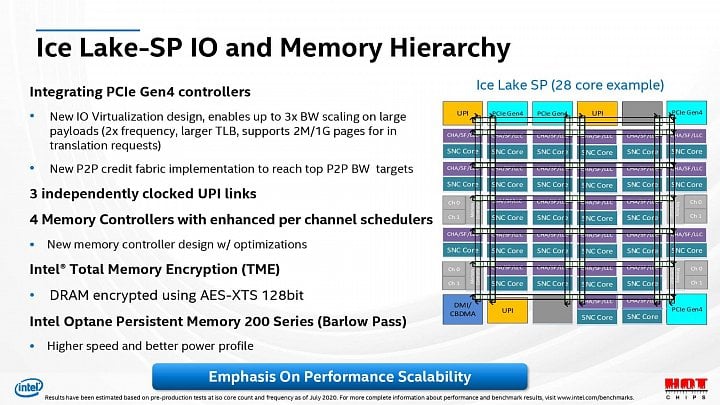

Jádra a I/O bloky jsou jak můžete vidět nyní rozhozena poněkud méně pravidelně, více je jich použito pro I/O (tři linky UPI, PCI Express) a také pro řadiče pamětí. Zatímco v Skylake vykusovaly řadiče pamětí dvě pole (každé se třemi kanály DDR4), u Ice Lake jsou to čtyři pole, kde v každém je dvoukanálový řadič DDR4. Řadič PCI Expresu už podporuje PCIe 4.0 (jako AMD Epyc 7002), přičemž by nad mohl mít 64 linek.

Ice Lake-SP má tedy opravdu osmikanálový řadič pamětí DDR4, jenž by měl podporovat DDR4-3200 a také paměti Optane DC Persistent Memory generace Barlow Pass na 3200 MHz (14nm CPU umí jen 2666 MHz).

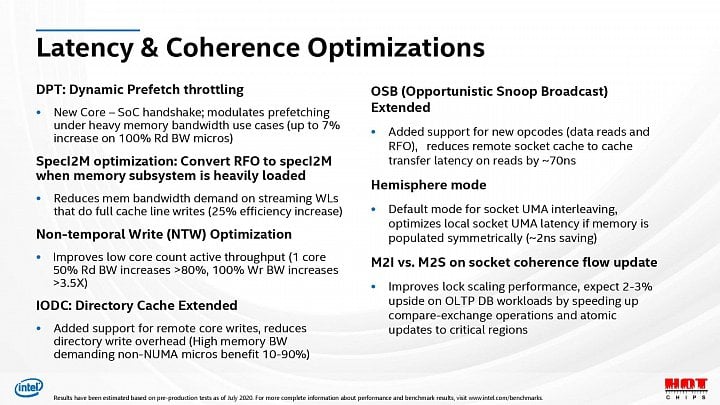

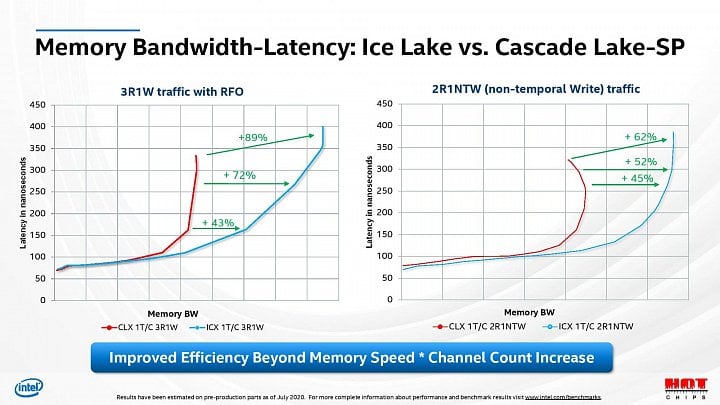

Řadič mimochodem také podporuje AES-XTS šifrování RAM Total Memory Encryption (TME). Procesor má i mimo to mít nějaká architektonická zlepšení řadiče pamětí, prefetche a koherence, vylepšující efektivní propustnost a latenci v serverových úlohách.

Ice Lake-SP má ještě starý 10nm proces, ne SuperFin

Zatím Intel nesdělil nic k parametrům jednotlivých modelů, takže počty jader a frekvence nebo TDP jsou stále otázka. Toto se dozvíme až když se vydání přiblíží (pokud nenastanou nějaké informační úniky). Vydání má nastat do konce roku.

Ice Lake by mělo přinášet více výkonu s lepší energetickou efektivitou, což nyní Intel proti Epycu (a případně asi i ARM konkurentům jako je Graviton2) potřebuje. Nicméně určitou slabinou Ice Lake-SP je, že je ještě postavené na stejné verzi 10nm procesu (oficiálně první, neoficiálně druhé, pokud počítáme Cannon Lake, k němuž se Intel moc nehlásí). Serverové Ice Lake ale ještě nemá zdokonalený (možná by se dalo říci opravený) proces 10nm SuperFin, takže patrně bude trpět na relativně nízké frekvence a možná i zhoršenou energetickou efektivitu proti jádrům Tiger Lake s procesem 10SF.

Tip: 10nm proces Intelu zpět ve hře. Technologie SuperFin masivně zlepší takty, problémy pryč?

Běžně by od serverové verze snad měly být odvozené i nové highendové procesory nahrazující současné Core i9 „Cascade Lake“ na platformě X299. Ovšem právě kvůli předchozímu je nejisté, zda Intel nějakou verzi Ice Lake-X pro highednový desktop a pracovní stanice vyrobí. Pokud takty nebudou dost vysoké, mohl by Intel Ice Lake přeskočit a počkat až na Sapphire Rapids.

Galerie: Prezentace architektury 10nm procesorů Intel Xeon Ice Lake SP na HotChips 32

Zdroje: AnandTech, Tom's Hardware